1、信號串擾

串擾指的是在兩條信號線之間的耦合現象。信號因為空間距離近的原因導致的信號線之間會出現不希望看到的電感性和電容性耦合從而互相干擾。電容性耦合會引發耦合電流,而電感性耦合則引發耦合電壓。在電路設計中,是一個比較棘手的問題。

2、本文概要

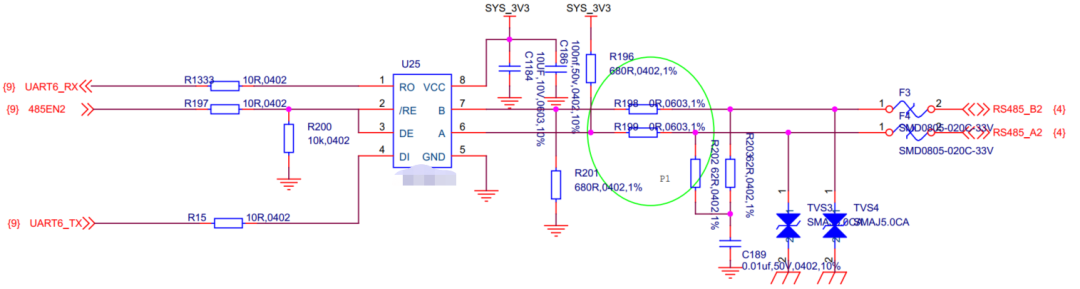

本文要解決的是RS485發送端波形噪聲干擾大的問題,如下圖1所示是其原理圖,RS485的發送,接收,使能控制引腳通過一個10R電阻分別直接連接到MCU端口上。這個電路是目前市面上比較常用的RS485方案,具體的實現方式如下:

在空閑期間,485EN為低電平,MCU處于接收狀態;在準備發送數據之前,MCU會先拉高485EN,U25處于發送狀態;發送完畢之后,485EN重新處于低電平,U25處于接收狀態。此方案的關鍵是要掌握好控制485EN引腳的高低的時機,否則會有丟包問題。

圖 1RS485 典型應用原理圖

3、問題發現及解決過程

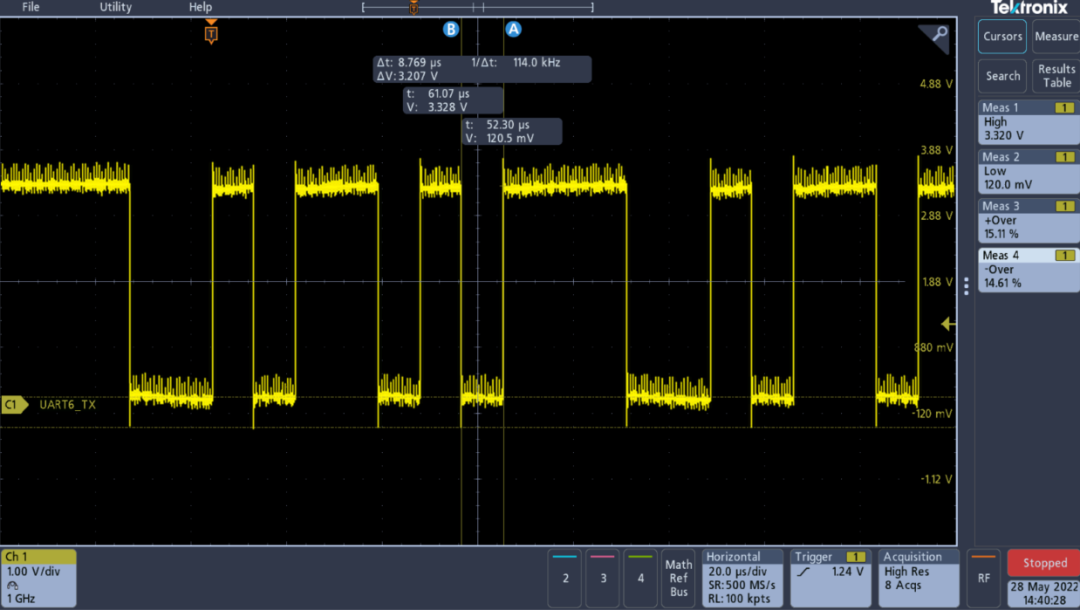

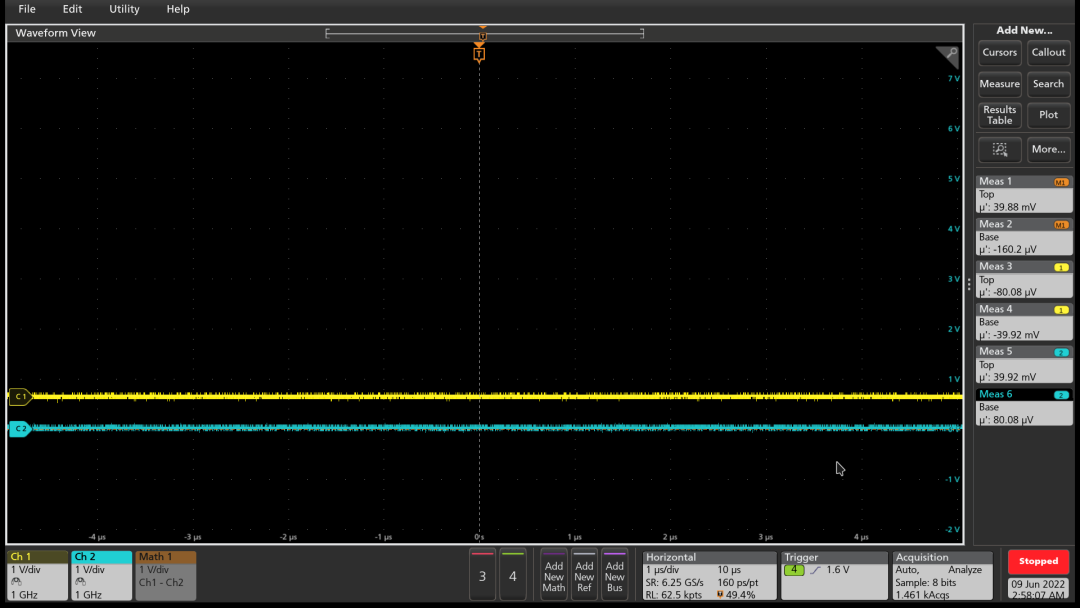

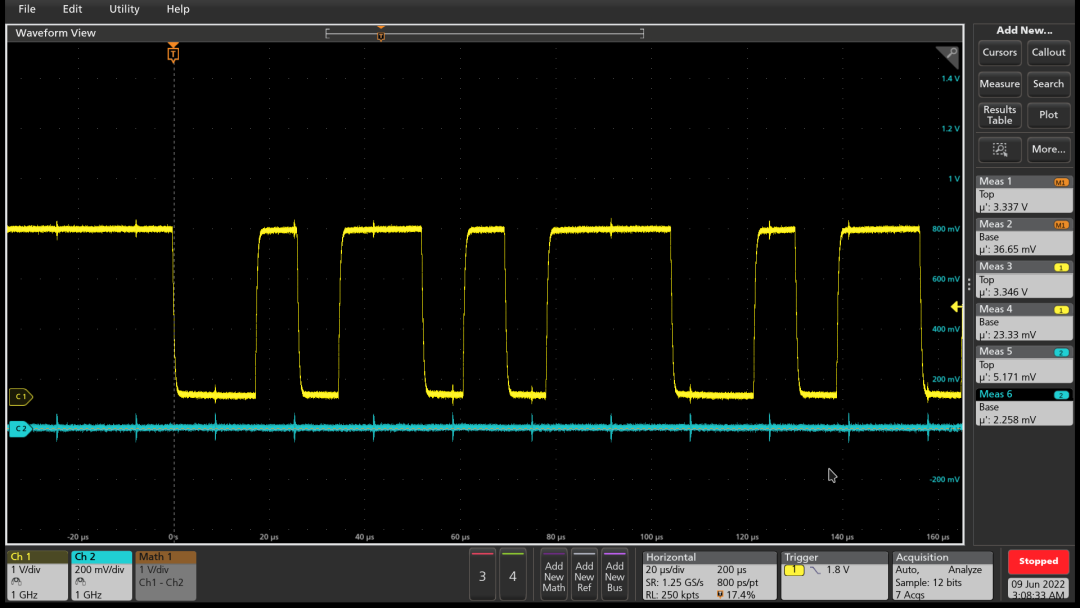

硬件測試時發現發射端DI的波形如下圖2所示,在信號上有很大的毛刺(電阻R15前后都一樣),測量另外一路同樣的RS485電路就不會有這種問題,分析電路原理上是不會有問題的,懷疑是這路信號被其他信號干擾了。

圖 2RS485發射引腳DI(UART6_TX)的波形圖

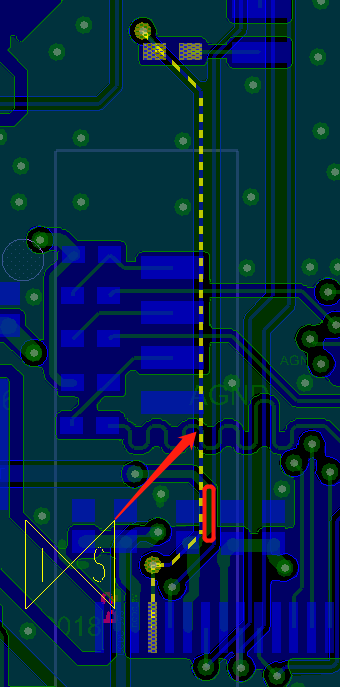

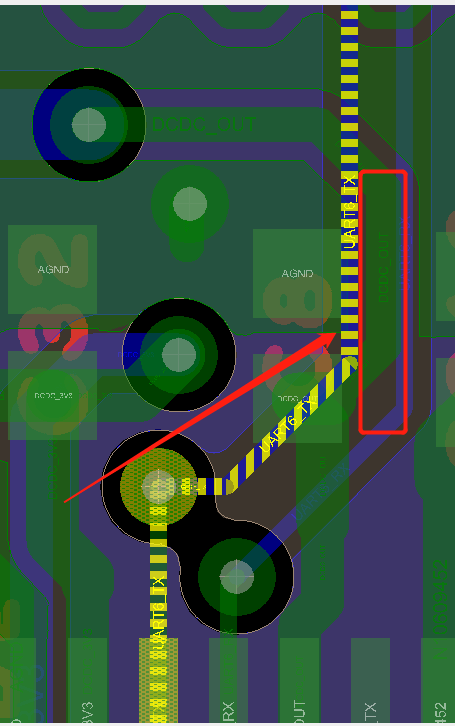

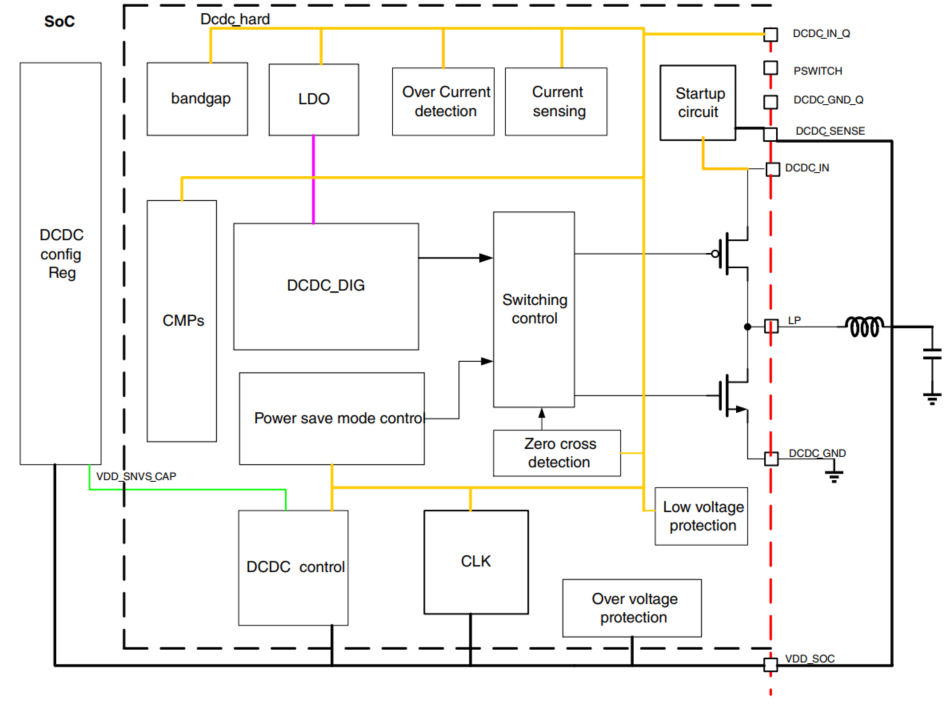

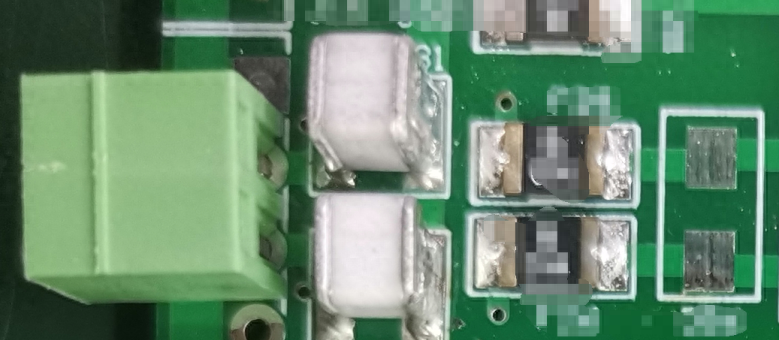

打開PCB圖,找到UART6_TX這根線對應的PCB走線圖,如下圖3、圖4所示。我們可以看到這根線從MCU出來后通過過孔到第三層,然后徑直往上,在上面通過過孔回到第一層,然后通過R15電阻接入RS485芯片的DI引腳,整個路徑除了和第一層的DCDC_OUT這根線有一段短距離的平行布線之外,其余還算干凈。查看DCDC_OUT信號,發現DCDC_OUT是MCU的內核電壓,系統選用的MCU內部含有PMU單元,內部DCDC單元是其中的一部分,其框圖如下圖5所示。考慮到buck芯片的強干擾影響,猜測是內核DCDC輸出布線對UART6_TX造成的耦合干擾。

圖 3UART6_TX走線路徑圖

圖 4UART6_TX與DCDC_OUT平行走線部分

圖 5 DCDC block diagram

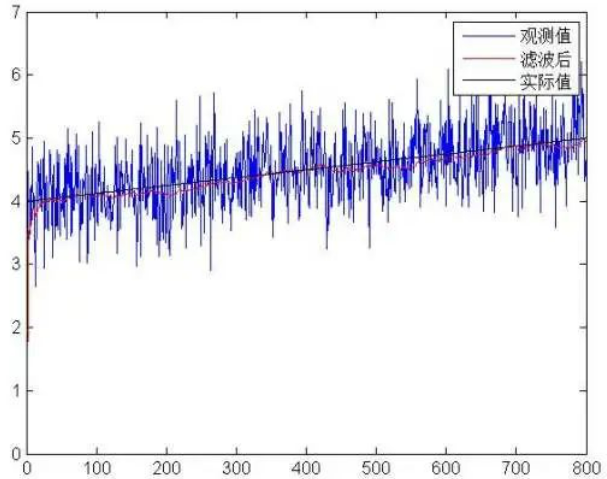

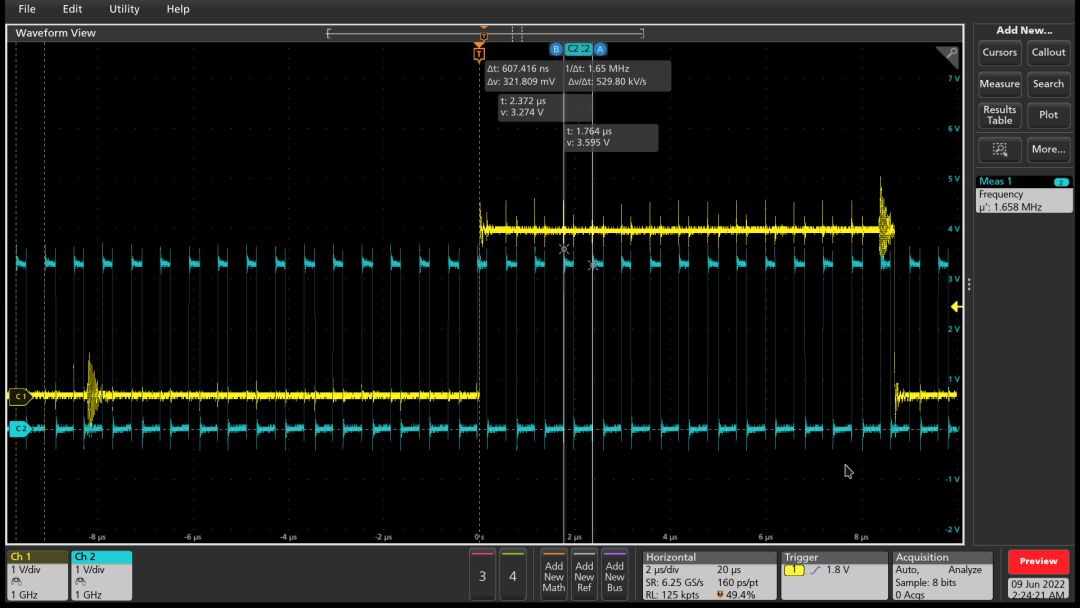

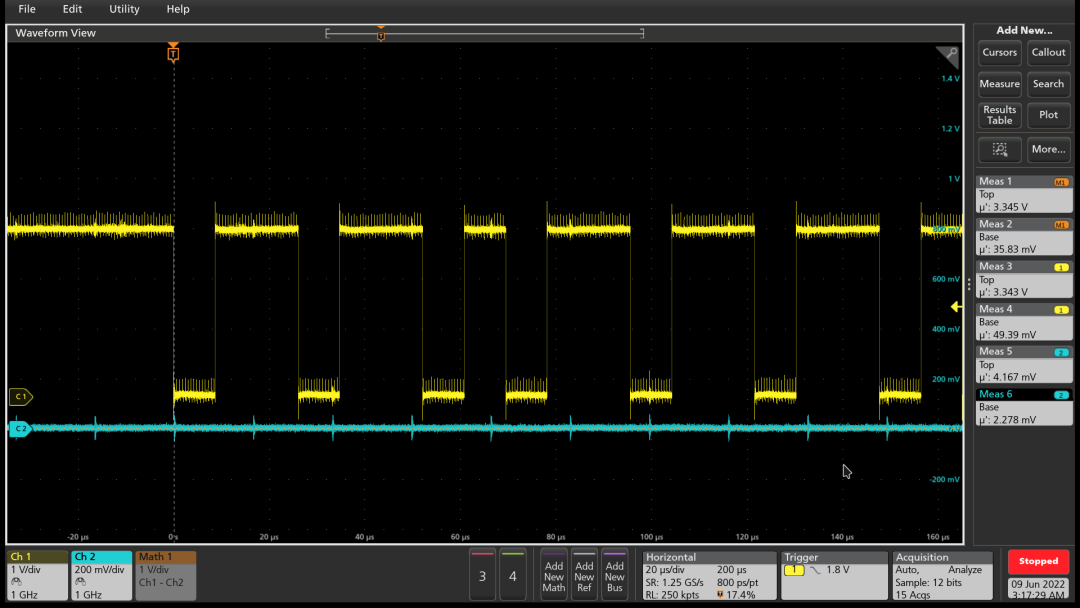

同時監測RS485發送引腳波形DI與LP點(圖5框圖中電感前)的電壓波形,如下圖6所示,可以發現,干擾的頻率與LP處頻率基本一致,基本可以判斷是芯片內核電源buck芯片的平行輸出布線耦合到RS485 DI引腳上去的。

注:黃色代表RS485上波形、LP處波形

圖 6 發送端DI與LP處波形

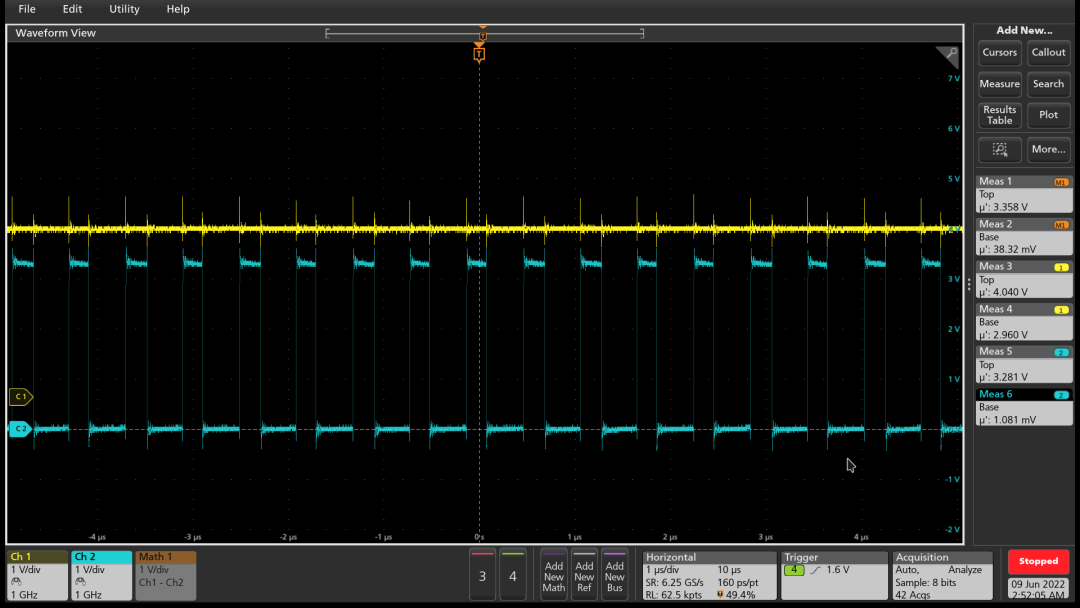

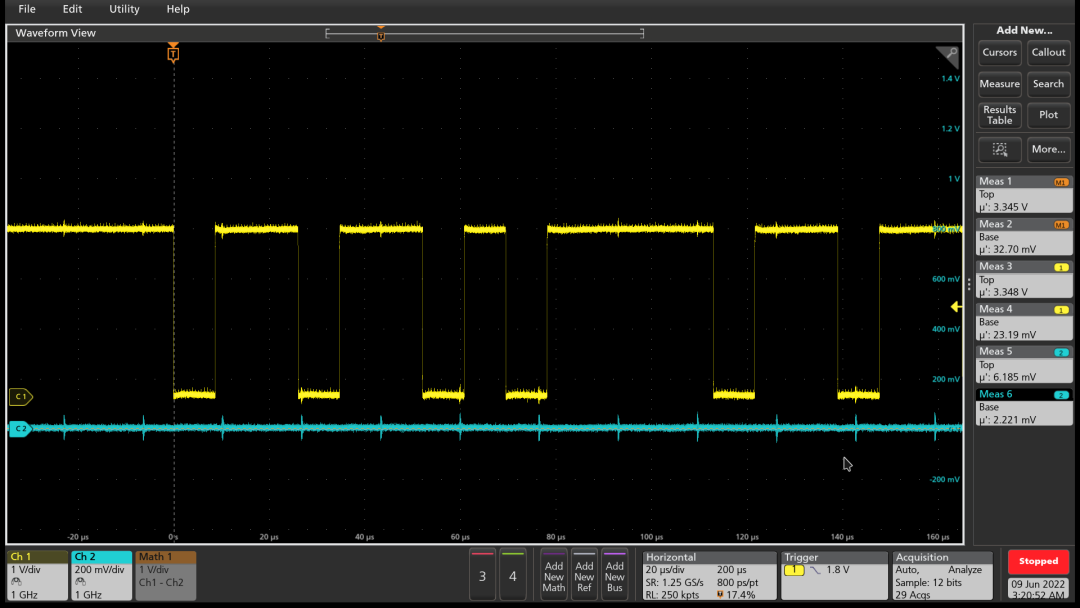

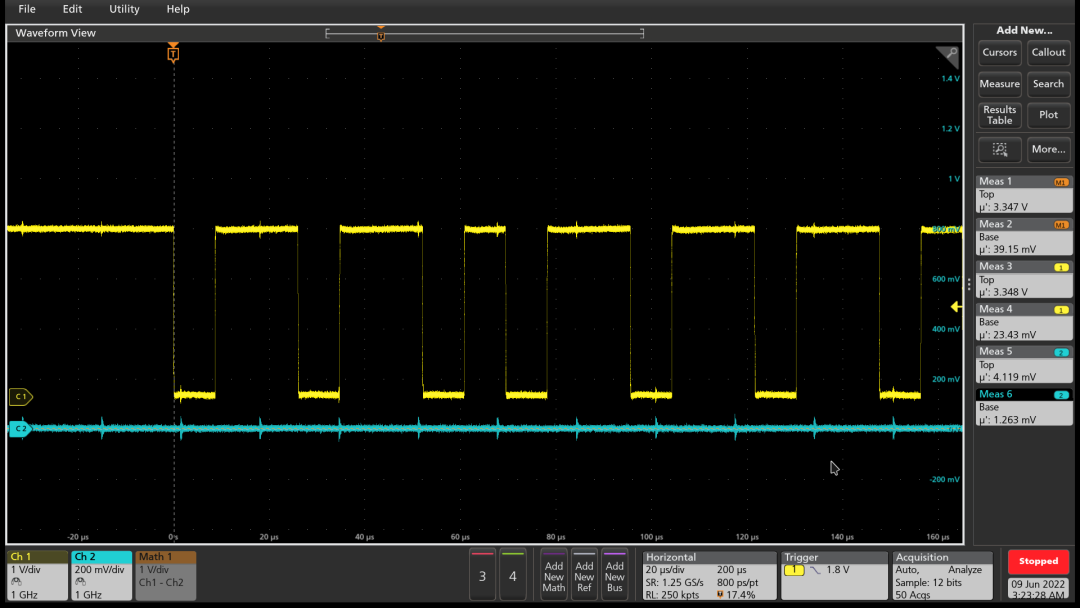

那有人說了,這樣判斷是不是有點草率了?有沒有可能是RS485芯片部分的接收到其他地方的干擾傳導前面發射端的呢?好的,那我們再來驗證一下:我們先把R15電阻斷開,然后觀測靠近MCU端的波形和LP點輸出電壓波形,如下如7所示,發現斷開R15后,干擾波形依然存在,測量DI端波形,如下圖8所示,波形無干擾。因此,基本確定干擾由前級DCDC_OUT與UART6_TX平行布線部分串進來的。

圖7 R15斷開后測量的MCU端與LP處波形

圖8R15斷開后測量DI端波形(黃色)

4、解決方法

原因找到了,那么如何去除干擾呢?

1、布線的時候將這段平行布線改掉,避免平行布線或拉遠布線間距;

2、RS485發送DE引腳加一個小電容濾除噪聲,因為噪聲頻率在1.65MHz,RS485頻率最大110k,頻率相差比較大,好濾除。如下是在DI引腳處添加不同容值的電容時的測試波形圖,考慮到既要去除干擾又要保證信號波形上升下降沿的質量,因此最終選擇用1nF電容。

圖 9 22pF時DI引腳波形圖

圖 10 220pF時DI引腳波形圖

圖 11 1nF時DI引腳波形圖

圖 12 10nF時DI引腳波形圖

審核編輯:湯梓紅

-

噪聲

+關注

關注

13文章

1120瀏覽量

47400 -

RS485

+關注

關注

39文章

1156瀏覽量

82291 -

信號串擾

+關注

關注

0文章

15瀏覽量

8579

原文標題:實例講解:RS485發射端串擾問題如何解決?

文章出處:【微信號:hjldws,微信公眾號:硬件微講堂】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RS485發送數據的時候,AB線上同時在發送數據,B線上的數據是錯誤的為什么?

RS485轉以太網的應用、解決方案和關鍵技術

關于RS485通信信號問題

rs485總線通信故障。當接受串口關閉時候,串口發送數據時rs485總線出現途中干擾是什么原因?

RS485通信網絡的EMC解決方案

RS485簡介

RS485是什么?RS485通信的特點有哪些

MCU中RS485接口設計資料分享

我用stm32通過RS485發送數據到串口,串口收到數據是亂碼是怎么回事啊?

RS485發送時,影響其他串口接收?為什么呢?

STM32F103ZET6基于RS485發送接收簡單例程

RS485的實際應用和維護RS485的常用方法

為什么需要485隔離?常見RS485隔離方案介紹

RS485發送端波形噪聲干擾大的解決方案

RS485發送端波形噪聲干擾大的解決方案

評論