在摩爾定律的驅動下,存儲器和邏輯芯片半導體制造商通過提高晶體管密度來減少產品成本、提升性能[1]。在NAND flash技術中,市場主流是3D結構而不是2D平面結構,這樣可以通過增加3D NAND芯片堆疊層數從而線性地增加存儲密度[2]。同時,圖形化方案的優化也可以提高3D NAND的有效器件密度。本文中,我們將分析不同TCAT (terabit cell array transistor) 3D NAND節點臺階(stair)和狹縫結構(slit)各種圖形化方案的優缺點并分析它們對晶體管密度的影響。本研究中使用的方案和數據基于(或取自于)TechInsights發布的逆向工程報告,建模工具是Lam Coventor SEMulator3D 。

圖形化方案對制造工藝的影響

在3D-NAND中,決定存儲單元和臺階面積的兩個最重要因素是狹縫節距和臺階節距。傳統上,可以通過減小狹縫和臺階結構的尺寸和節距來減小存儲單元和臺階面積,但是會給光刻、蝕刻以及填充工藝帶來許多挑戰。例如,狹縫節距減小,則通孔節距減小,同時通孔的CD也會變小,這導致蝕刻過程中容易出現通孔之間的橋連,以及通孔和襯底虛連等缺陷。另外,隨著臺階尺寸的減小,獲得更好的臺階均勻性和更小的尺寸誤差的難度也隨之加大。很好的工藝窗口控制是非常重要的,只有讓接觸通孔正好落在臺階正中央才能避免其與臺階側壁上別的字線短接。在不犧牲工藝窗口(process window) 的情況下如何提高晶體管密度是3D NAND技術開發的一個關鍵問題。

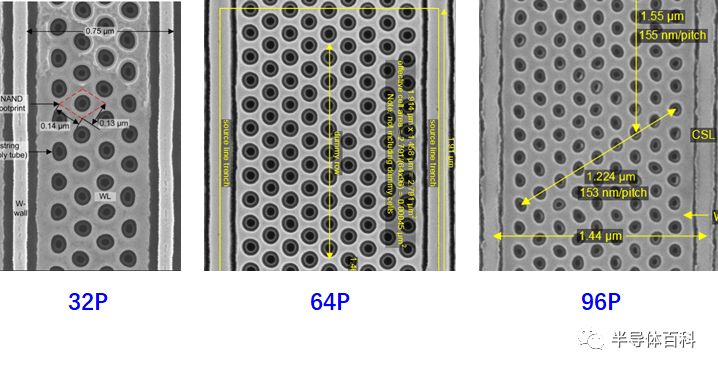

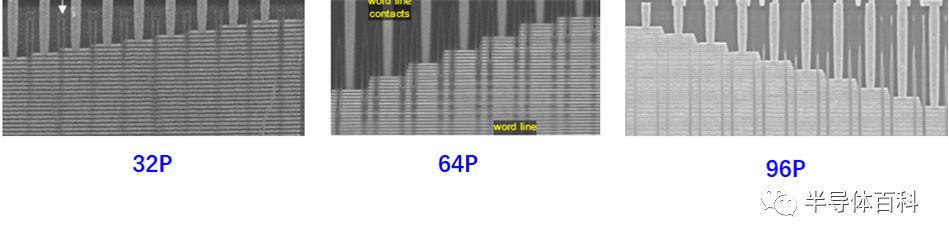

為了進一步探討這個問題,我們基于TechInsights的逆向工程報告,對32P、64P和96P TCAT 3D NAND進行了建模。圖1顯示了32P、64P和96P節點的3D NAND狹縫和溝道孔的俯視圖,圖2是截面圖,表1是建模結構的基本尺寸信息。表1中,更高級的節點(64/96P),狹縫和臺階間距被我們加大以增加工藝窗口。64P和96P兩個節點,我們增加了每個狹縫的通孔數以及每個臺階的字線(word line)數。我們將討論如何通過改變圖形化方案,在不縮小溝道孔CD和節距的情況下提高存儲密度。

圖1,不同節點的狹縫和溝道孔俯視圖。來源:TechInsights

圖2,不同節點臺階橫斷面圖。來源:TechInsights

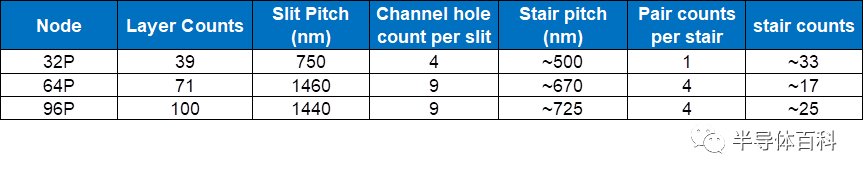

表1,不同節點狹縫和臺階的基本尺寸

超細狹縫圖形化方案

在32P TCAT技術節點,每4個存儲單元(cell)中的1個可以使用位線和字線的組合在任意兩個狹縫之間進行獨立尋址。而64P和96P工藝節點,采用了一種超細狹縫(ultra-mini-slit)工藝,切割中間一排通孔,將9排通孔分成左右各4排。這個超細狹縫將NO堆疊頂部的3層分為2個部分,對應著兩個獨立的字符串線(string line)。通過位線、字線和字符串線的組合,每9個存儲單元中的1個可以進行獨立尋址。引入超細狹縫有三個好處:

節省了位線方向的面積。與普通狹縫相比,超細狹縫的尺寸更小,相鄰通孔之間的空間更小;

工藝難度小。通孔均勻性——尺寸和深度——變得更好;

物理結構更強,因為只有最上面3層被切割,每兩個深狹縫之間只有9個通孔。

然而,這這些優點是需要增加了工藝步驟和光罩數來獲得的。此外,橫向蝕刻和沉積距離較大,使得RMG工藝更具挑戰性。

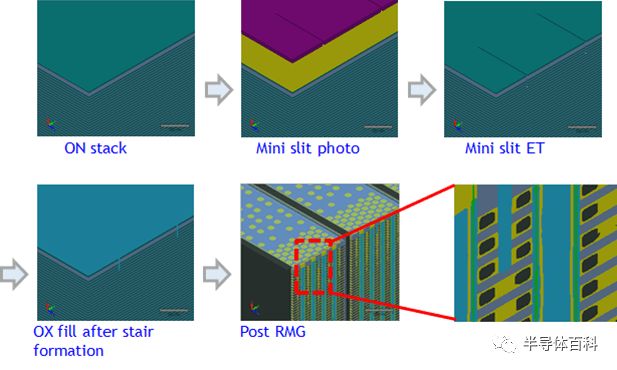

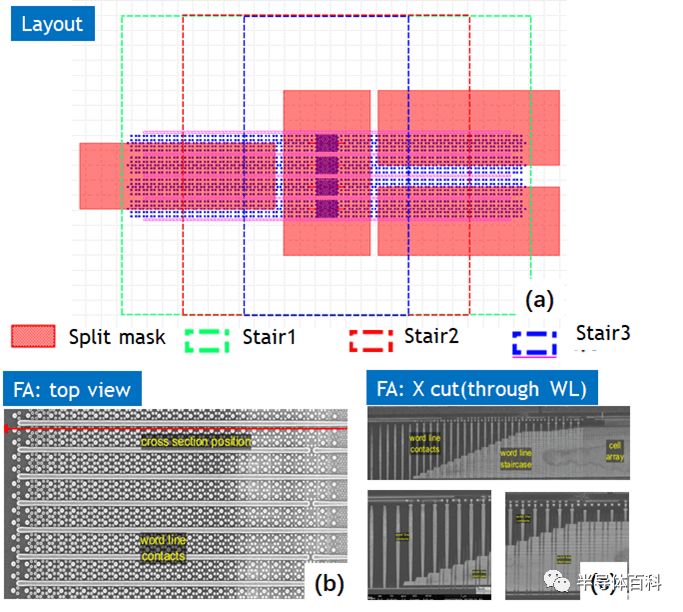

圖3顯示了超細狹縫版圖設計、截面面以及俯視圖。圖4是SEMulator3D建模的超細狹縫工藝流程圖。該工藝流程包括兩個步驟,疊層形成后的超細狹縫曝光和蝕刻工藝,以及臺階蝕刻后的超細狹縫和氧化層填充工藝。

圖3,超細狹縫(a)版圖,(b)截面圖,(c)存儲單元區域的俯視圖,(d)臺階區域的俯視圖。來源:TechInsights

圖4,微縫形成過程的工藝步驟

臺階工藝分析

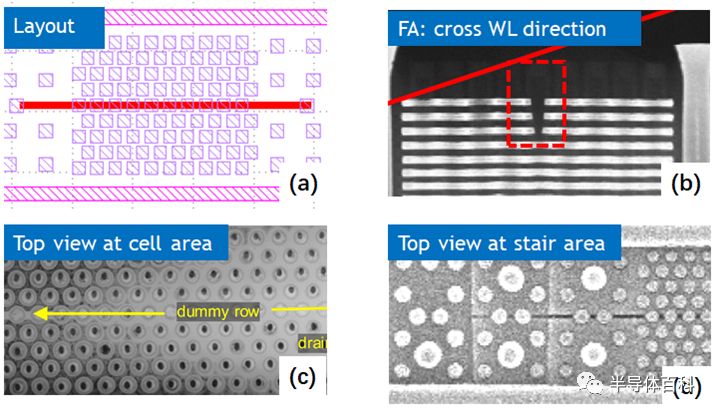

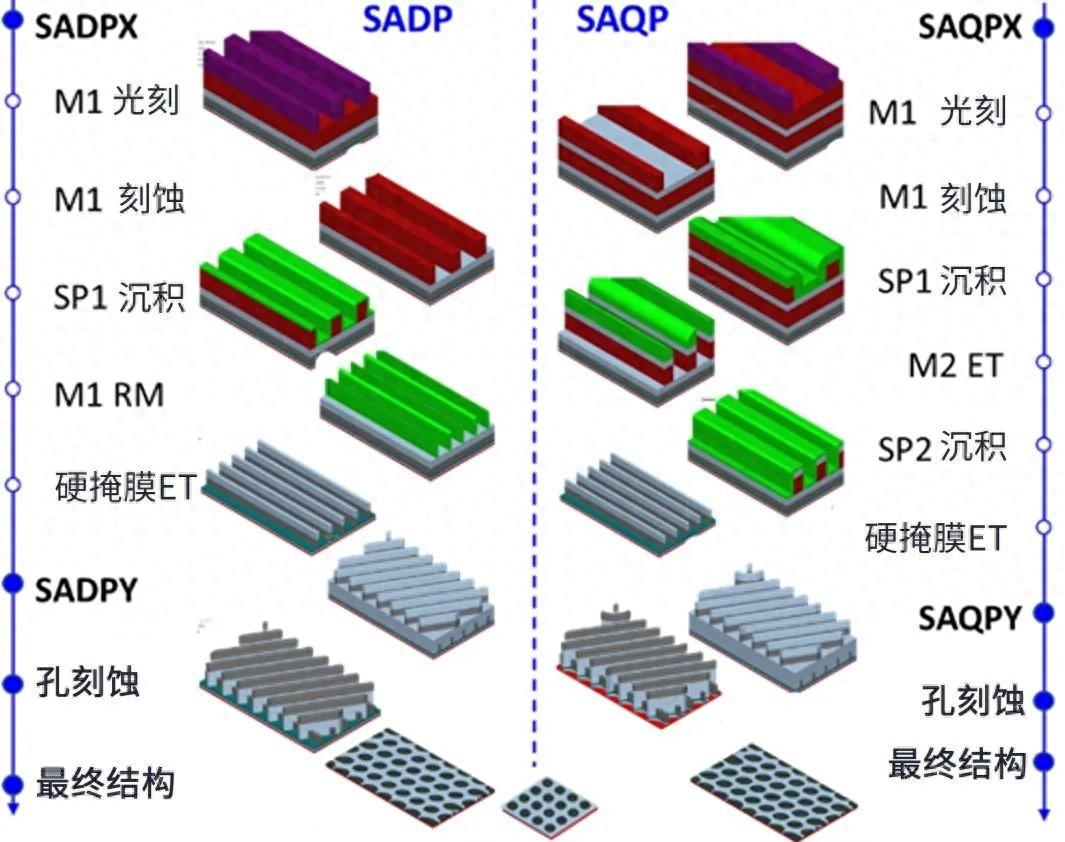

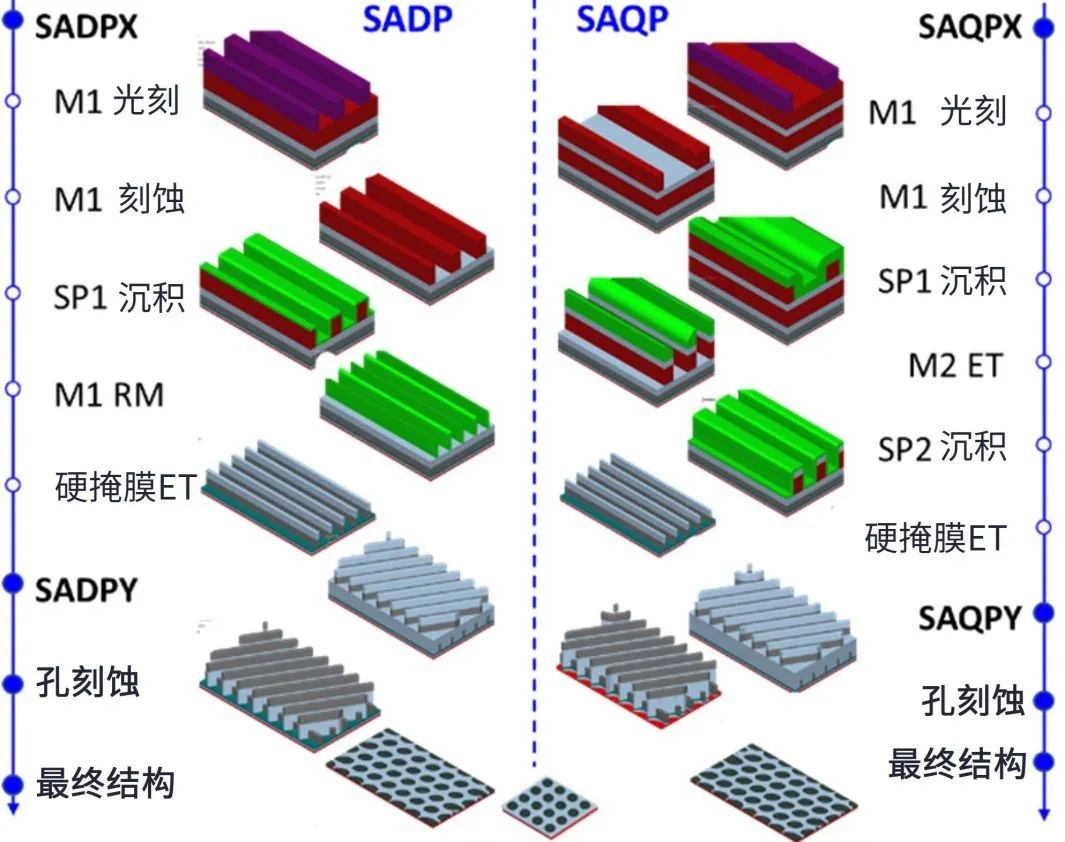

在3D NAND中,字線通過臺階接觸孔與后段金屬相連,每一層臺階的字線接觸孔彼此分開。在32P TCAT工藝(見圖2)中,每層臺階對應一條字線,而在64P和96P工藝中,每層臺階包括4條字線,傳統上我們需要2張光罩才能將這4組字線區分開來。但是通過厚(光刻)阻工藝和臺階修剪(trim),我們只需要一張光罩就能做到這一點。

圖5是64P工藝的版圖設計。我們假設位線是y方向,而字線是x方向。整個存儲單元通過3層臺階(圖中綠紅藍3種顏色)分為4個不同深度。

j‘a

圖5,(a)光罩拆分和臺階光罩的版圖設計,

(b)臺階區俯視圖,(c)橫截面圖(垂直位線方向)。來源:TechInsights

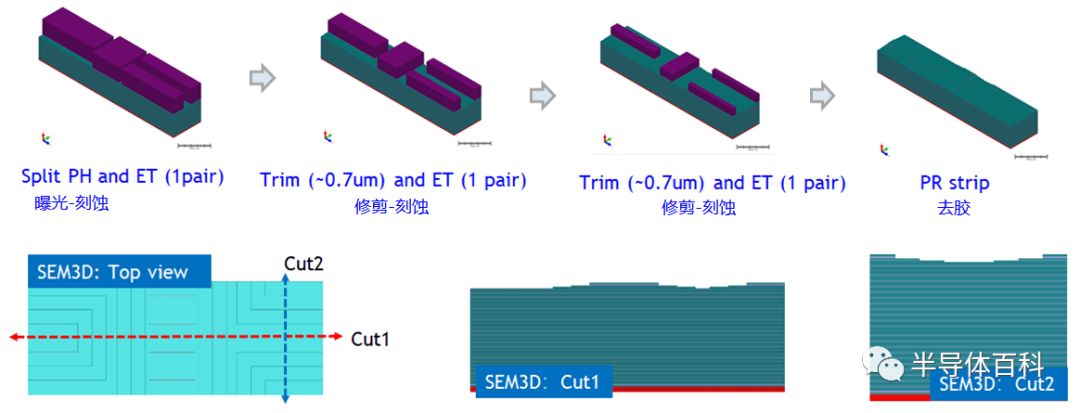

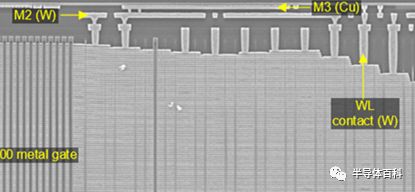

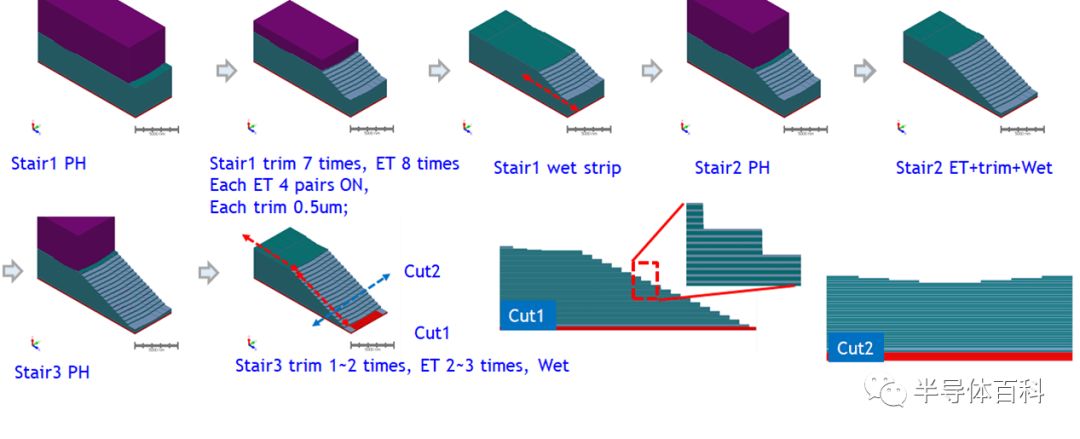

圖6是臺階成型過程的三維示意圖,完整的成型過程需要1次曝光、3次蝕刻和2次修剪。Y方向上,通過光刻,蝕刻將光阻的邊緣與狹縫或小狹縫對齊,每次修剪會在x和y方向消耗約740nm的光阻。圖7是一個實際芯片存儲單元的臺階剖面圖,與圖6中的Cut1基本一樣,證明了我們模型的準確性。

圖6,臺階疊層拆分的工藝步驟

圖7,存儲單元邊緣的臺階剖面圖。來源:TechInsights

圖8是頂層(4層)臺階形成之后下層臺階(16層)的成型過程,一共需要3次曝光,每次曝光之后需要幾次蝕刻和幾次修剪,每次修剪消耗約670nm的光刻膠。圖8的截面圖(Cut1)與圖5(c)中的實際SEM圖像非常類似,顯示了我們建模的準確性。需要注意的是,光刻過程可以是1-》2-》3也可以是3-》2-》1。這種臺階成型方案可以提供多種好處,只需要一張光罩就能區分4組字線,此外,在X方向也只需要更少的光罩。

圖8,臺階成型工藝步驟

在這項研究中,我們使用SEMulator 3D來建立3D NAND分割和臺階圖案方案的處理模型。SEMulator 3D虛擬制造平臺提高了對這些復雜3D-NAND集成方案及其產生的3D結構的理解和可視化,同時提供了一種高效益的時間和成本優化方法。

-

摩爾定律

+關注

關注

4文章

639瀏覽量

79861 -

晶體管

+關注

關注

77文章

10018瀏覽量

141605 -

3D結構光

+關注

關注

0文章

12瀏覽量

553

原文標題:3D NAND 的圖形化方案

文章出處:【微信號:半導體設備與材料,微信公眾號:半導體設備與材料】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

[分享]圖形化系統的設計

labview圖形化編程分享!

淺析Mixly圖形化編程軟件

Mixly圖形化編程軟件介紹

怎樣才能縮短開發圖形化系統設計的時間?

淺析半導體行業圖形化工藝之光刻工藝

EUV工藝不同多重圖形化方案的優缺點及新的進展研究

使用虛擬制造評估先進DRAM電容器圖形化的工藝窗口

評論