通信、工業甚至嵌入式設計越來越需要更高性能的接口。諸如 DDR4 內存、10 Gigabit 以太網、PCIe、串行 ADC 和 DAC 接口等協議正在變得司空見慣。雖然這些高速接口通常出現在高端 FPGA 上,但對于大多數應用來說,這通常是一種過度殺傷的方法并且成本過高。使用低端 FPGA 也不是一種選擇,因為它們不能提供必要的性能。

現在,部署這些接口的成本可以通過使用新型節能、中等密度的 FPGA 顯著降低,這些 FPGA 經過成本優化,功耗更低,提供比更昂貴的 FPGA 更小的外形尺寸,同時仍然提供大量高- 速度接口選項。

應對新的市場動態

盡管各個細分市場是獨一無二的,但它們也有幾個共同點。對更高價值和更低成本的需求正在成為所有應用和細分市場的增長動力。此外,隨著物聯網 (IoT) 的出現,速度更快、數量更多的網絡接口現在變得更加普遍。最后,大多數嵌入式設計中的高速處理是一種新規范。

這些因素要求架構包含千兆以太網等接口,以及足夠快的收發器以支持 10 GbE、JESD204B ADC/DAC、PCIe 接口、HDMI 2.0b 和 DDR4 等內存總線,僅舉幾例。

既然這些類型的接口可用于成本優化、低功耗的中檔 FPGA,設計工程師就有了重要的新選擇來應對其產品的最新市場動態。其中最有價值的選項之一是能夠在 FPGA 的通用輸入輸出 (GPIO) 引腳上使用串行千兆位媒體獨立接口 (SGMII),而不必使用高速收發器。

在 GPIO 上利用 SGMII

在許多通信和工業設計中最常用的接口是千兆以太網 (GbE)。最常見的是,FPGA 通過串行 SGMII 接口連接到 PHY。過去,使用 FPGA 實現 SGMII 接口也需要使用高速收發器。這一切都隨著新的成本優化的中檔 FPGA 的出現而改變,這使得 SGMII 接口可以在通用 GPIO 引腳上使用,以實現 GbE 到 FPGA 鏈接的最低功耗實現。

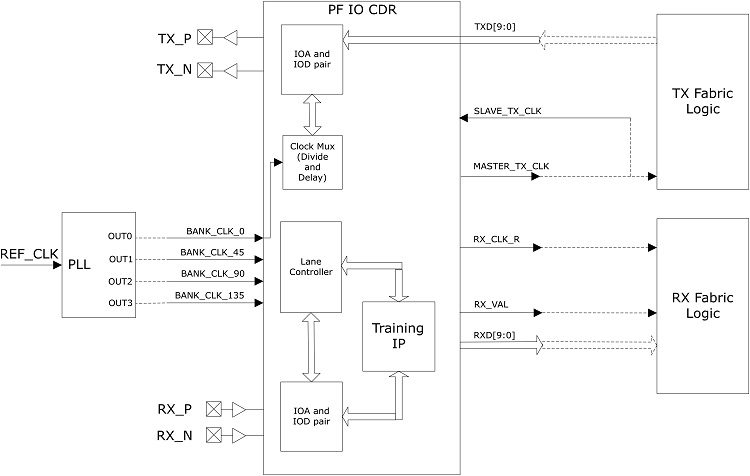

許多嵌入式產品開發人員使用 GbE 來實現越來越多的連接。這些鏈接不再僅適用于數據有效負載,而且在控制、管理、狀態等方面變得無處不在。雖然低端和傳統中端 FPGA 都可以支持這些 1-Gbps 速度,但它們需要收發器來實現 1.25-Gbps SGMII 接口以及其他高速接口。理想情況下,設備應具有專門分配的通用 I/O 引腳以支持 SGMII(圖 1)。

圖 1:傳統和中檔 FPGA 可以支持 1-Gbps 速度,但它們需要收發器來實現 1.25-Gbps SGMII 接口。

低端 FPGA 和傳統中端 FPGA 沒有這個特性,所以它們必須依賴收發器。以這種方式實現接口可能具有挑戰性,因為這些收發器接口非常珍貴且經常稀缺。為了有足夠的它們來滿足更高性能的接口要求,設計人員以前必須選擇更昂貴、更高密度的 FPGA 架構。

工業設計中通常不需要這些大型 FPGA 結構,但設計人員無論如何都被迫選擇它們,只是為了擁有足夠的額外收發器。此外,這些更大的設備意味著需要更大的封裝尺寸。結果是工業市場需要相反的更高的功耗和成本。

當今的低功耗、成本優化的中檔密度 FPGA 逆勢而上,提供了一種通過 GPIO 上的 SGMII 滿足眾多千兆以太網鏈路要求的新方法。一些解決方案更進一步,將時鐘和數據恢復 (CDR) 電路集成到可支持 1.25 Gbps 的高速 LVDS I/O 中。這些特性使器件能夠在眾多 GPIO 引腳上支持 SGMII 接口。與使用傳統中端或高端 FPGA 創建的設計相比,使用這種架構,設計人員可以降低其設計的成本、尺寸和功耗。

平衡速度、成本和功耗

并非每個帶有通信接口的設計都需要極高的性能,但在整個市場中,處理需求都在增加,而接口卻越來越快。這些因素要求 FPGA 支持高達 12.5 Gbps 的串行接口,以實現以下越來越常見的選項:

PCIe Gen2 需要 5 Gbps

HDMI 2.0b,需要 6 Gbps

10 GbE 需要 10 Gbps

JESD204B,最高可運行 12.5 Gbps

這些高速串行接口要求收發器以上述速度運行,但功耗也應優化。對于基于高端架構的高端 FPGA 或中端 FPGA,這些速率的性能微不足道。不幸的是,這些設備也消耗非常高的功率,需要很大的外形尺寸,并且通常超出許多設計的預算。

另一方面,低密度 FPGA 通常沒有收發器,并且包含它們的那些不支持列出的性能速率。平衡收發器速度、低成本和功率效率的答案是使用具有邏輯元件 (LE) 和收發器的正確組合的中等密度 FPGA,以支持所需的數據速率。

通過這些選項,工業架構師可以支持最新的高速串行接口,同時還擁有足夠的片上 LE 來實現必要的電路板功能。此外,在 GPIO 和收發器上實現 SGMII 的能力通常使設計人員能夠選擇更小的封裝尺寸和密度。這降低了系統成本并降低了 FPGA 功能所需的功率。

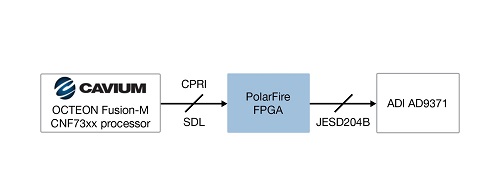

需要串行接口的一個例子是無線微蜂窩。這些設計通常使用處理器來處理大部分信號處理,同時利用 FPGA 進行自定義信號調節并連接到 ADC 和 DAC,如圖2 所示。

圖 2:串行接口設計示例。

在此示例中,FPGA 使用收發器實現 CPRI 或專有串行數字鏈路 (SDL) 到 Cavium 處理器,并通過 JESD204B 實現到 Analog Devices ADC/DAC 的串行鏈路。除了執行串行橋接功能外,FPGA 的結構還可以實現信號調理算法,例如波峰因數降低 (CFR) 和其他功能。該實施方案為小型蜂窩和微蜂窩應用提供了更低功耗的解決方案和更小的占位面積。

實現 DDR4 接口 的新方法

工程師傾向于連接到 FPGA 的最常見存儲器是基于 DDR DRAM 的設備。有幾代可供選擇,最好的選擇通常是使用已經出貨一段時間且不是絕對最新標準的內存。

對于 DRAM,DDR4 提供最佳的每比特成本,并且其架構將被支持多年。盡管 DDR3 仍然是設計的可行選擇,但大多數新設計都選擇 DDR4,因為它將在未來提供更低的價格、更快的性能和更寬的單芯片數據總線。

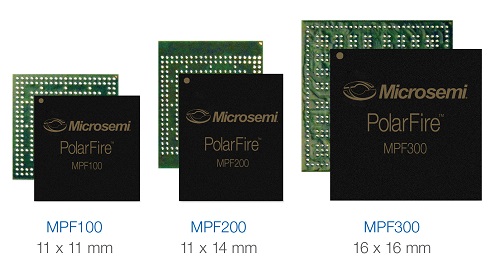

沒有支持 DDR4 存儲器接口的低密度 FPGA,因此設計人員必須使用基于高端架構構建的中等密度 FPGA 來實現這些接口。相比之下,當今最新的中端 FPGA 專為這些接口而構建,以顯著降低的成本和功耗提供所需的 DDR4 性能,同時實現嵌入式設計所需的更小尺寸(圖 3)。這些器件的封裝尺寸范圍從 16 x 16 mm 到 11 x 11 mm。

圖 3:多種密度和外形尺寸的 FPGA。

隨著通信、工業和嵌入式設計對更高性能接口、更多連接和更低成本的需求不斷增長,系統架構師和工程師需要尋找新的解決方案。當今的低功耗、中等密度 FPGA 解決了這些設計挑戰,將更大的價值與更低的功耗相結合,同時仍提供現代設計所需的接口選項和其他功能。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603012 -

接口

+關注

關注

33文章

8575瀏覽量

151023 -

GPIO

+關注

關注

16文章

1204瀏覽量

52055

發布評論請先 登錄

相關推薦

高速ADC與FPGA的LVDS數據接口中避免時序誤差的設計考慮

中端FPGA如何降低高速接口的成本

中端FPGA如何降低高速接口的成本

評論