一、前言

畢業(yè)論文答辯結束,閑下來寫篇文章。芯片研發(fā)人員都在Linux系統(tǒng)下借助各種EDA工具和代碼語言完成工作,因此提高代碼開發(fā)效率,熟練運用開發(fā)工具是十分必要的。本文講述VIM編輯神器的verilogHDL自定義模板調用以及VCS仿真軟件的基本使用方式。

二、VIM編輯器自定義模板調用

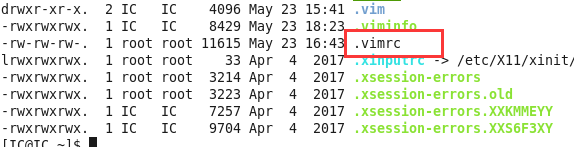

在之前的博文中談到過GVIM編輯器中可以通過調用模板來生成重復性代碼,但沒有介紹自定義模板的方式。關于VIM的安裝與配置詳細內容,見參考文獻1。這里主要用到VIM的用戶配置文件:.vimrc(若沒有新建該文件并編輯),我們在用戶目錄下使用ls -al命令可以看到該文件:

使用VIM編輯器打開VIM配置文件,以下部分是在文件底部自行添加的命令:

:ab Shixu always@(posedge clk or negedge rst_n)begin

自定義模板的格式為 :ab

其中com是調用指令,code是當前指令生成的代碼。我們新建一個.v文件測試下就能看出模板調用的妙處了。

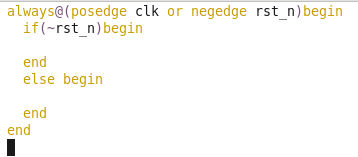

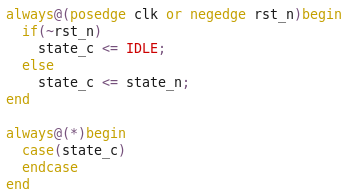

編輯(插入)模式下,輸入Shixu后按下回車生成:

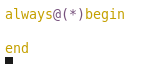

輸入Zuhe后按下回車生成:

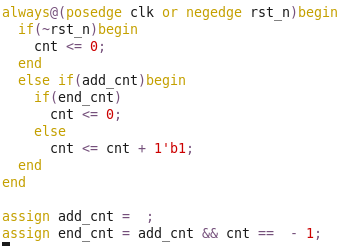

輸入Counter后按下回車生成:

這三個是最常用到的代碼,三者相互組合可以完成很多功能了。但若狀態(tài)或工作模式較多,一般采用狀態(tài)機完成。輸入FSM后按下回車生成:

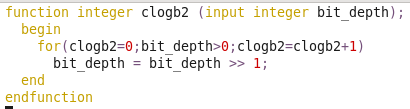

在設計時,經常要根據數(shù)值范圍設定變量的位寬。此時經常用到一個位寬計算到函數(shù)。輸入Width_func后按下回車生成:

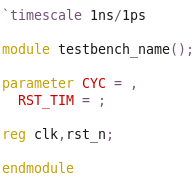

在設計文件里常用的重復性代碼基本就這些了,可以根據自己的coding style靈活調整。接下來說說testbench部分。輸入Test后按下回車生成:

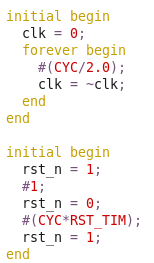

里邊包括了testbench中的時鐘和復位相關的參數(shù)與信號定義。實際上時鐘和復位信號的產生也是可以復用的。輸入Clock_rst后按下回車生成:

自定義模板還沒有靈活到可以生成模塊例化代碼,這一部分功能得借助其他腳本語言完成了,筆者還沒有嘗試過。

三、VCS軟件仿真

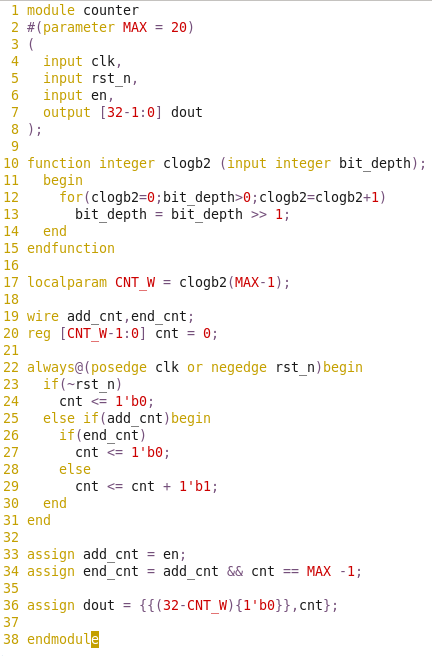

光說這個軟件沒什么意思,我們來舉個栗子~設計一個計數(shù)器,輸出位寬固定32位。當使能信號拉高則開始從0計數(shù)直到最大值后再次從0開始遞增。設計代碼counter.v:

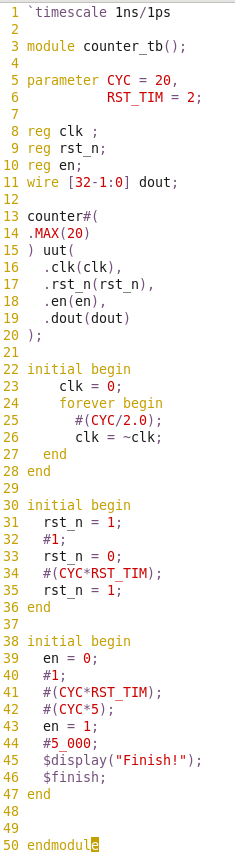

測試代碼 counter_tb.v:

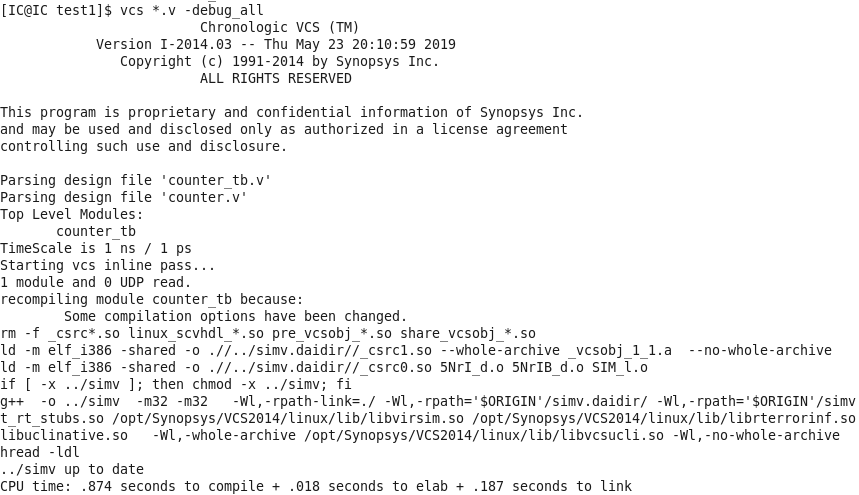

VCS仿真大體分為三步:編譯、仿真以及調試。編譯命令:vcs *.v -debug_all 命令行界面會顯示些信息:

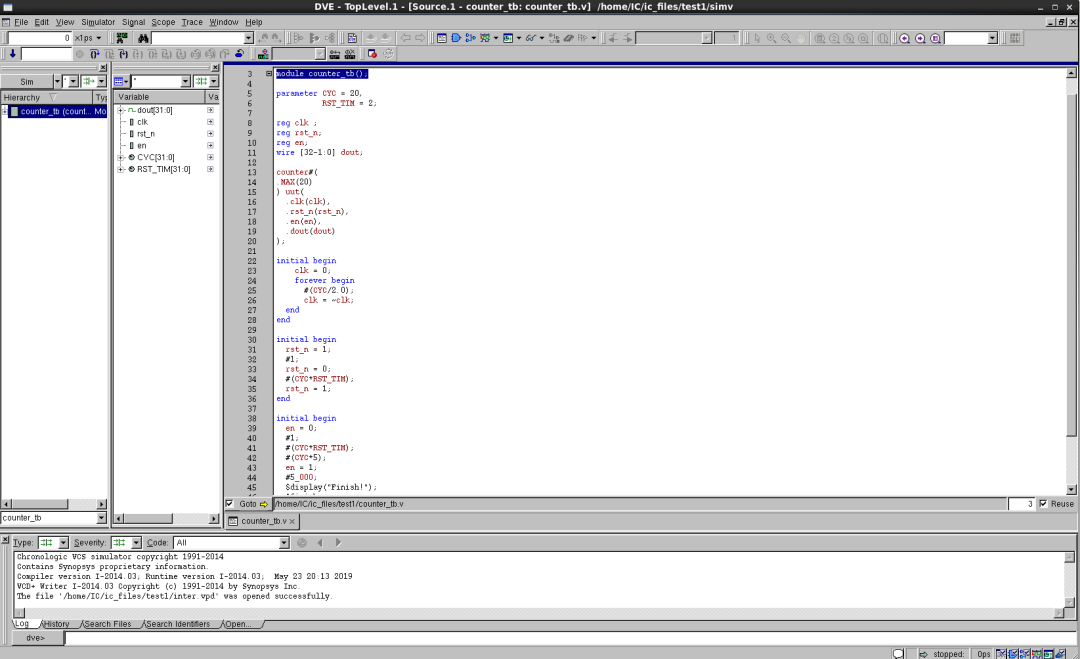

之后文件夾內會生成simv文件,執(zhí)行該文件進行仿真。./simv -gui 這里使用-gui選項打開DVE圖形界面。

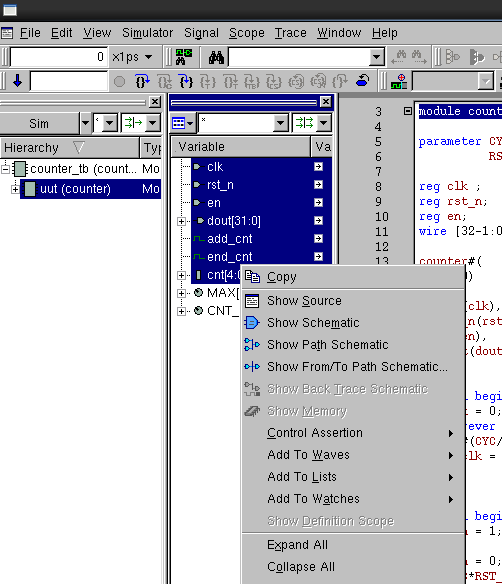

接下來的操作和常用的Modelsim差不多了。把要觀測的信號添加到波形窗口:

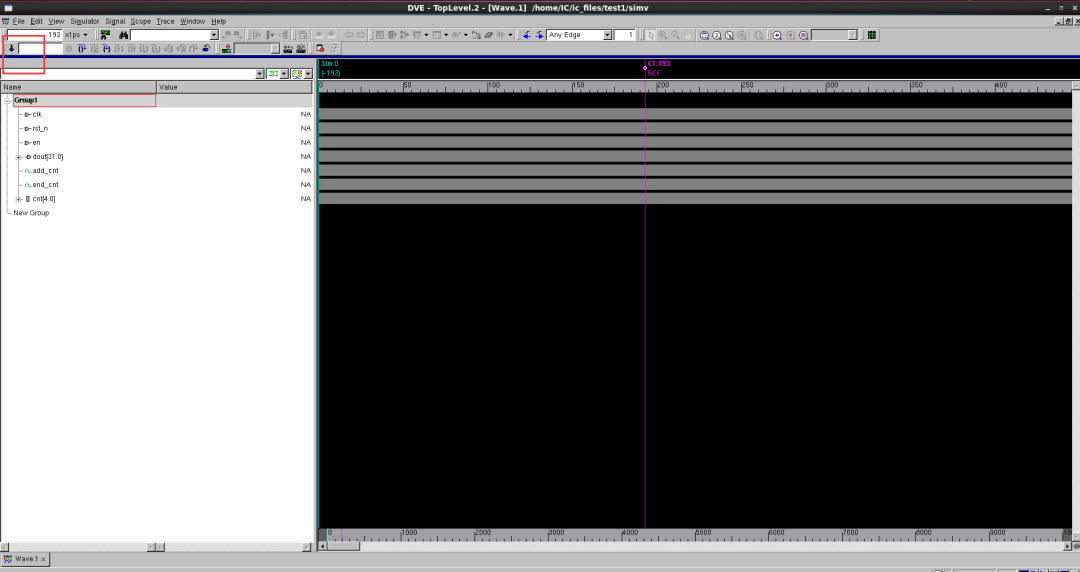

點擊左上角按鈕運行仿真:

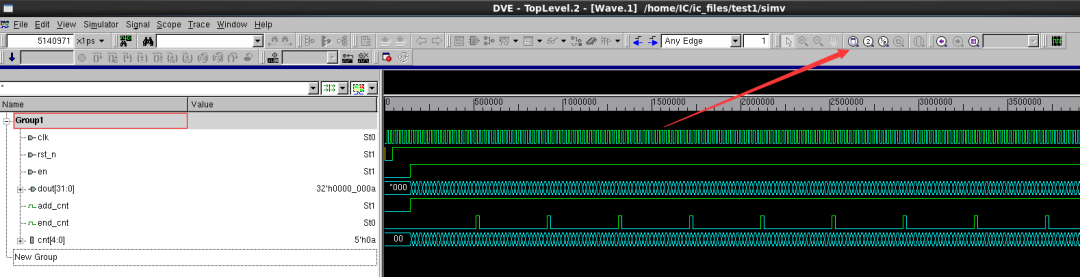

按下紅色箭頭所指位置觀察全局波形:

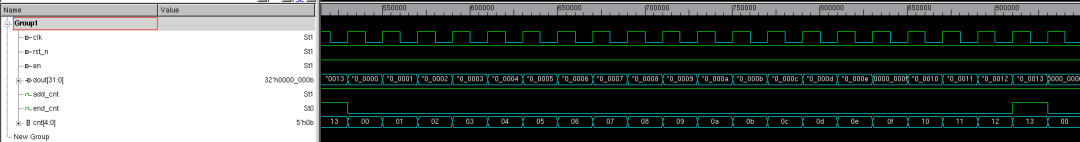

按住鼠標左鍵拖動來局部放大數(shù)據波形,計數(shù)器與輸出從0到19周期性遞增,功能正確。

復雜的操作后續(xù)用到再學。

-

VCS

+關注

關注

0文章

79瀏覽量

9605 -

代碼

+關注

關注

30文章

4787瀏覽量

68591 -

仿真軟件

+關注

關注

21文章

243瀏覽量

30380 -

編輯器

+關注

關注

1文章

806瀏覽量

31169

原文標題:數(shù)字IC設計入門必備——VIM自定義模板調用與VCS基本仿真操作示例

文章出處:【微信號:ZYNQ,微信公眾號:ZYNQ】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

VCS仿真指南(第二版).pdf

VCS DVE 仿真工具講解

nanosim和vcs混合仿真的過程是怎樣的?

基于linux系統(tǒng)的VCS使用及仿真說明

VCS的調試模式

基于linux系統(tǒng)實現(xiàn)的vivado調用VCS仿真教程

VCS仿真軟件的基本使用方式

VCS仿真軟件的基本使用方式

評論