不知道這篇文字應(yīng)該叫電路邏輯結(jié)構(gòu)還是高速信令,想寫的原因是基于之前學(xué)習(xí)模型或者看芯片的設(shè)計(jì)規(guī)范時(shí),會(huì)有下面的一些信息:

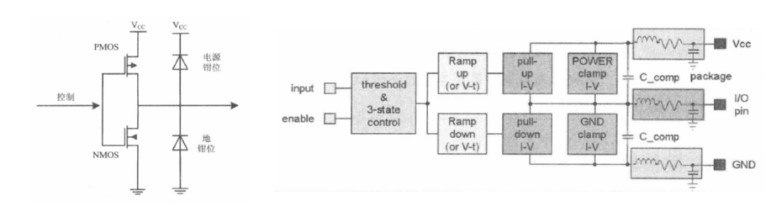

IBIS模型,電路邏輯模型結(jié)構(gòu)里面有COMS電路,由一個(gè)上拉的PMOS管和一個(gè)下拉的NMOS管構(gòu)成,在I/O的接口位置,還有兩個(gè)鉗位二極管。

IBIS模型簡化結(jié)構(gòu)

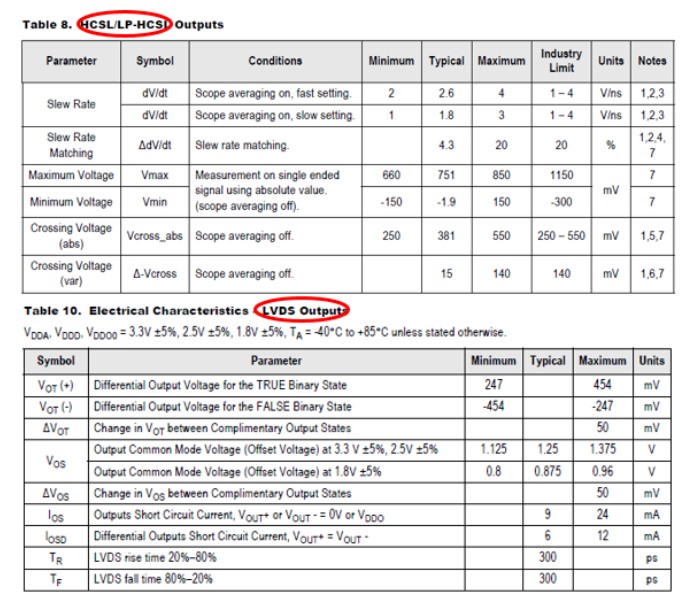

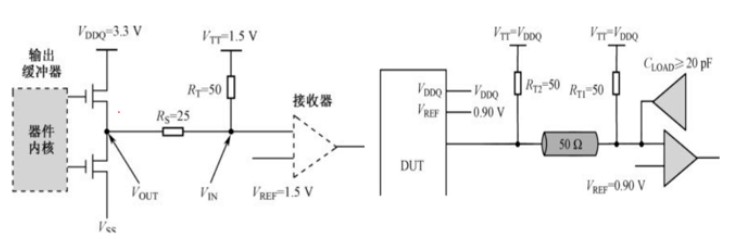

看芯片datasheet ,也會(huì)有各種電路邏輯結(jié)構(gòu):

所以,就想了解一下這些電路邏輯結(jié)構(gòu)。

信號完整性的工作,不管是SI,PI還是EMI,都是管控信號傳播路徑,來滿足相關(guān)標(biāo)準(zhǔn)。而我們看到的紅圈標(biāo)記的東西,是另一種標(biāo)準(zhǔn),即發(fā)送/接收端確定以何種的高低電平與結(jié)構(gòu)進(jìn)行信號轉(zhuǎn)移傳遞。有的資料說,這就是高速信令。

TTL 和CMOS邏輯電路是大學(xué)時(shí)期數(shù)字信號的基礎(chǔ)知識,那里面有邏輯電平分類:5V(5V TTL 5V COMS)3.3V ,2.5V,1.8V等。TTL 和CMOS邏輯電路都是5V電源電壓。但這里面還有區(qū)別,輸入高低電平和輸出高低電平不一樣,比如TTL輸出高電平>=2.4V,而CMOS輸入高電平是3.5V,這時(shí)候CMOS電路檢測不到高電平,就滿足不了要求。

可以通過轉(zhuǎn)換符合電平輸出的芯片,或者增加上拉電阻的方式,來輸出符合要求的電平。一般來說CMOS電路可以直接驅(qū)動(dòng)TTL,但是TTL 不能直接驅(qū)動(dòng)CMOS。

所以不同信令之間需要轉(zhuǎn)換電路來完成對接。

TTL 電路是電流控制器件,CMOS電路是電壓控制器件,這有什么區(qū)別呢?電壓控制需要一個(gè)開關(guān)的過程,有傳輸延遲,大概在25~50ns,電流控制雖然延遲小,但功耗大。

不同應(yīng)用會(huì)選擇不同的邏輯電路。背板系統(tǒng)的總線驅(qū)動(dòng)之前采用TTL或CMOS邏輯電路。但是其3.3~5V的高電壓擺幅導(dǎo)致高功耗,也不能提供正確匹配所需的負(fù)載條件。這個(gè)時(shí)候,采用GTLP(Gunning Transceiver Logic Plus),更低的電壓擺幅和集電極開路輸出級解決了這些問題。

差分信令,第一時(shí)間想到的就是LVDS。

LVDS(Low-Voltage Differential Signaling,低電壓差分信令)又稱RS-644總線接口,是一種數(shù)據(jù)傳輸和接口技術(shù)。LVDS是PCB板級或子系統(tǒng)間高速數(shù)據(jù)傳輸?shù)囊环N高可靠、低功耗、低噪聲、低成本的解決方案。

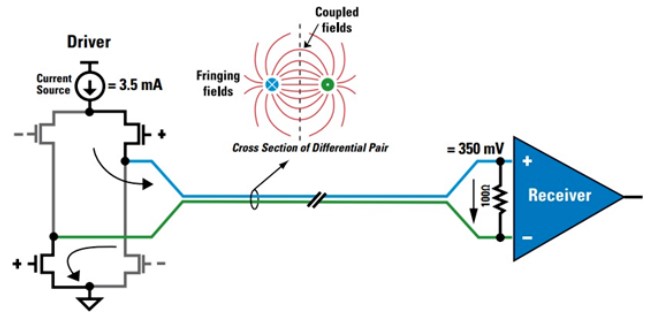

LVDS采用的是電流模邏輯。LVDS輸出包括一個(gè)恒流源,它驅(qū)動(dòng)差分對的電流。兩個(gè)N管導(dǎo)通,在接收器前的匹配電阻上產(chǎn)生正向壓降,輸出高電平;兩個(gè)P管導(dǎo)通,在接收器前的匹配電阻上產(chǎn)生反向壓降,則輸出低電平。接收器匹配電阻上的壓降,正向?yàn)楦撸聪驗(yàn)榈汀?/p>

這一邏輯結(jié)構(gòu)采用低功耗CMOS管,電流源的電流一般為3.5mA,接收器前的匹配電阻一般為100Ω,產(chǎn)生的壓降為350mV。

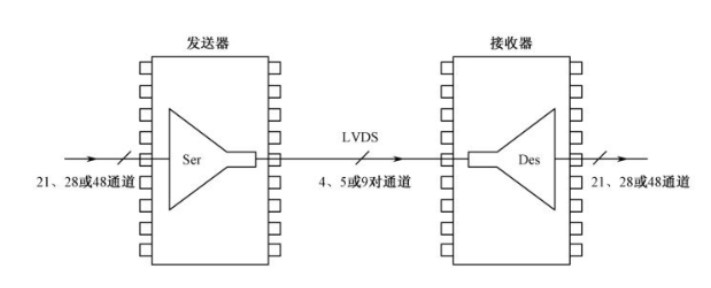

LVDS與TTL/CMOS邏輯的接口設(shè)計(jì)非常方便,采用SerDes芯片就可以輕松實(shí)現(xiàn)TTL/CMOS邏輯并行總線到LVDS串行總線的轉(zhuǎn)換,以及從LVDS串行總線到TTL/CMOS邏輯并行總線的轉(zhuǎn)換。

高速信令有單端信令和差分信令之分。

信令指標(biāo)有很多,比如:邏輯信號電平,應(yīng)用場景,電壓擺幅,驅(qū)動(dòng)方式,負(fù)載匹配,是否支持熱插拔,支持最大的數(shù)據(jù)率等。

邏輯電路及電壓要求

說到應(yīng)用場景,總結(jié)一下常見的一些高速信令:

AGTL+(Assisted Gunning Transceiver Logic+)用于處理器、存儲(chǔ)器和I/O之間的多處理接口以及各種Intel芯片組的系統(tǒng)總線的信令技術(shù)。

HSTL(High-speed Transceiver Logic)一般工作在200MHz以上,是高速存儲(chǔ)器應(yīng)用的I/O接口首選,非常適用于多存儲(chǔ)器組地址總線的驅(qū)動(dòng)。在中頻范圍(100~180MHz),I/O端口的單端信令還有GTL/GTL+、SSTL和LVTTL。

SSTL(Stub-Series Terminated Logic)信令標(biāo)準(zhǔn)是專為高速存儲(chǔ)器應(yīng)用開發(fā)而制定的。特別針對工作頻率為333MHz或以上單雙數(shù)據(jù)率的SDRAM,還支持眾多存儲(chǔ)器、3D圖形卡、LCD顯示、DTV接口和機(jī)頂盒等。

JEDEC定義了3種SSTL標(biāo)準(zhǔn):EIA/JESD8-8 3.3V SSTL(SSTL 3);EIA/JESD8-9B 2.5V SSTL(SSTL 2);EIA/JESD8-15 1.8V SSTL(SSTL 18)。

ECL差分信令能提供比其他任何邏輯更短的傳播時(shí)延和更高的切換速率。有的器件每個(gè)差分對能夠傳輸12Gbps的數(shù)據(jù)率,應(yīng)用在高速測試儀器、光纖網(wǎng)絡(luò)儀器、超高速路由器、網(wǎng)絡(luò)存儲(chǔ)設(shè)備、10 Gb以太網(wǎng)、企業(yè)計(jì)算服務(wù)器和高性能工作站等。

CML(Current-Mode Logic)信令屬于ECL工藝,廣泛應(yīng)用于新型高速器件,應(yīng)用于網(wǎng)絡(luò)物理層和SerDes器件。CML串行差分信令數(shù)據(jù)率為1~10Gbps,速度取決于驅(qū)動(dòng)器和接收器的生產(chǎn)工藝技術(shù)。

應(yīng)用部分,硬件工程師很關(guān)注,信號完整性方面,我們更關(guān)注相關(guān)邏輯電路在實(shí)際版圖的設(shè)計(jì),相關(guān)規(guī)則:1.走線阻抗匹配;2.對稱性走線;3.減少過孔數(shù)量及相關(guān)不連續(xù)點(diǎn);4.走線角度……都是關(guān)于管控信號完整性的高速設(shè)計(jì)的相關(guān)規(guī)則。未來高速設(shè)計(jì)的規(guī)則會(huì)成為一種常態(tài),如何在設(shè)計(jì)中管控和取舍,這里就不過多展開了。

審核編輯:劉清

-

NMOS

+關(guān)注

關(guān)注

3文章

295瀏覽量

34434 -

信號完整性

+關(guān)注

關(guān)注

68文章

1409瀏覽量

95510 -

轉(zhuǎn)換電路

+關(guān)注

關(guān)注

2文章

205瀏覽量

30505 -

鉗位二極管

+關(guān)注

關(guān)注

1文章

33瀏覽量

9199

發(fā)布評論請先 登錄

相關(guān)推薦

總結(jié)一下高速信令的指標(biāo)與應(yīng)用場景

總結(jié)一下高速信令的指標(biāo)與應(yīng)用場景

評論