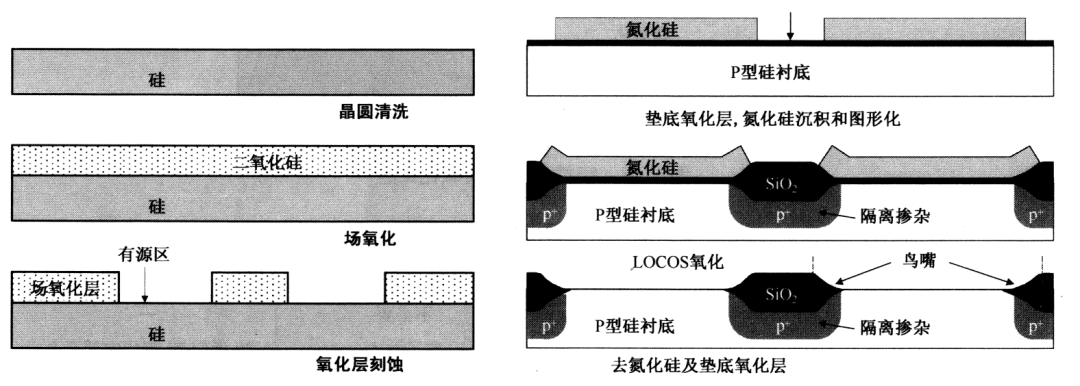

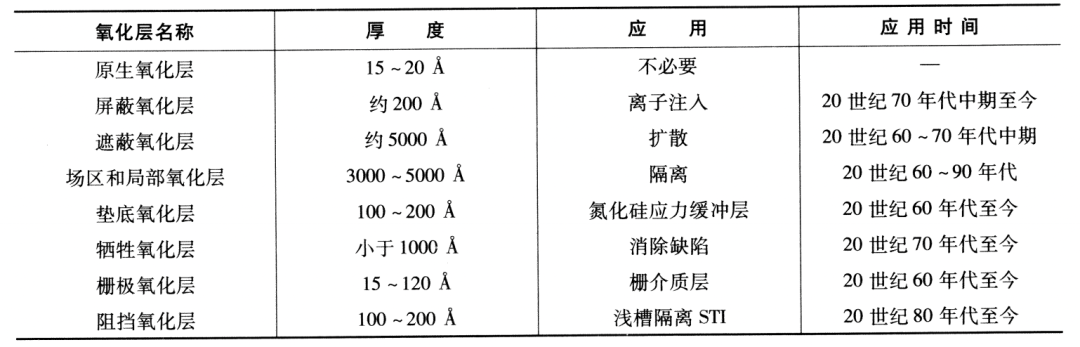

熱生長的二氧化硅最重要的應用之一是形成絕緣體使IC芯片上相鄰晶體管間電氣隔離。整面全區覆蓋式氧化和局部氧化是隔離相鄰元器件并防止它們相互干擾所用的兩種技術。整面全區覆蓋式氧化層是最簡單的隔離工藝,早期的半導體生產普遍使用這種技術。熱生長一層5000-10 000A的二氧化硅,通過光刻技術使其圖形化,再用氫氟酸刻蝕氧化層,接著將器件區打開后就可以開始晶體管的制造過程了(見下圖)。

硅局部氧化(LOCOS)的隔離效果比整面全區覆蓋式氧化效果好。LOCOS工藝使用一層很薄的二氧化硅層200-500A作為襯墊層以緩沖LPCVD氮化硅的強張力。經過氮化硅刻蝕、光刻膠剝除和晶圓清洗后,沒有被氮化硅覆蓋的區域再生長出一層厚度為3000?5000 A的氧化層。氮化硅的阻擋效果比二氧化硅好,由于氧分子無法穿過氮化硅層,所以氮化硅層下的硅并不會被氧化。而未被氮化硅覆蓋的區域,氧分子就會不斷擴散穿過二氧化硅層與底層的硅形成更厚的二氧化硅。LOCOS的形成過程如下圖所示。

由于氧在二氧化硅中的擴散是一種等向性過程,所以氧也會碰到側邊的硅。這使得 LOCOS工藝有兩個缺點:一個缺點是靠近刻蝕氧化窗口的氮化硅層底生長有氧化物,這就是所 謂的鳥嘴(Bird?sBeak)(見下圖)。鳥嘴占據了晶圖表面的很多面積,是應盡量避免出現的情況。另一個缺點是由于氧化物的生長特點而形成氧化層對硅有一個表面臺階,這將引起表面平坦化問題。

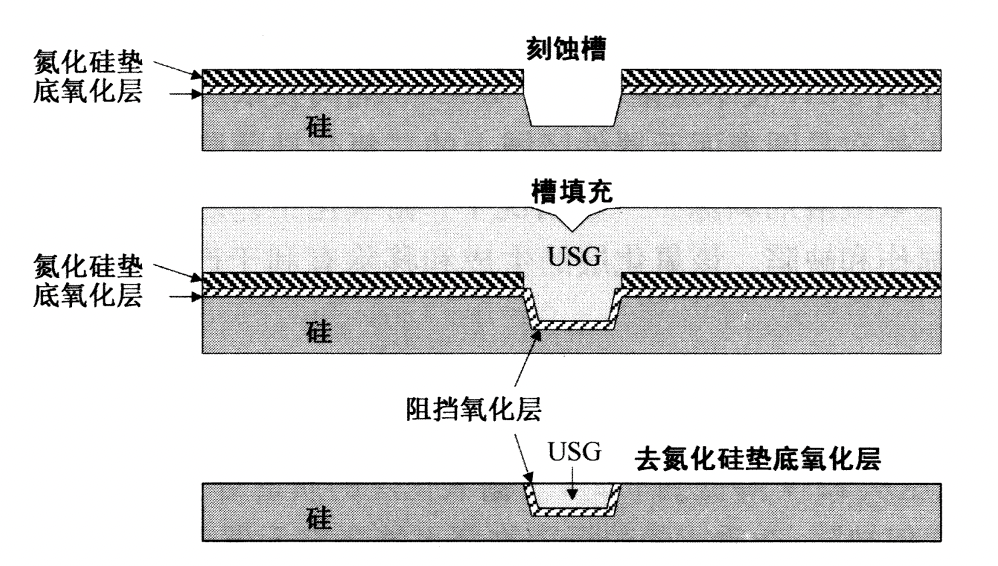

已經采用了許多方法抑制鳥嘴效應,其中最普遍的是多晶硅緩沖層(Poly Buffered LOCOS, PBL)T藝。較厚的襯墊層形成較長的鳥嘴,這使得氧分子擴散的路徑變得較寬。使用一層厚度大約為500 A的多晶硅緩沖LPCVD氮化硅的高張力,襯墊氧化層的厚度能從500 A降低到 100 A,從而可以大大減小氧化物的侵入。但是硅的局部氧化層兩側總有0. 1?0.2um的鳥嘴。當最小圖形尺寸小于0.35um時,鳥嘴問題變得很嚴重,于是發展出了淺溝槽隔離(STI)工藝以避免鳥嘴效應,STI形成的表面也比較平坦。20世紀90年代中期,當元器件圖形尺寸縮小到0. 35um以下時,STI技術逐漸取代了LOCOS隔離技術。

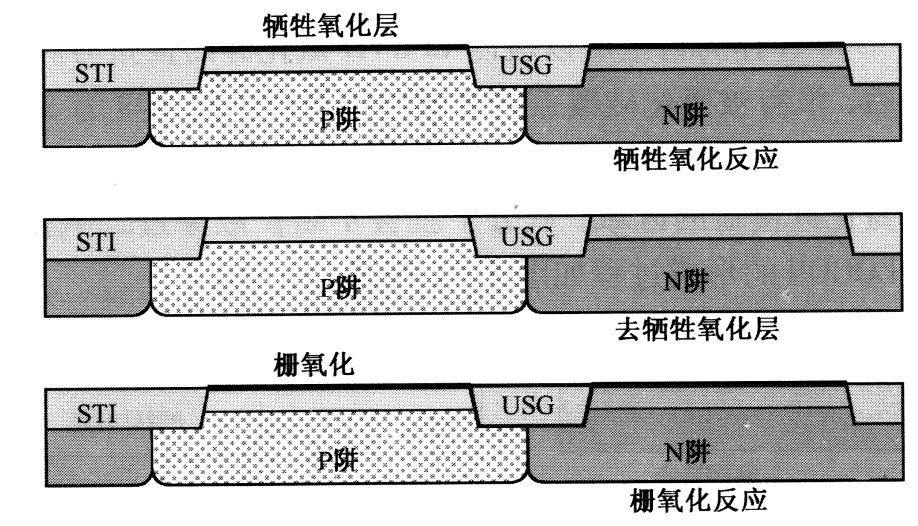

犧牲氧化層是生長在晶圓表面元器件區域上的二氧化硅薄膜(低于1000 A)o犧牲氧化層生成之后將立刻被氫氟酸溶劑剝除。一般情況下,柵氧化工藝之前都將先生長一層犧牲氧化層來移除硅表面的損傷和缺陷。該氧化層的生成和移除有利于產生零缺陷的硅表面并獲得高質量的柵氧化層。

以MOS為主的IC芯片,其最薄也最重要的二氧化硅層是柵氧化層。由于元器件尺寸不斷縮小,柵氧化層從20世紀60年代大于1000 A厚度降低到2000年復雜芯片上的15 A左右,而且IC芯片的工作電壓從12 V降低到1.2 Vo柵氧化層的質量對于元器件能否正常工作非常重要,柵氧化層中的任何缺陷、雜質或微粒污染物都可能影響元器件的性能,并且顯著降低芯片的成品率。下圖說明了犧牲氧化層和柵氧化層的形成過程,下表列出了 IC生產中應用熱生長的二氧化硅情況。

審核編輯 :李倩

-

半導體

+關注

關注

334文章

27442瀏覽量

219474 -

晶體管

+關注

關注

77文章

9701瀏覽量

138386 -

IC芯片

+關注

關注

8文章

248瀏覽量

26259

原文標題:半導體行業(一百二十三)——加熱工藝(四)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

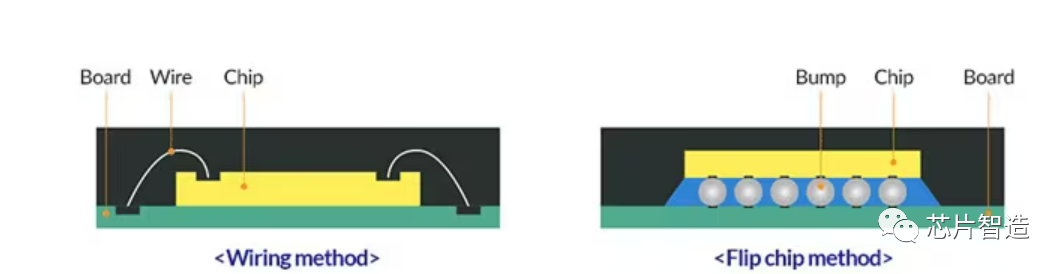

倒裝封裝(Flip Chip)工藝:半導體封裝的璀璨明星!

半導體晶圓制造工藝流程

半導體濕法刻蝕設備加熱器的作用

激光錫球焊接機植球工藝在半導體行業的崛起

周星工程研發ALD新技術,引領半導體工藝革新

半導體發展的四個時代

半導體發展的四個時代

半導體封裝工藝面臨的挑戰

半導體行業——加熱工藝解析

半導體行業——加熱工藝解析

評論