數(shù)字硬件建模SystemVerilog-按位運(yùn)算符

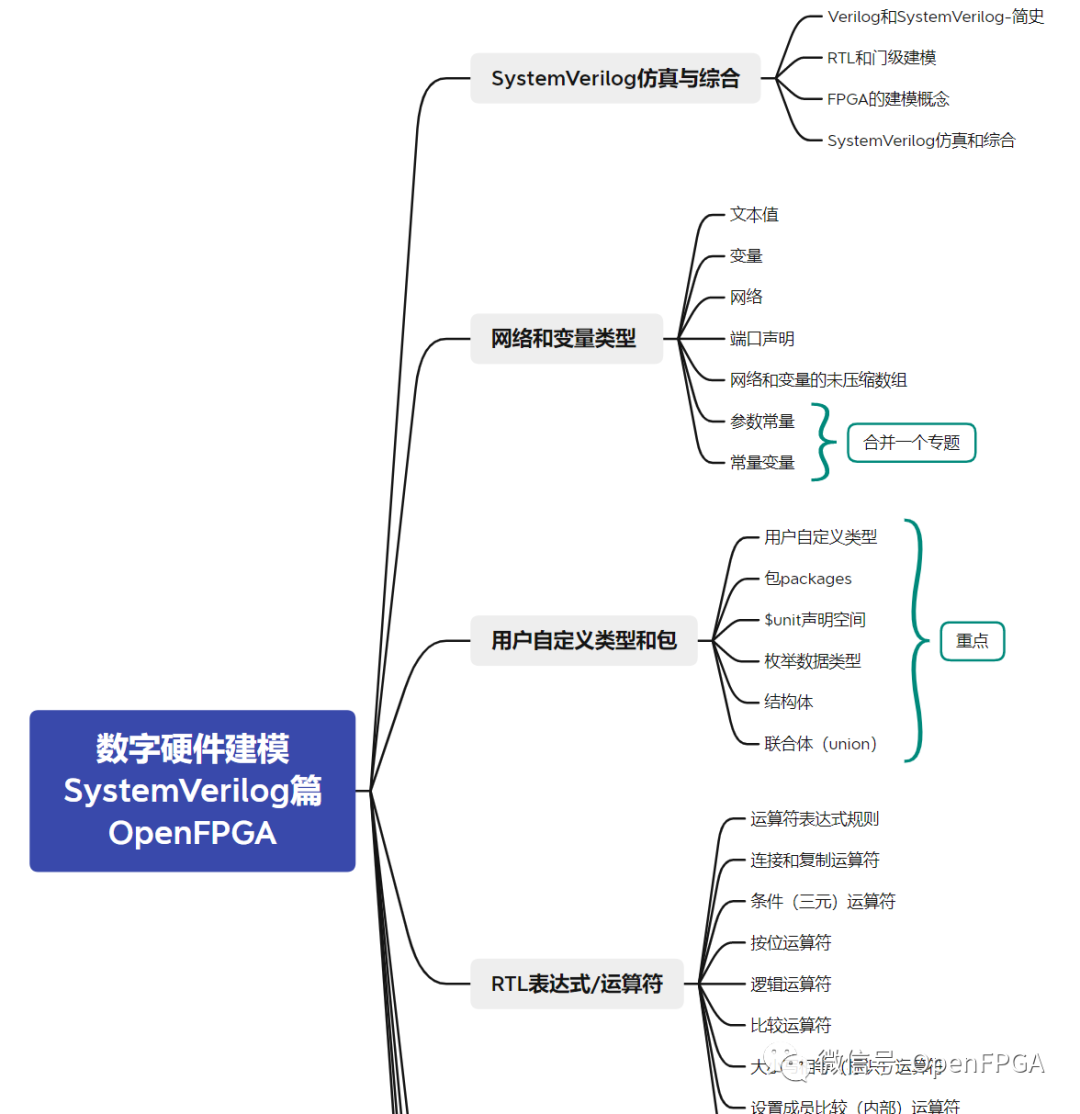

經(jīng)過(guò)幾周的更新,SV核心部分用戶自定義類型和包內(nèi)容已更新完畢,接下來(lái)就是RTL表達(dá)式和運(yùn)算符。

馬上HDLBits-SystemVerilog版本也開始準(zhǔn)備了,基本這一部分完成后就開始更新~

介紹

(按)位運(yùn)算符(Bitwise operators)

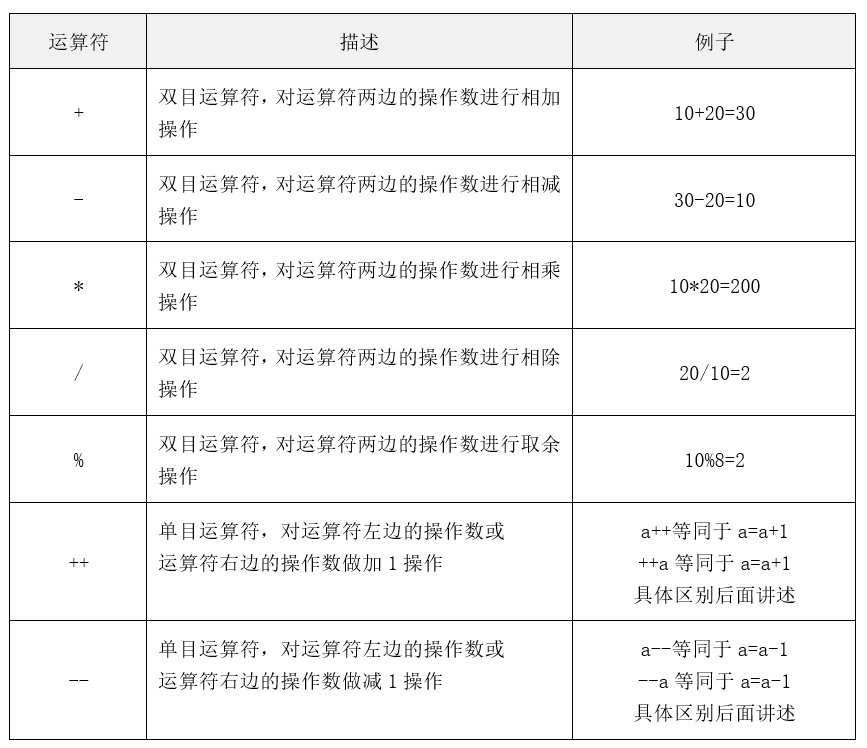

位運(yùn)算符一次執(zhí)行一位操作,從最右邊的位(最低有效位)向最左邊的位(最高有效位)移動(dòng)。表5-3列出了按位運(yùn)算符功能。

| 運(yùn)算符 | 示例用法 | 描述 |

|---|---|---|

| ~ | ~m | 將m(1的補(bǔ)碼)的每一位反轉(zhuǎn) |

| & | m&n | m和n的每一位相與(AND) |

| ^ | m ^ n | m與n的每一位相異或(XOR) |

| ^~或者~^ | m ^~n | m和n的每一位相同或 |

| I | mIn | m和n的每一位相或(OR) |

(I代表 | - 或操作)

沒有位NAND或NOR運(yùn)算符。NAND或NOR操作是分別反轉(zhuǎn)AND或OR操作的結(jié)果,如~(m&n)。需要括號(hào),以便先執(zhí)行AND運(yùn)算。

位運(yùn)算要求兩個(gè)操作數(shù)的向量大小相同。在執(zhí)行操作之前,較小的操作數(shù)將擴(kuò)展以匹配較大操作數(shù)的大小。

(按)位反轉(zhuǎn)

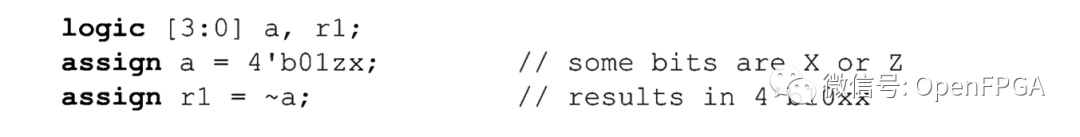

按位反轉(zhuǎn)(Bitwise inversion.)。位反轉(zhuǎn)運(yùn)算符將其單個(gè)操作數(shù)的每一位反轉(zhuǎn),從右向左操作,結(jié)果是操作數(shù)值的一個(gè)補(bǔ)數(shù)。位反轉(zhuǎn)運(yùn)算符是X-pessimistic-反轉(zhuǎn)X或Z值的結(jié)果始終是X。表5-4顯示了位反轉(zhuǎn)的真值表。表中的結(jié)果針對(duì)操作數(shù)的每一位。

| ~ | 結(jié)果 |

|---|---|

| 0 | 1 |

| 1 | 0 |

| X | X |

| Z | X |

位反轉(zhuǎn)操作的一個(gè)示例結(jié)果是:

(按)位AND

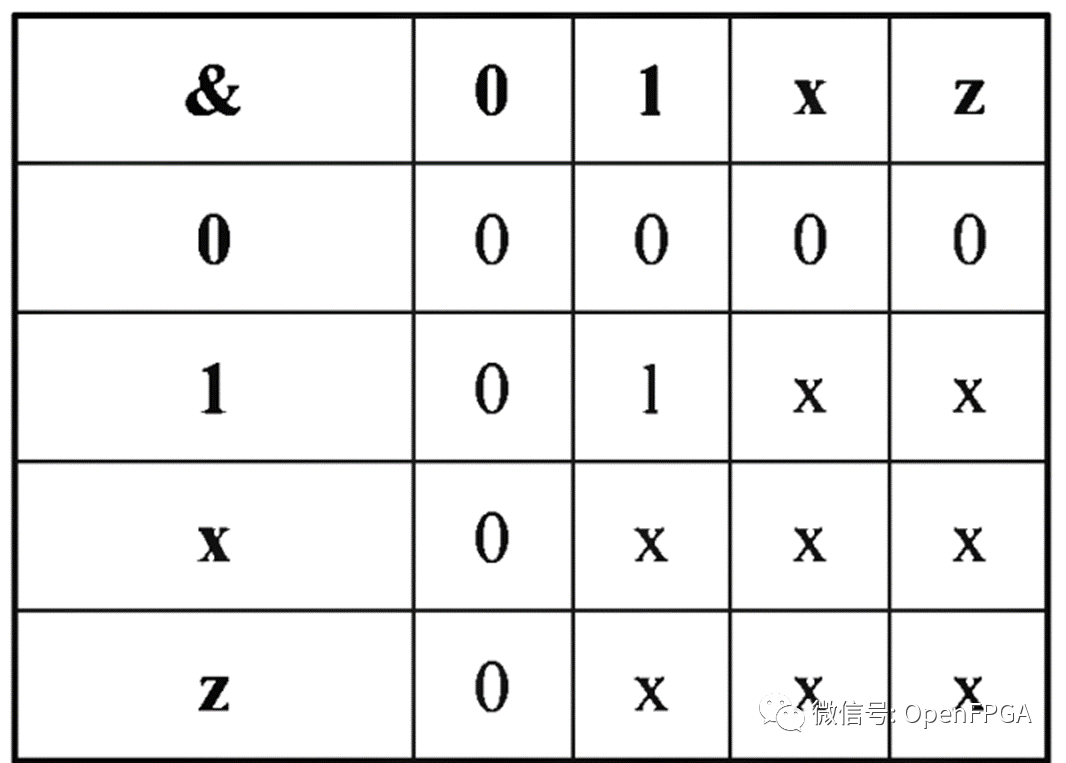

按位和(Bitwise AND)。位AND運(yùn)算符對(duì)第一個(gè)操作數(shù)的每一位與第二個(gè)操作數(shù)中的對(duì)應(yīng)位進(jìn)行布爾AND運(yùn)算,從右到左運(yùn)算。位AND運(yùn)算符是X-optimistic:0與任何值的AND運(yùn)算都將得到0。表5-5顯示了位AND的真值表。表中的結(jié)果針對(duì)兩個(gè)操作數(shù)的每一位。

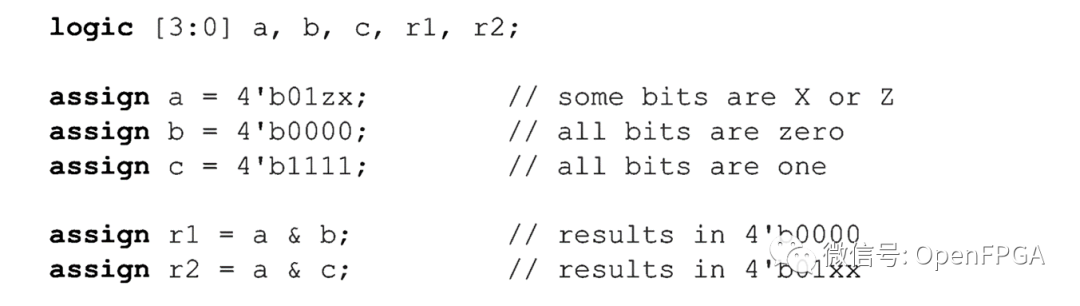

位AND運(yùn)算的一些示例結(jié)果如下:

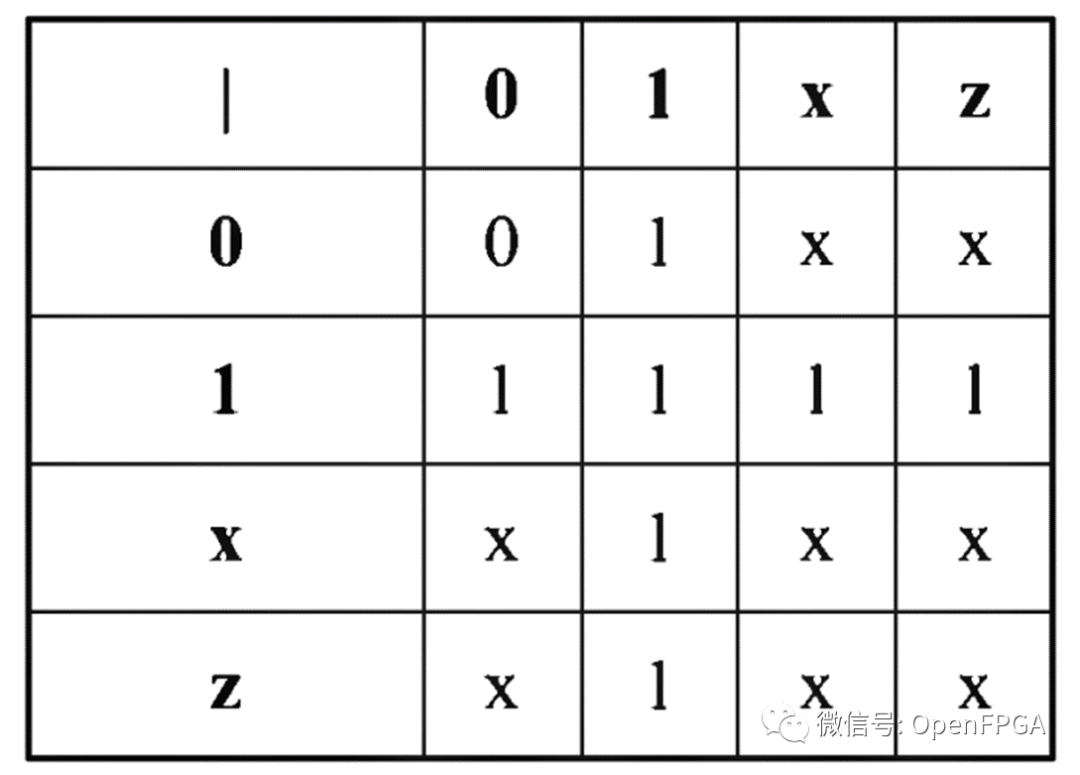

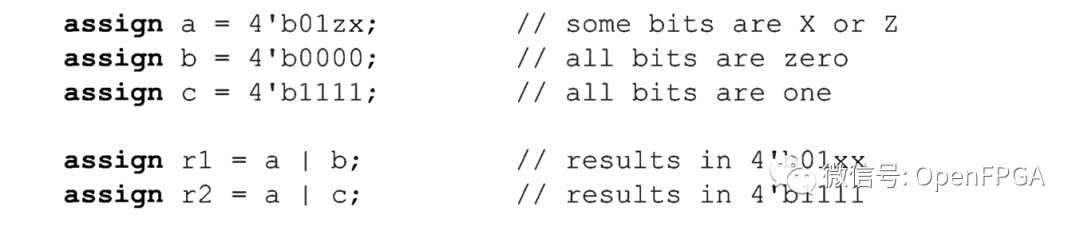

(按)位OR

按位或(Bitwise OR)。位OR運(yùn)算符對(duì)第一個(gè)操作數(shù)的每一位與第二個(gè)操作數(shù)中的對(duì)應(yīng)位進(jìn)行布爾OR運(yùn)算,從右向左進(jìn)行運(yùn)算。位OR運(yùn)算符是X-optimistic-與任何值進(jìn)行OR運(yùn)算結(jié)果都是1。表5-6顯示了位OR的真值表。

按位OR運(yùn)算的一些結(jié)果示例如下:

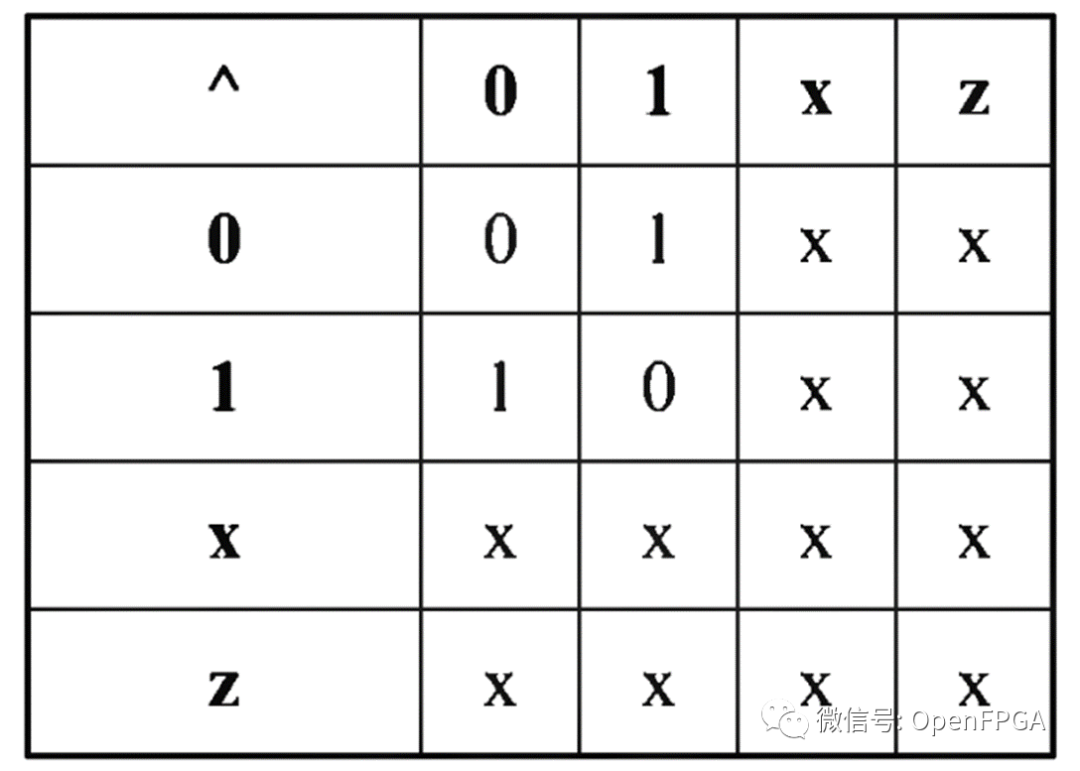

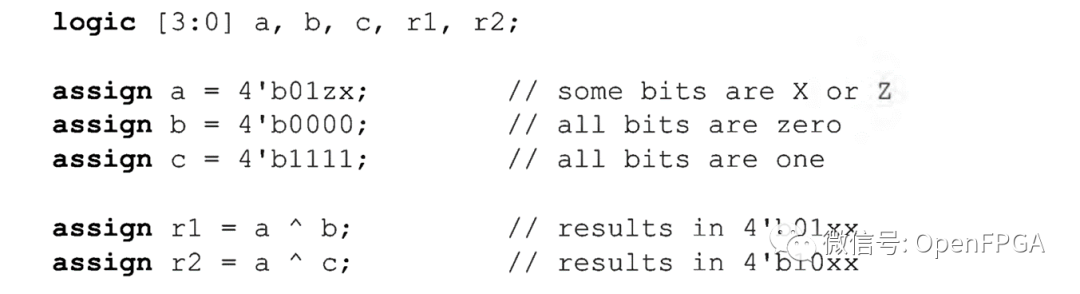

(按)位XOR

按位異或(Bitwise XOR)。位XOR運(yùn)算符對(duì)第一個(gè)操作數(shù)的每一位與第二個(gè)操作數(shù)的對(duì)應(yīng)位進(jìn)行布爾異或XOR運(yùn)算,從右到左進(jìn)行運(yùn)算。按位異或運(yùn)算符為X-pessimistic——對(duì)X或Z值進(jìn)行異或運(yùn)算的結(jié)果始終為X。表5-7顯示了按位異或的真值表。

按位異或運(yùn)算的一些示例結(jié)果如下:

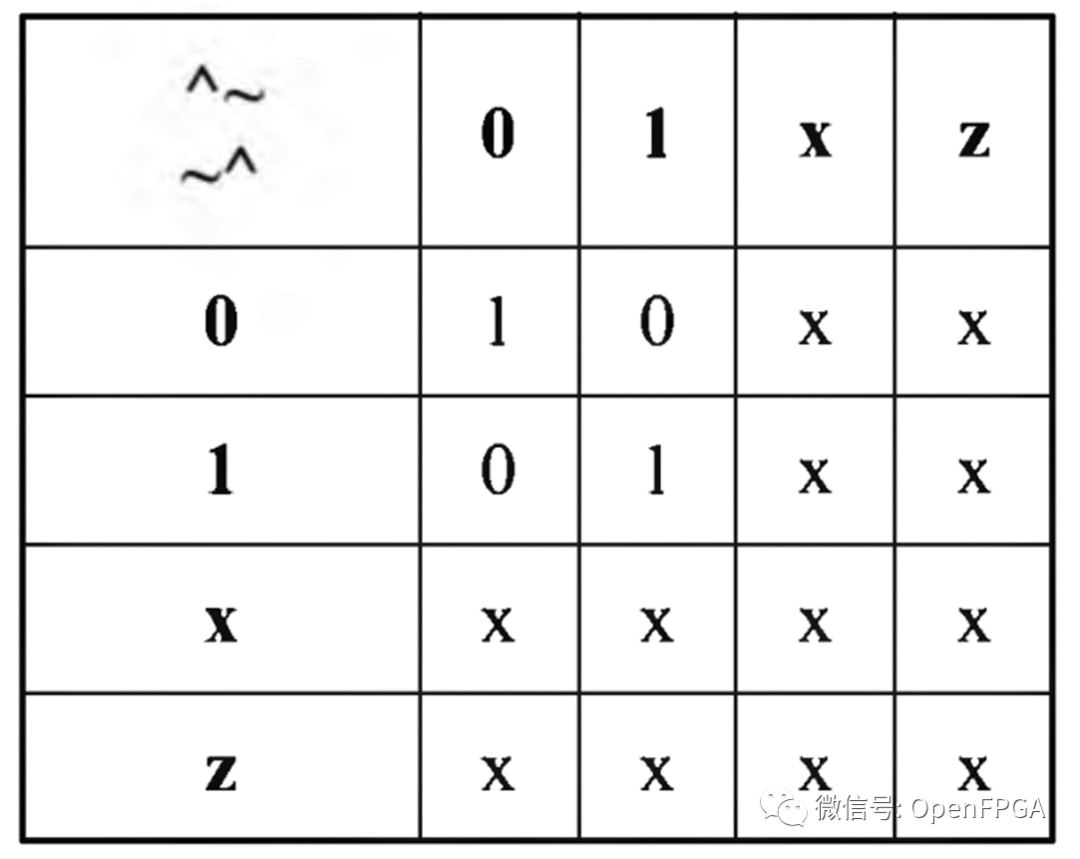

(按)位XNOR

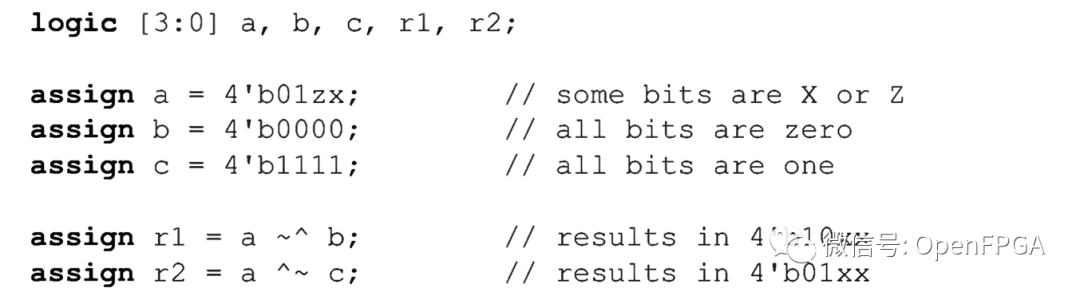

按位XNOR(Bitwise XNOR)。位XNOR運(yùn)算符對(duì)第一個(gè)操作數(shù)的每一位與第二個(gè)操作數(shù)的對(duì)應(yīng)位進(jìn)行布爾XNOR運(yùn)算,從右到左進(jìn)行運(yùn)算。位XNOR運(yùn)算符為X-pessimistic ——對(duì)X或Z值進(jìn)行XNOR運(yùn)算的結(jié)果為X。表5-8顯示了按位XNOR的真值表。

按位XNOR運(yùn)算的一些示例結(jié)果如下:

示例5-5說(shuō)明了一個(gè)利用按位運(yùn)算符的小型RTL模型。

//`begin_keywords"1800-2012"//useSystemVerilog-2012keywords

//User-definedtypedefinitions

packagedefinitions_pkg;

typedefenumlogic{AND_OP,XOR_OP}mode_t;

endpackage:definitions_pkg

//MultiplexedN-bitwidebitwise-ANDorbitwise-XORoperation

moduleand_xor

importdefinitions_pkg::*;

#(parameterN=4)//opsize(default8-bits)

(inputmode_tmode,//1-bitenumeratedinput

inputlogic[N-1:0]a,b,//scalableinputsize

outputlogic[N-1:0]result//scalableoutputsize

);

timeunit1ns;timeprecision1ns;

always_comb

case(mode)

AND_OP:result=a&b;

XOR_OP:result=a^b;

endcase

endmodule:and_xor

//`end_keywords

圖5-5顯示了示例5-5中的RTL模型綜合結(jié)果,如上一節(jié)前面所述,綜合創(chuàng)建的實(shí)現(xiàn)可能受到多個(gè)因素的影響,包括:目標(biāo)設(shè)備、與運(yùn)算符一起使用的任何其他運(yùn)算符或編程語(yǔ)句、使用的綜合編譯器以及指定的綜合選項(xiàng)和約束。

圖5-5:示例5-5的綜合結(jié)果:按位AND和OR運(yùn)算

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110077 -

按位運(yùn)算符

+關(guān)注

關(guān)注

0文章

3瀏覽量

4785

原文標(biāo)題:(按)位XNOR

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

C語(yǔ)言運(yùn)算符的使用方法

【跟我學(xué)單片機(jī)C語(yǔ)言】詳解運(yùn)算符和表達(dá)式的位運(yùn)算符

2.7 python運(yùn)算符

STM32位運(yùn)算按位與運(yùn)算符學(xué)習(xí)記錄

數(shù)字硬件建模SystemVerilog-歸約運(yùn)算符

第八課 運(yùn)算符和表達(dá)式(位運(yùn)算符)

移位運(yùn)算符的應(yīng)用實(shí)例講解

python運(yùn)算符是什么

SystemVerilog-運(yùn)算符/表達(dá)式規(guī)則

條件(三元)運(yùn)算符

什么是按位運(yùn)算符

Python中運(yùn)算符介紹

C語(yǔ)言中位運(yùn)算符的基礎(chǔ)用法

數(shù)字硬件建模SystemVerilog-按位運(yùn)算符

數(shù)字硬件建模SystemVerilog-按位運(yùn)算符

評(píng)論