1.

CAN2.0A 是CAN協議的PART A部分,此部分定義了11bit的標識區 。

CAN2.0B 是CAN協議的擴展部分,也叫PART B,定義了29bit的標識區,其它部分與CAN2.0A一樣。

CANOpen是基于CAN協議的應用層協議,可以理解為用戶層,即規定了用戶、軟件、網絡終端等之間用來進行信息交換的約定!而CAN定義了物理層和數據鏈路層,而CANOpen與DeviceNet一樣,只定義了OSI模型的第七層。

CAN2.0A/B是CAN標準的兩個部分,只要CAN芯片支持CAN2.0B,則都可以兼容通訊,而CANOpen是上層協議,建立在CAN的基礎上的

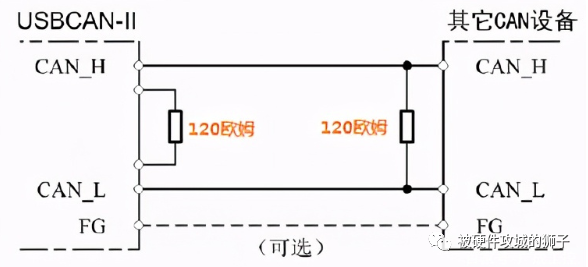

實驗中發現多數情況下,總線上接入一個120歐姆電阻可以實現1米左右的CAN總線通信。但在此還是要說明下,CAN總線上L和H之間的阻值在64歐姆左右才是穩定的狀態,也就是說要在兩個終端上各掛一個120歐姆電阻。如果線路上有5臺CAN總線設備,那么相對位置在中間的三臺設備是不能掛載120歐姆電阻的。

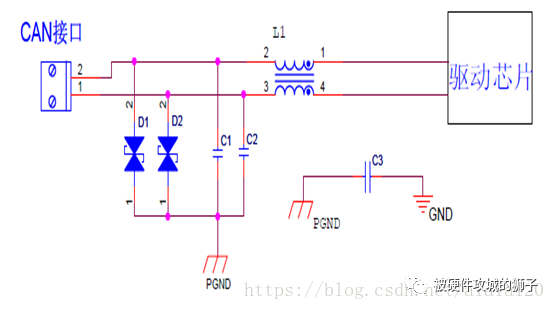

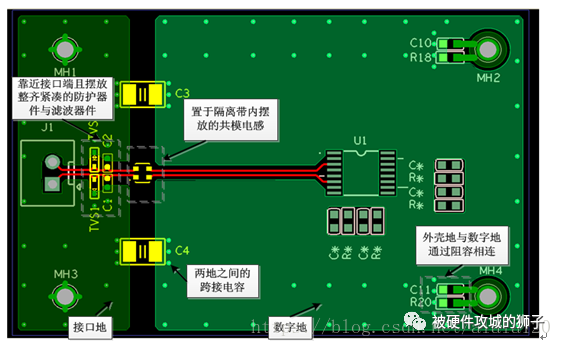

2.接口地

CAN接口電路的 EMC設計方案(工業)_alala120的博客-CSDN博客_can接口電路

3.千兆網和百兆網

千兆網絡變壓器有四路繞組,也就是四對線,對應網口1/2、3/6、4/5、7/8都要使用,每對速率是250M,收發兩個方向的載波頻率不一樣,網絡傳輸時可以同時收發;

百兆變壓器是兩路繞組,只用1/2和3/6,收發各用一對線,速率為100M。

4.芯片算力(TOPS, GOPS, MOPS)與精度(int8,int16)

TOPS

TOPS是Tera Operations Per Second的縮寫,1TOPS代表處理器每秒鐘可進行一萬億次(10^12)操作。

與此對應的還有GOPS(Giga Operations Per Second),MOPS(Million Operation Per Second)算力單位。1GOPS代表處理器每秒鐘可進行十億次(109)操作,1MOPS代表處理器每秒鐘可進行一百萬次(106)操作。TOPS同GOPS與MOPS可以換算,都代表每秒鐘能處理的次數,單位不同而已。

FLOPS

是“每秒所執行的浮點運算次數”(floating-point operations per second)的縮寫。它常被用來估算電腦的執行效能,尤其是在使用到大量浮點運算的科學計算領域中。正因為FLOPS字尾的那個S,代表秒,而不是復數,所以不能省略掉。

在這里所謂的“浮點運算”,實際上包括了所有涉及小數的運算。這類運算在某類應用軟件中常常出現,而它們也比整數運算更花時間。現今大部分的處理器中,都有一個專門用來處理浮點運算的“浮點運算器”(FPU)。也因此FLOPS所量測的,實際上就是FPU的執行速度。而最常用來測量FLOPS的基準程式(benchmark)之一,就是Linpack。

FLOPS換算

一個MFLOPS(megaFLOPS)等于每秒一百萬(=10^6)次的浮點運算,

一個GFLOPS(gigaFLOPS)等于每秒十億(=10^9)次的浮點運算,

一個TFLOPS(teraFLOPS)等于每秒一萬億(=10^12)次的浮點運算,(1太拉)

一個PFLOPS(petaFLOPS)等于每秒一千萬億(=10^15)次的浮點運算,

MIPS(Million Instructions Per Second)

字面理解為百萬條指令/秒,即每秒執行百萬級指令數。這是衡量CPU速度的一個指標。像是一個Intel 80386 電腦可以每秒處理3百萬到5百萬機器語言指令,既我們可以說80386是3到5MIPS的CPU。MIPS只是衡量CPU性能的指標。

DMIPS(Dhrystone Million Instructions executed Per Second)

Dhrystone是測量處理器運算能力的最常見基準程序之一,常用于處理器的整型運算性能的測量。Dhrystone是一種整數運算測試程序。

4.高低速的匹配

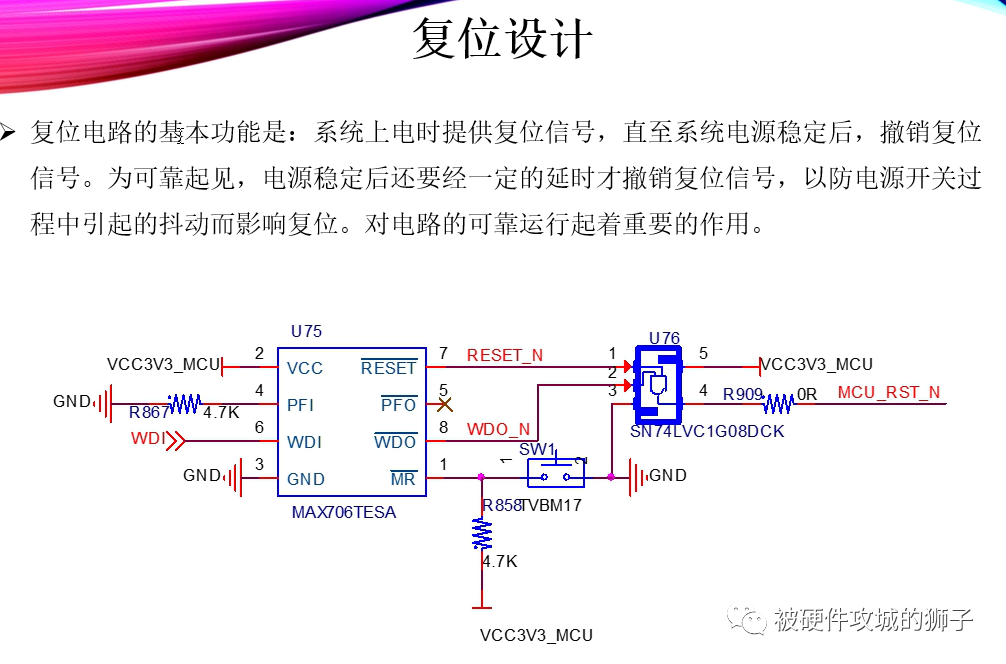

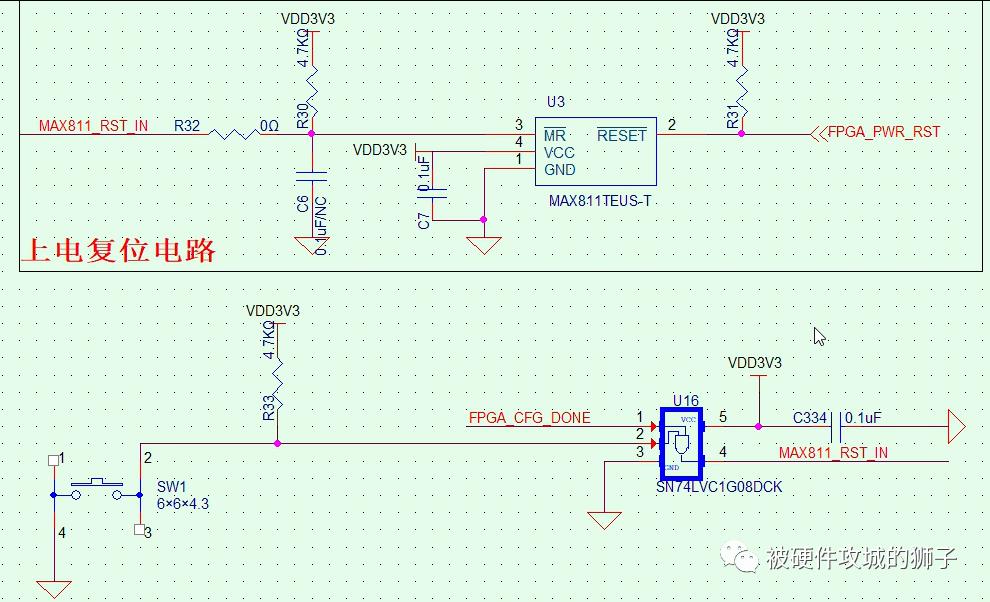

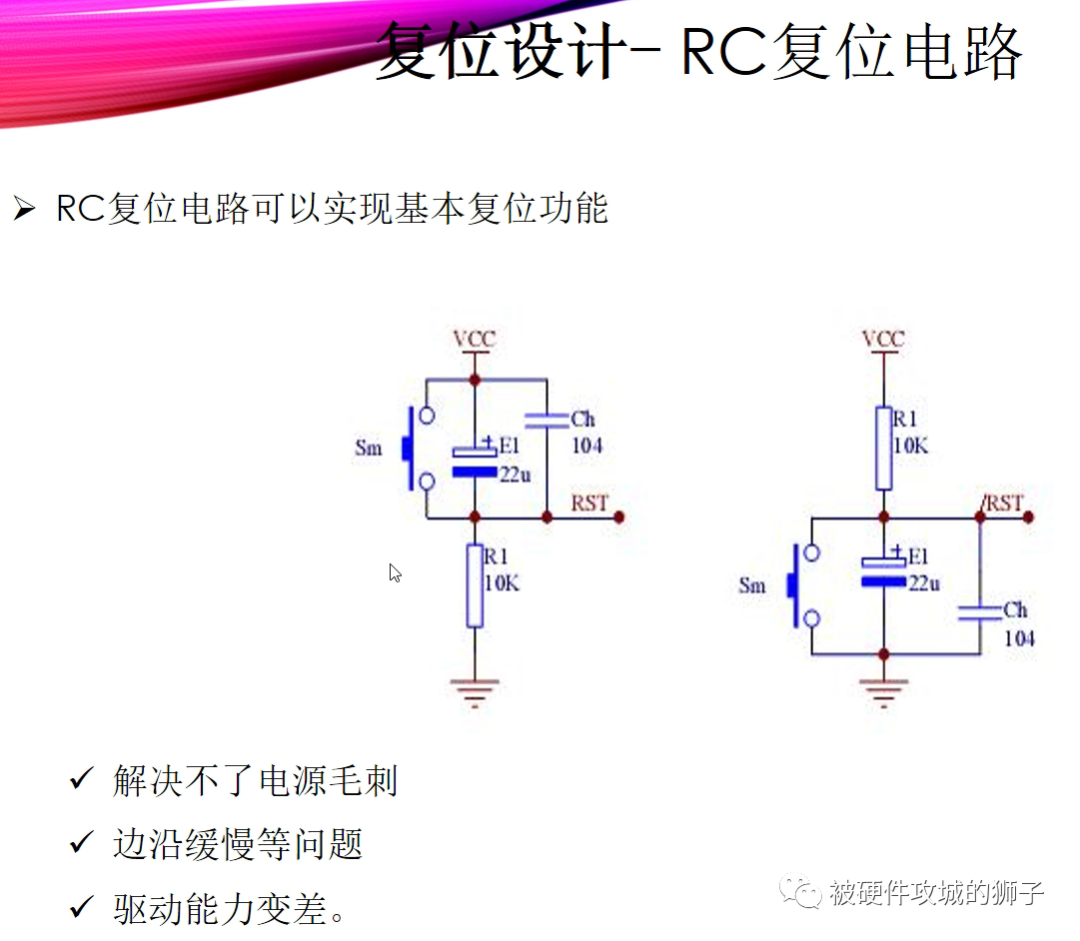

5.復位電路

復位電路能讓微機系統中電路穩定可靠工作,復位電路最主要的功能是上電復位。一般來說,微機電路正常工作供電電源差不多需要5V±5%,也就是4.75~5.25V。而微機電路是時序數字電路,必須要有一個穩定的時鐘信號,所以在電源上電的時候,只有達到VCC大雨4.75V并且小于5.25V還有晶體振蕩器穩定工作條件時,復位信號才會撤除,接著微機電路工作。

復位電路在在上電以及復位的時候,控制CPU的復位狀態:讓CPU一直是復位狀態,不會讓一上電或者剛復位完就開始工作,這樣可以防止CPU發出錯誤的指令以及執行錯誤操作,還能夠讓電磁兼容性能提高。

所以復位電路是很重要的,很多地方都要設計到復位電路,所以選擇復位電路,會影響到整個系統工作的可靠性。

無論用戶使用哪種類型的單片機,總要涉及到單片機復位電路的設計。而單片機復位電路設計的好壞,直接影響到整個系統工作的可靠性,復位電路作為一個比較重要的原件,建議購買正規企業的產品。

6.斬波(Chopper)

:將直流電變為另一固定電壓或可調電壓的直流電。

也稱為直流--直流變換器(DC/DC Converter)。

一般指直接將直流電變為另一直流電,不包括直流—交流—直流。

直流斬波電路(DC Chopper)種類:

6種基本斬波電路:降壓斬波電路、升壓斬波電路、 升降壓斬波電路、Cuk斬波電路、Sepic斬波電路和Zeta斬波電路。

復合斬波電路——不同結構基本斬波電路組合。

多相多重斬波電路——相同結構基本斬波電路組合。

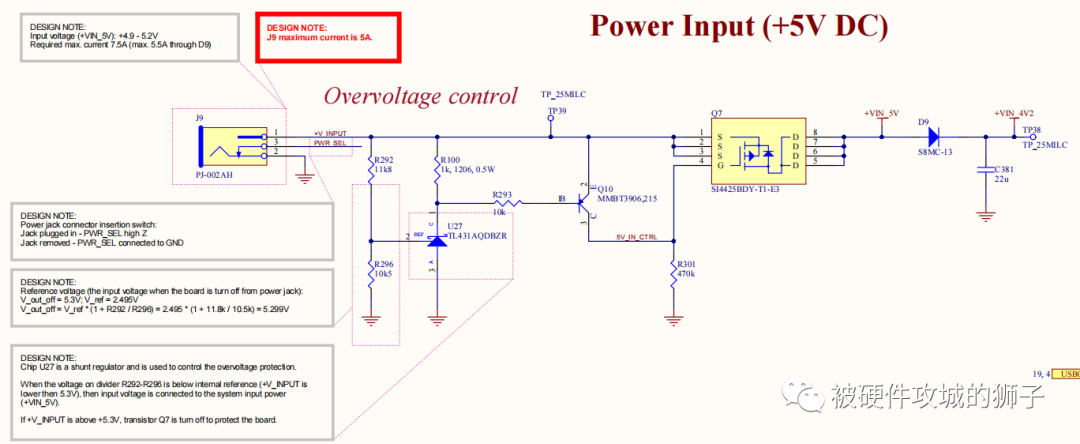

7.TL431的應用電路

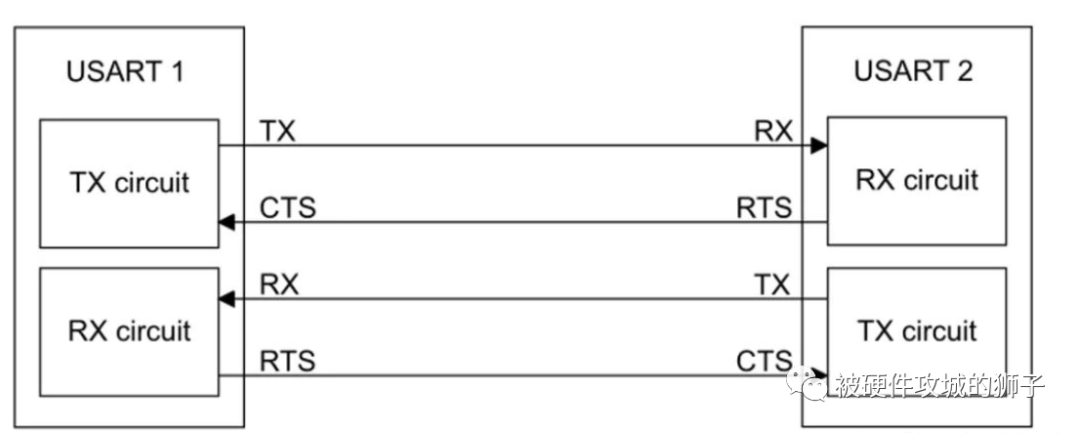

8.串口的硬件流控

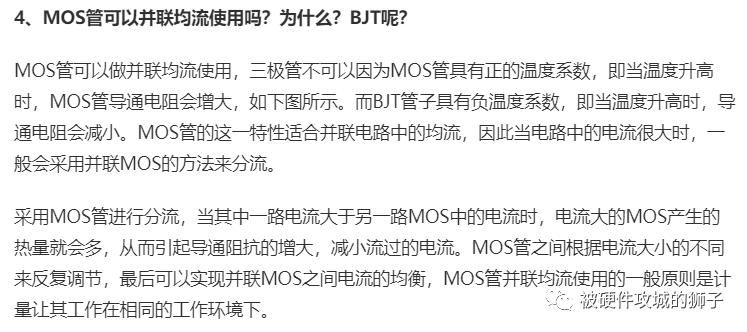

9.mos管 BJT的并聯使用

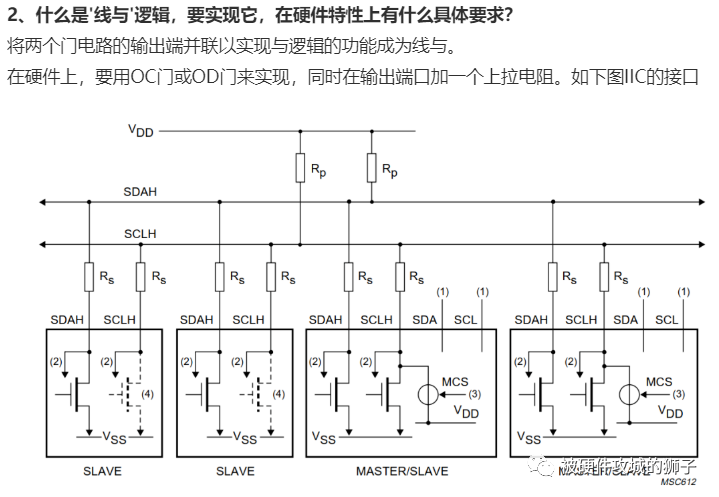

10.線與邏輯

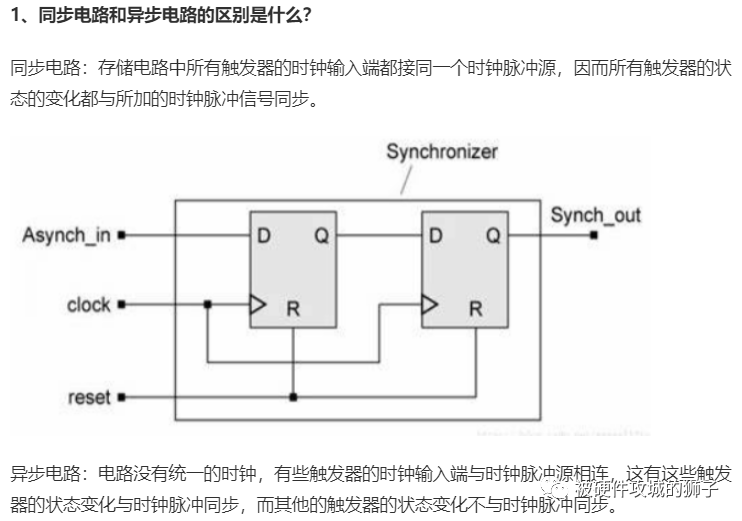

11.同步 異步電路

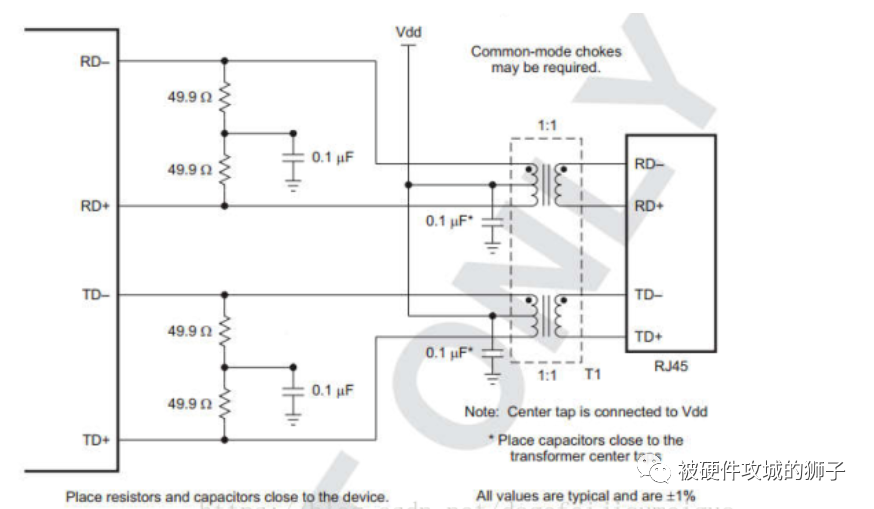

12.電流型和電壓型PHY

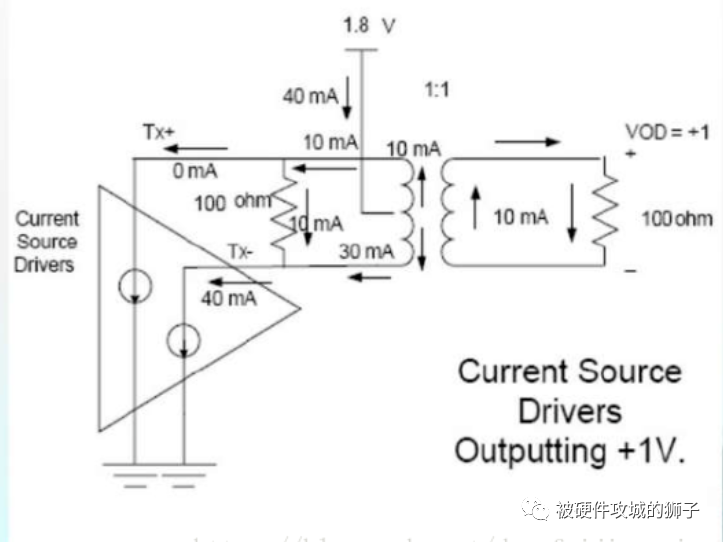

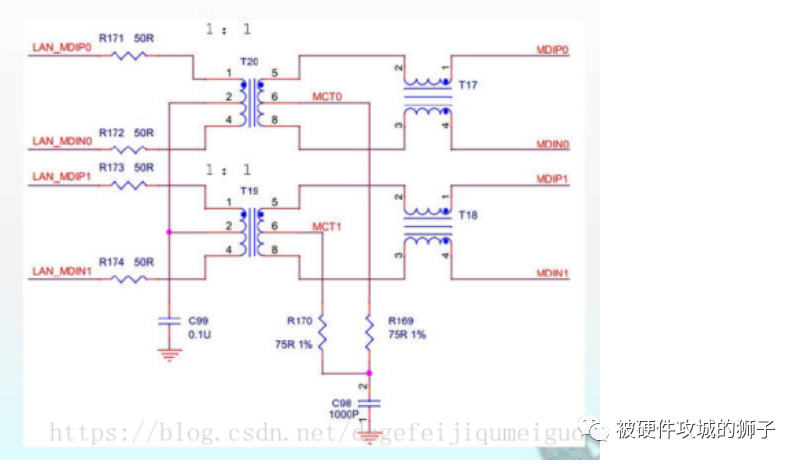

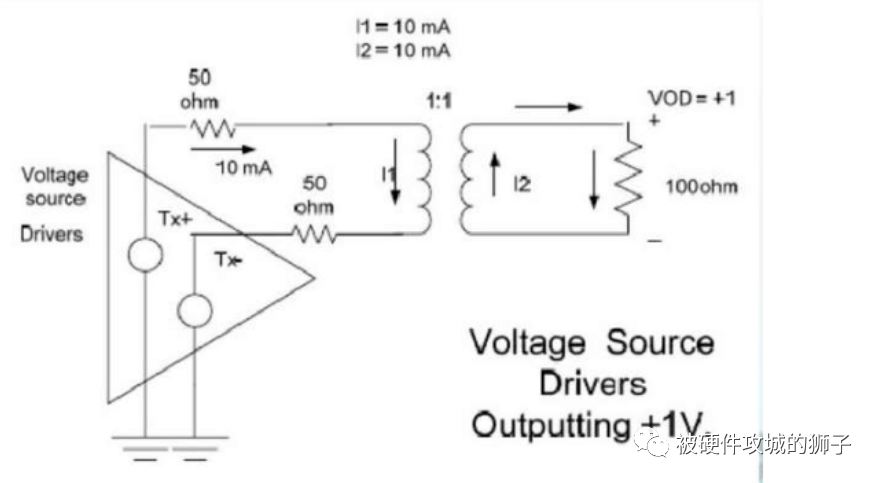

接法根據PHY是電壓型還是電流型確定,電流型PHY,需要偏置電壓,49.9端接到電源,電壓型過電容端接到地----Trent

網口PHY芯片對于TX與RX的驅動方式有電壓驅動和電流驅動之分。最簡單的一個識別方式就是看其推薦原理圖,

如果網絡變壓器的中心抽頭需要提供一個VCC(3.3V、2.5V等等,下同)電源的就是電流驅動,

如果是直接加一個對地電容就可以的就是電壓驅動。

13.CAN和485的通信速率

1、從數據傳輸速率上看,CAN總線的最大通信速率為1Mbps,不算特別大和以太網相比,但也還可以。相比而言,485總線的最大通信速率為10Mbps,是CAN總線的十倍。在通信速率上,485總線顯然是更占優勢的。

2、從數據傳輸距離上看,在無中繼的情況下,CAN總線的通信距離可達10千米,而485總線則在1千米上下徘徊,這點CAN總線完勝。

3、在通信安全穩定性上看,CAN總線和485總線都采用了差分電壓傳輸信號的原理,但CAN總線自帶CRC檢錯機制,其通信的延遲性也更低,所以CAN總線的通信安全穩定性更高。

4、在可連接節點設備數上,CAN總線理論上可以連接110個節點,485總線可以連接128個節點,雙方差距不大,485總線小勝。

13.SPI和IIC的通信速率

1、定義不同:

SPI:SPI是串行外設接口(Serial Peripheral Interface)的縮寫,是一種高速的,全雙工,同步的通信總線,并且在芯片的管腳上只占用四根線,節約了芯片的管腳,同時為PCB的布局上節省空間,提供方便,正是出于這種簡單易用的特性,越來越多的芯片集成了這種通信協議,比如AT91RM9200。

I2C :I2C 總線支持任何IC 生產過程(NMOS CMOS、雙極性)。兩線――串行數據(SDA)和串行時鐘 (SCL)線在連接到總線的器件間傳遞信息。每個器件都有一個唯一的地址識別(無論是微控制器——MCU、LCD 驅動器、存儲器或鍵盤接口),而且都可以作為一個發送器或接收器(由器件的功能決定)。很明顯,LCD 驅動器只是一個接收器,而存儲器則既可以接收又可以發送數據。除了發送器和接收器外器件在執行數 據傳輸時也可以被看作是主機或從機(見表1)。主機是初始化總線的數據傳輸并產生允許傳輸的時鐘信號 的器件。此時,任何被尋址的器件都被認為是從機。.

2、I2C總線是半雙工,2根線SCL SDA;SPI總線實現全雙工,4根線SCK CS MOSI MISO。

3、I2C是多主機總線,通過SDA上的地址信息來鎖定從設備;SPI只有一個主設備,主設備通過CS片選來確定從設備。

4、I2C總線傳輸速度100Kbps----4Mbps;SPI可達30Mbps以上。

5、I2C高電平時SDA下降沿標志傳輸開始,上升沿標志傳輸結束;SPI總線CS拉低標志傳輸開始,CS拉高標志傳輸結束。

6、I2C總線讀寫時序比較固定統一,設備驅動編寫方便。SPI總線不同從設備datasheet來實現讀寫,相對復雜一些。

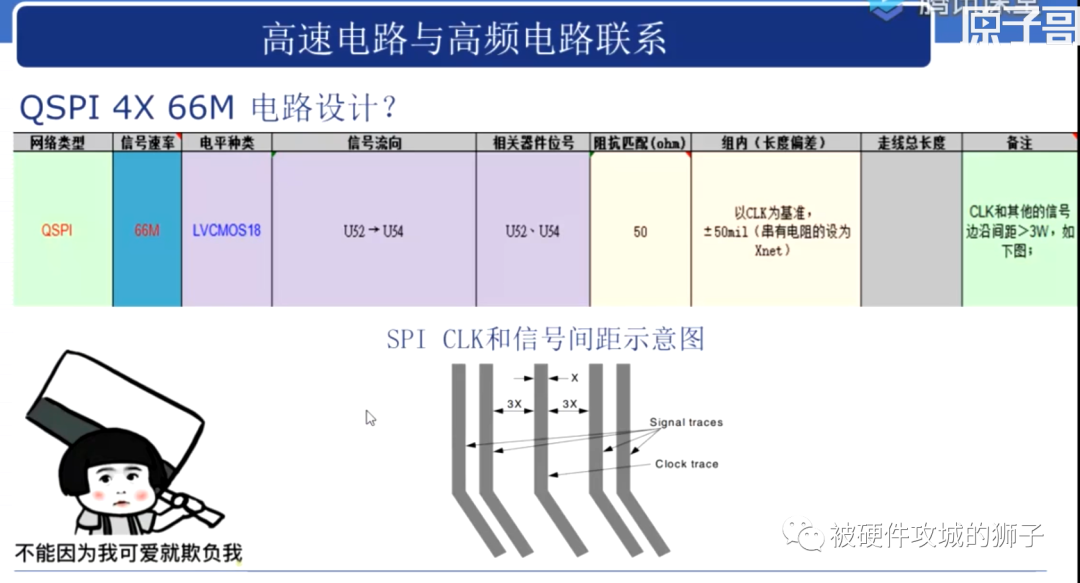

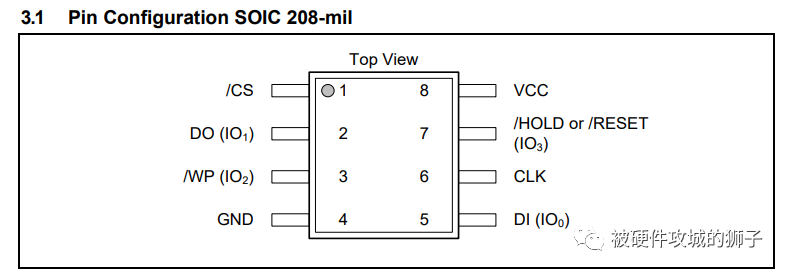

QSPI(Quad SPI,四倍速率SPI總線,6線制)

eg:W25Q128BV的Quad SPI Flash存儲器的Top View如下圖所示

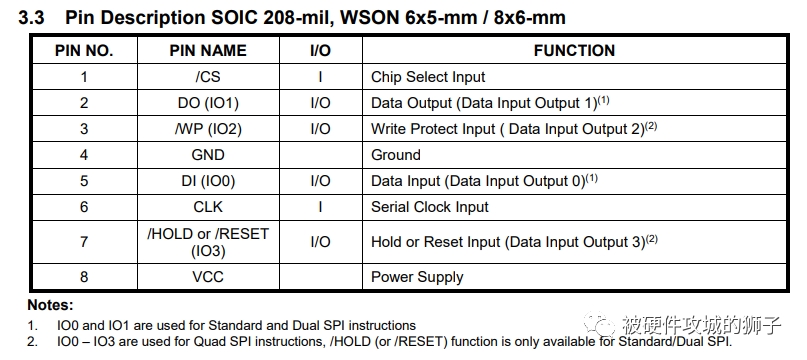

這塊芯片一共有8個有用的管腳,其每個管腳的功能定義如下圖所示

由上圖可知2號管腳DO(IO1),3號管腳 /WP(IO2),5號管腳DI(IO0)以及7號管腳/HOLD(IO3)均為雙向IO口,所以在編寫Verilog代碼的時候要把它們定義為inout類型,inout類型的信號既可以做輸出也可以作為輸入,具體在代碼里面如何處理后文會有介紹。

QSPI Flash每個引腳的詳細描述如下:

1、Chip Select(/CS)

片選信號Chip Select(/CS)的作用是使能或者不使能設備的操作,當CS為高時,表示設備未被選中,串行數據輸出線(DO或IO0,IO1,IO2,IO3)均處于高阻態,當CS為低時,表示設備被選中,FPGA可以給QSPI Flash發送數據或從QSPI Flash接收數據。

2、串行數據輸入信號DI以及串行輸出信號DO

W25Q128BV支持標準SPI協議,雙線SPI(Dual SPI)協議與四線SPI(Quad SPI)協議。標準的SPI協議在串行時鐘信號(SCLK)的上升沿把串行輸入信號DI上的數據存入QSPI Flash中,在串行時鐘信號(SCLK)的下降沿把QSPI Flash中的數據串行化通過單向的DO引腳輸出。而在Dual SPI與Quad SPI中,DI與DO均為雙向信號(既可以作為輸入,也可以作為輸出)。

3、Write Project(/WP)

寫保護信號的作用是防止QSPI Flash的狀態寄存器被寫入錯誤的數據,WP信號低電平有效,但是當狀態寄存器2的QE位被置1時,WP信號失去寫保護功能,它變成Quad SPI的一個雙向數據傳輸信號。

4、HOLD(/HOLD)

HOLD信號的作用是暫停QSPI Flash的操作。當HOLD信號為低,并且CS也為低時,串行輸出信號DO將處于高阻態,串行輸入信號DI與串行時鐘信號SCLK將被QSPI Flash忽略。當HOLD拉高以后,QSPI Flash的讀寫操作能繼續進行。當多個SPI設備共享同一組SPI總線相同的信號的時候,可以通過HOLD來切換信號的流向。和WP信號一樣,當當狀態寄存器2的QE位被置1時,HOLD信號失去保持功能,它也變成Quad SPI的一個雙向數據傳輸信號。

5、串行時鐘線

串行時鐘線用來提供串行輸入輸出操作的時鐘。

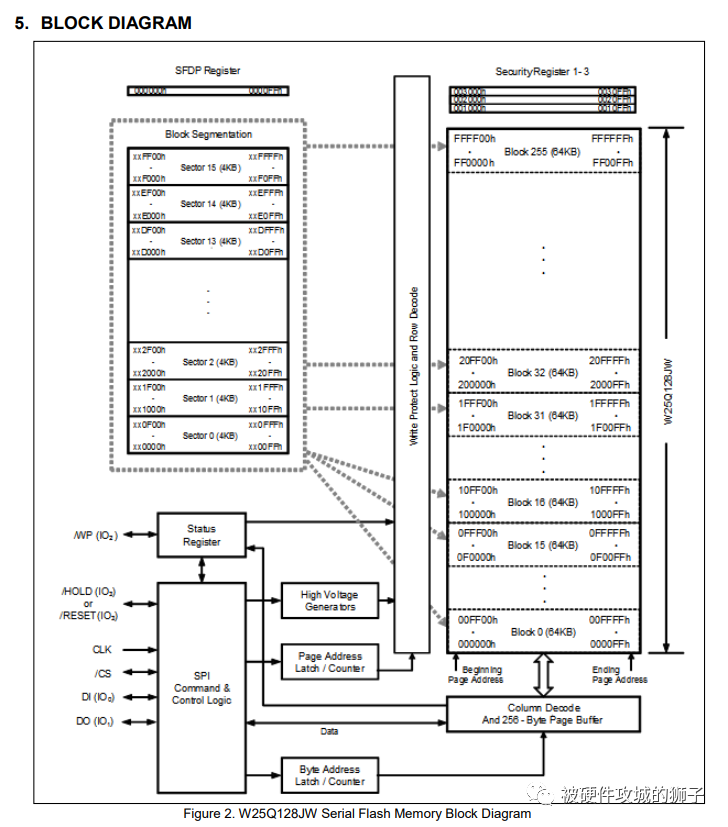

W25Q128BV的內部結構框圖如下圖所示

更多詳細的內容請閱讀W25Q128BV的芯片手冊。由于本文要進行4線SPI的操作,但QSPI Flash默認的操作模式是標準單線SPI模式,所以在每次進行4線SPI操作的時候一定要先把狀態寄存器2的QE位(倒數第2位)置1,然后才能進行QSPI操作。

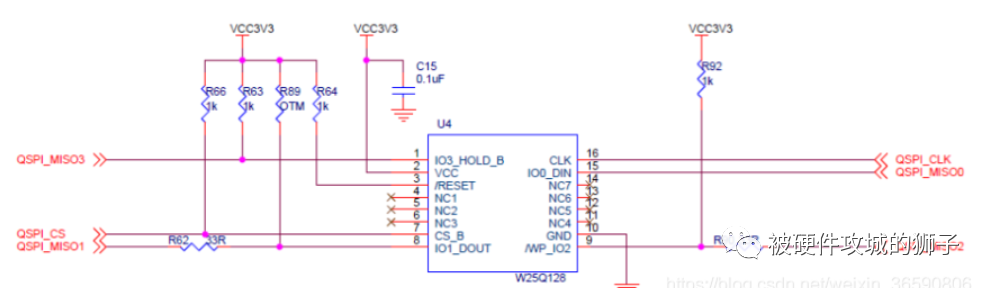

最后介紹一下我的開發板上QSPI Flash硬件原理圖如下圖所示:

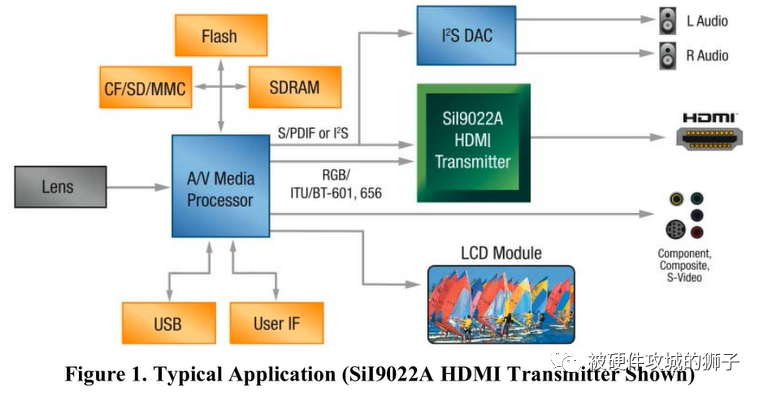

14.HDMI

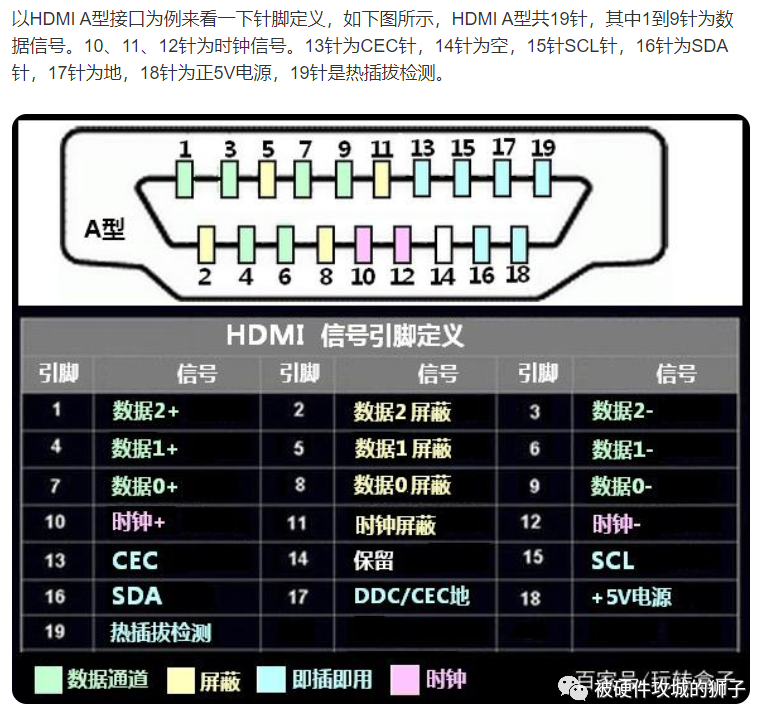

其中

1-9 都是TMDS數據傳輸實際上用到的引腳,分為0,1,2三組

10-12 為TMDS時鐘信號,如當前Video Timing為480p@60Hz(Htotal:800,Vtotal:525),則TMDS clock = 800x525x60 = 25.2MHz。TMDS clock就像是對像素的打包,一個clock分別在三個Channel傳輸一個像素的R、G、B(8bit)信號。

13 為CEC(consumer electronic control)類似一種擴展的HDMI功能,供廠家自己定制HDMI消息,(比如說你有一臺sony的DVD與TV,兩者用HDMI線接上,如果你用TV的遙控器可以控制DVD,另DVD執行某種功能,那么該功能的命令信號就是通過TV與DVD間的CEC引腳傳輸的)

14 為保留引腳,未使用(或者也可以為CEC提供多一個引腳)

15-16 為I2C引腳,用于DDC(Display Data Channel,主要用于EDID與HDCP的傳輸)傳輸,具體可以查看。在HDMI的流程中,DDC通信幾乎是最先做的(前有Hotplug),因為HDMI的主從兩個設備需要通過DDC來獲得他們對方設備的EDID,從而得到各種信息,并且通過比較timming以確定以后送出來的timming為最合適的

17 為接地引腳

18 為5v的AC引腳

19 為Hotplug(熱拔插)引腳(用于監測HDMI設備有沒有存在,如果存在(Hotplug為high)那么可以通過DDC去讀EDID),HDMI有規定在HDMI 5vAC斷電時source device可以讀reciever device的EDID,也就是需要Hotplug為High。其中有兩種Hotplug相關的情況會導致HDMI被識別為DVI:

Hotplug為High,不過EDID并沒有準備好,那么信號源設備會由于無法讀到EDID而認為接收設備為DVI,這樣會導致HDMI有圖像無聲的問題。

Hotplug為Low,也會導致信號源無法讀到EDID而認為接收設備為DVI,從而導致HDMI有圖無聲

在TV這種有多個HDMI通道的情況下,有時會在多個HDMI通道進行切換,切換后HDMI通道應當先初始化,即先把Hotplug拉低,通知HDMI source device之前所用的EDID已經改變,需要重新讀取,那么source device在Hotplug被拉高的時候會去讀取新的EDID,但是拉低這個過程至少需要100ms,否則source device有可能不會去讀取新的EDID,從而輸出DVI信號

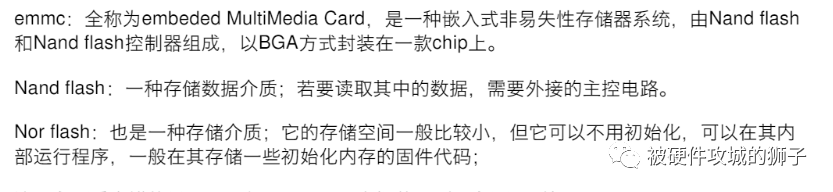

15.emmc nand nor FLASH

存儲顆粒與外部控制器

flash內部有一個存儲顆粒,只跟flash本身功率有關。如nand,nor flash.

nandflash中的存儲顆粒也有技術差異,如sic、mico

這些東西是內部封裝起來的用干存儲的內核,對外編程的接口還需要一個外部控制器。

我們買到的flash芯片,其實是內部的flash存儲顆粒+外部封裝的控制器來構成的。即,對外是外部控制器,對內是存儲顆粒。

存儲顆粒決定容量大小,外部用什么控制器訪問,不過大部分的內部存儲顆粒都是一樣的。全世界做這個的也沒有幾家。

外部控制器會影響讀寫速度,就比如U盤讀寫速度的差異。存儲顆粒也會影響。

常見的flash對比

像EMMC、SD、MMC.SPIFLASH、NANDFLASH內部都一樣用的是NAND存儲顆粒,對外通過不同的控制器實現了不同的協議,所以外部可以通過不同的協議去訪問它。

如SPI FLASH內部是NAND存儲顆粒,對外的接口是用SPI協議開放出來的。主芯片若想與SPI FLASH對接,只需要其支持SPIFLASH就可以了

NAND FLASH是最原始的NAND接口,其本身有它的時序特征,時序會非常復雜。這樣就會非常麻煩,對干芯片來說還需要一個NAND控制器,接口復雜。

如果沒有專門的NAND控制器,有SPI控制器就行了。而市面上的大部分芯片都有SPLFLASH。

NANDFLASH現在用的越來越少了,因為NANDFLASH的兼容性不好。EMMC是無縫替換,不同容量的封裝兼容,換一個容量或廠家什么都不用改

接口簡單就是SPL FLASH最大的優勢

內置還是外接Flash

但是如stm32SPI內置的成本非常高,內置1M或2MFlsah的成本比內置512k或256k的成本高出一倍不止。內置Flash的成本可能會占到整個MCU成本的一半甚至更多。

所以現在很多的單片機都傾向干外掛一個SPLFlash,外掛的就特別便宜。買一個8M只有幾塊錢,板載16M的不到20塊。內置的話就不可想象。

如果需求是512M或者1G以上的這種大容量的建議選擇EMMC(板載)及SD(TF卡)。現在的手機都逐漸由外擴的SD(tf卡)轉為EMMC(板載)了。

使用難度

很多MCU或CPU在需要外擴一個8M、16M、32M、64M這個容量的外部存儲器時,選擇SPIFlash是很好的。成本低

NANDFlash控制器是最老的,EMMC、SD等都比NANDFlash更新一些,更好一些。

flash選擇總結

要大還要板載,就選EMMC

要大還要靈活,就用SD

要小、成本低,就用SPIFlash

更小,只有幾個字節,就用EEPROM

NANDFlash被淘汰的原因

NANDFLASH現在用的越來越少了,因為NANDFLASH的兼容性不好。

EMMC的優勢

比如iphone的64g 128g版本,用的就是EMMC方案

如EMMC是有接口規范的,很多東西是在接口內部實現,不需要用戶去實現。

主CPU通過EMMC接口對不同的存儲顆粒實現了共通管控,用的是8g還是16g的卡是直接自動識別的

EMMC在封裝上本身就是pin to pin的,要換不同容量、不同廠家的芯片,什么都不用改,可以無縫替換。

所以EMMC的涉及是更加優秀的,比直接使用NANDFlash要好很多

eMMC存儲器其實就是在原有內害存儲器的其礎上,額外加了一個控制芯片,最后再以統一的方式封裝,并預留一個標準接,類似臺式機里面的硬盤。eMMC從協議版本上分為eMMC4.41,eMMC 4.5eMMC.5.0,eMMC5.1,不同的版本,速度區別很大。通常16GB以上容量,需要選用高版本型號,否則在大批量數據讀寫的時候會很慢。16GB或以下容量,選用低版本速度自然會慢一些,但相對于高版本不是特明顯。這好比坐火車,短途旅行高鐵跟動車差別不大一樣,但是長途旅行,總的時間就差別很明顯。

芯片PCB上的引腳分153ball和169ball,其實這2種引腳是兼容的,后者比前者多出的16個Pin是空腳(其實真正有用的也就10多個引腳,其他的都是為了固定芯片用的,芯片內部沒有接線),沒有任何信號定義。

有經驗的工程師,在PCBLayout時,會在PCB上預留最大尺寸的絲印為止,焊盤會畫成169ball的,這樣就可以兼容153ball的芯片。

DDR3和eMMC區別

1. 存儲性質不同;

2. 存儲容量不同;

3. 運行速度不同;

4. 用途不同。

具體區別如下:

1、存儲性質不同:eMMC是非易失性存儲器,不論在通電或斷電狀態下,數據都是可以存儲的,而DDR3內存是易失性存儲器,斷電同時,數據即丟失。

2、存儲容量不同:eMMC的存儲容量要比DDR3內存大3-4倍,常見有32G,而DDR3內存容量相對較小,常見有2-8G。

3、運行速度不同:DDR3內存運行速度要比eMMC快得多。

4、用途不同:eMMC主要用于數據存儲,而DDR3內存主要用于數據運算。eMMC 主要是針對手機或平板電腦等產品的內嵌式存儲器標準規格。用來提供標準接口并管理閃存。在手機或平板電腦中,DDR3內存可稱之為運行內存,而eMMC可稱之為存儲內存。

ADD eMMC:

eMMC(Embedded Multi Media Card)也是一種使用兼容MMC協議的芯片,和MMC的區別如其名,eMMC經常被用于嵌入式環境中,而MMC一般用作外接設備的標準。eMMC = NAND flash + 控制器 + 標準封裝接口。

很多卡內部的存儲設備用的都是NAND flash, 單純nand flash和這些卡的區別,就是nand flash是上面這些卡內部真正的存儲單元。

emmc的特點:

1. 有四種尺寸:BGA153-11.5x13, BGA169-12x16, 12x18, 14x18

一般長相如圖:

2. eMMC內部可以很好對MLC/TLC進行管理,有ECC除錯機制,區塊管理,平均默寫存儲區塊技術,低功耗管理等。

3. 廠商不必再為NAND Flash的大小/規格重新設計硬件了,直接用eMMC就好了。

在以前,每次NAND技術換代的時候,手機客戶端也要重新設計,手機制造商需要選擇新的與NAND flash匹配的soc芯片,而soc廠商一般要針對這款NAND flash,重新設計soc芯片(主要是內部的nand flash ccontroller),這種方式十分麻煩。

在推出emmc后,soc廠商只需要在芯片上加上一個可以與mmc標準通信的控制器(一般叫做sdmmc controller/sd controller),這個控制器可以支持某種/某幾種emmc標準。同時emmc芯片封裝好NAND flash,向外也提供一個統一的emmc 接口(如emmc 4.3/4.4),此時只要給soc芯片選定好一個emmc接口,連上二者即可通信了。

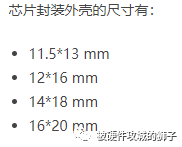

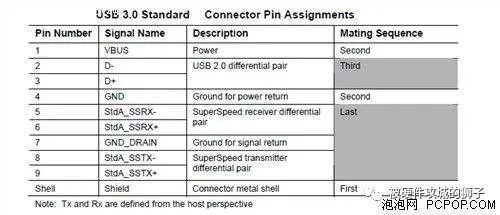

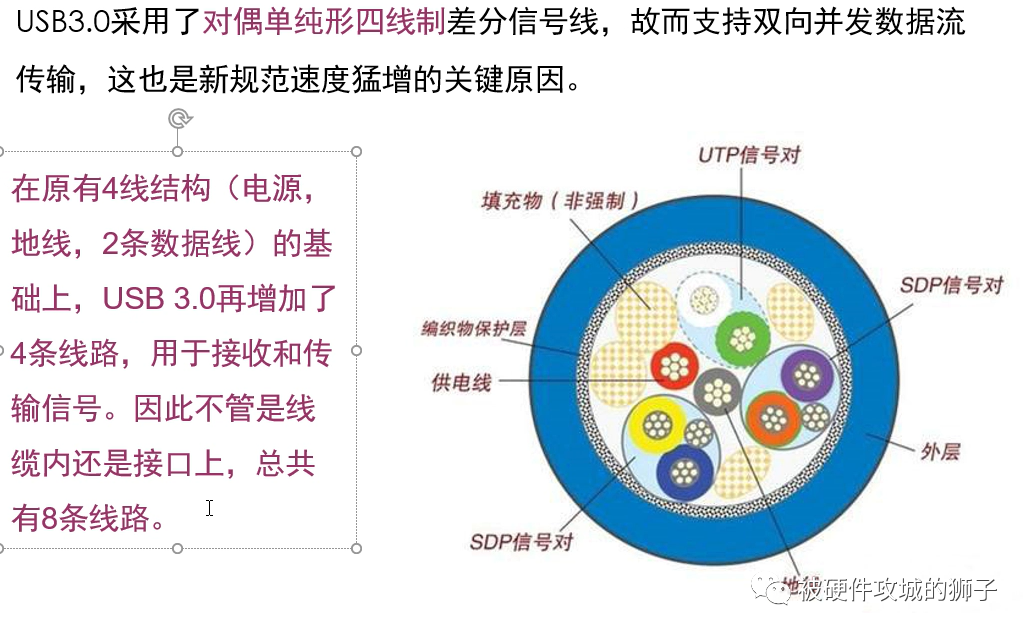

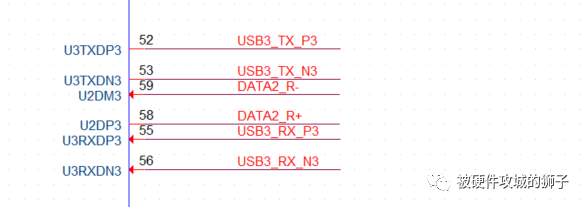

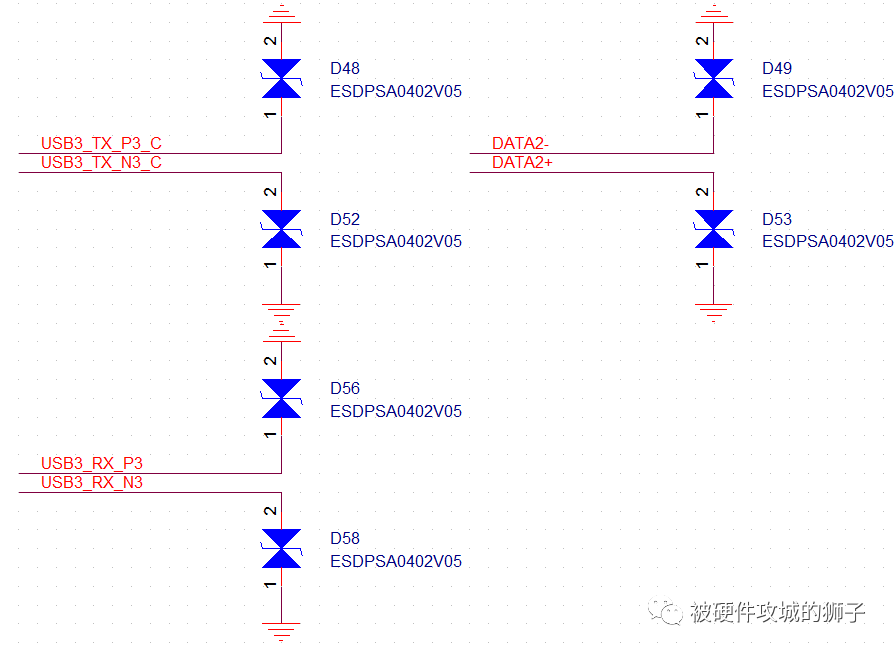

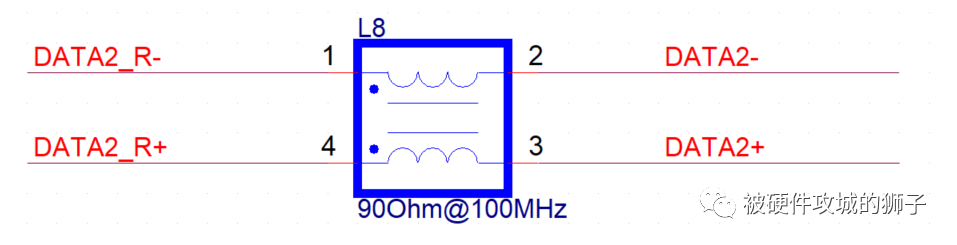

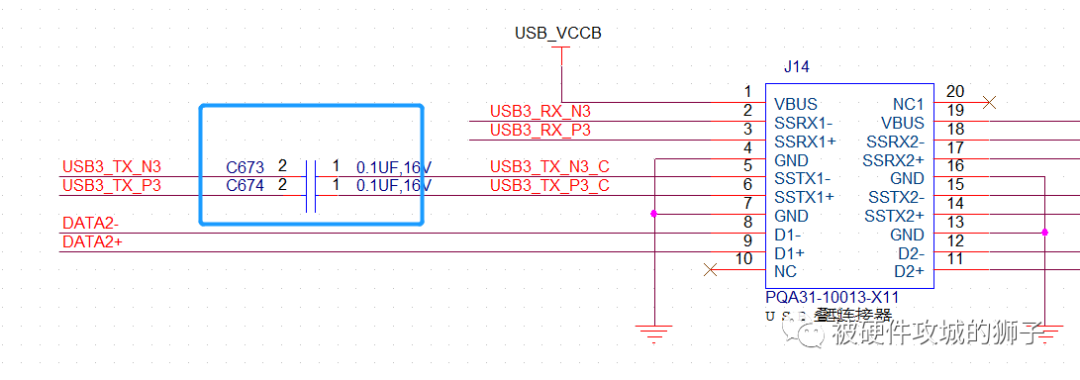

16.USB3.0

對于USB來說,每一個通道有兩個差分對,一個用于發送,一個用于接收。PCIe也一樣是全雙工通信,會同時發送和接收數據,通道的定義也符合這一點。下圖為USB Type-C母座,共有兩個通道,即高速通道0和高速通道1,我們稱之為Lane 0 Adapter和Lane 1 Adapter。即通道0適配器和通道1適配器 。這里的適配器可以當做信號轉換器來理解。USB是全雙工通信,每一個通道有兩個差分對,一個用于發送,一個用于接收。

usb3.0的信號里面既有3.0的通道,又有2.0的通道,要把2.0的信號通道引到其中的通道上,3.0的接口才可以向下兼容2.0的設備。

17:AC耦合電容擺放注意事項:

1,按照design guideline 要求放置

2,沒有guideline,如果是IC 到IC,請靠近接收端放置

3,如果是IC 到連接器,請靠近連接器放置

4,盡可能選擇小的封裝尺寸,減小阻抗不連續

PCIE信號:每一路差分信號均要串一個0.1uF的電容,放置位置為靠近驅動端即TX端;

USB3.0信號;0.1uF靠近TX;

SATA:為了避免信號反射及過壓保護防止芯片被損壞,0.01uF電容放在靠近連接器端。

https://suisuisi.blog.csdn.net/article/details/88849228?spm=1001.2101.3001.6650.1&utm_medium=distribute.pc_relevant.none-task-blog-2%7Edefault%7ECTRLIST%7Edefault-1-88849228-blog-95973132.pc_relevant_default&depth_1-utm_source=distribute.pc_relevant.none-task-blog-2%7Edefault%7ECTRLIST%7Edefault-1-88849228-blog-95973132.pc_relevant_default&utm_relevant_index=2

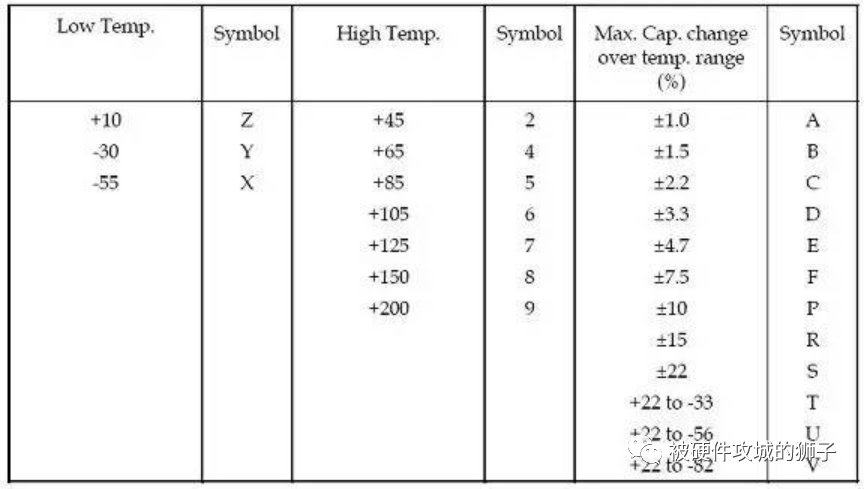

18:5R、X7R、Y5V、Z5U之間的區別是什么?

區別主要還在于溫度范圍和容值隨溫度的變化特性上。下表提示了這些代號的含義。

19:MIPI GSML 的并轉串,串轉并方案

CSI和DSI是MIPI標準的一種,因為MIPI在移動領域應用范圍太廣了,各種外圍設備都可以用它來傳輸信息,所以,MIPI聯盟給不同的外設接口定義了版本名,CSI是for Camera的,DSI是for Display的。而且這些標準不單包括物理層的時序定義,還包括上層的傳輸協議/數據處理協議和應用層協議。

MIPI信號是串行的!!!!之所以是串行,在phy層的時候進行了并轉串的轉換,再進行傳輸!并且雖然它最多有4條數據通道,但是是相對獨立的,不是并行傳輸的意思。

MIPI信號是并行的,cpu也是并行的,所以可以一對一連接,但是并行傳輸的排線距離較短,不適合長距離傳輸,這種情況下,適合用同軸電纜傳輸,同軸電纜都是串行數據,所以通過GMSL轉成串行的,Cpu端再通過串轉并芯片轉成并行數據!

應用:

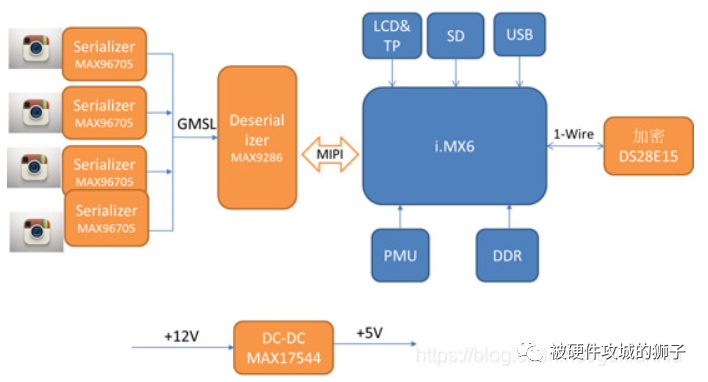

1.方案介紹:

1)基于美信MAX9286全數字接口芯片,提供高達1.5Gbps的數字傳輸

2)通過同軸線纜傳輸

3)提供4路720P高清影像輸入,LVDS/ Parallel RGB高清影像輸出

4)2D/3D全景環視集成ADAS功能,超高性價比

5)主處理器基于HI3519芯片

方框圖如下:

GMSL(Gigabit MultimediaSerial Link),是串行器和解串器構成的傳輸鏈路,基于LVDS傳輸,很多域控制器上直接使用GMSL4通道解串器,同時支持4路攝像頭數據傳入,例如在AVM(Around ViewMonitor)中,需要多路攝像輸入。

LVDS是現在常用的高速傳輸方式,是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps甚至幾Gbps的速率傳輸,其低壓幅和低電流驅動輸出實現了低噪聲和低功耗。

差分技術:LVDS、MLVDS、CML、LVPECL

SerDes信號層采用的LVDS工作在155Mbps~1.25Gbps之間,而CML(電流模式信號)在600Mbps和10+ Gbps,

因此現在SerDes一般使用CML。但是LVDS和CML信號可以互通,但要有外接電阻做電平轉換。

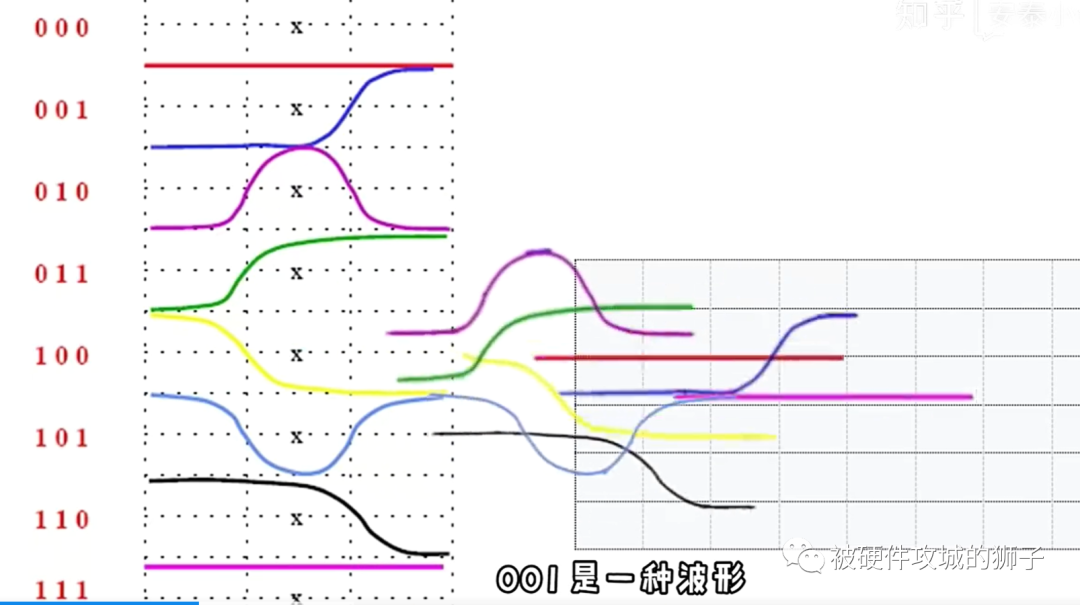

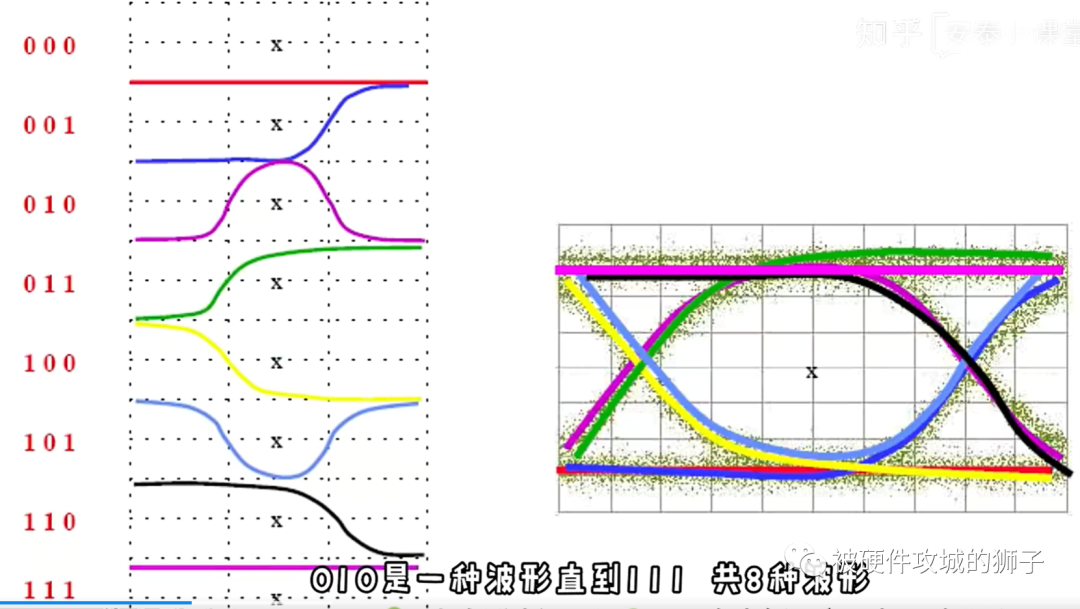

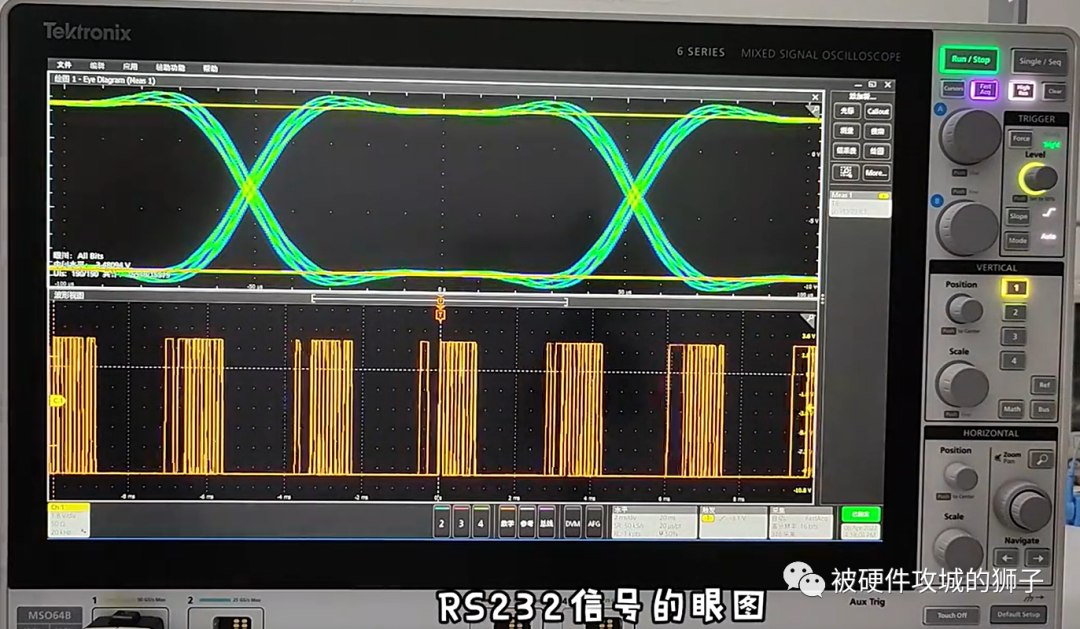

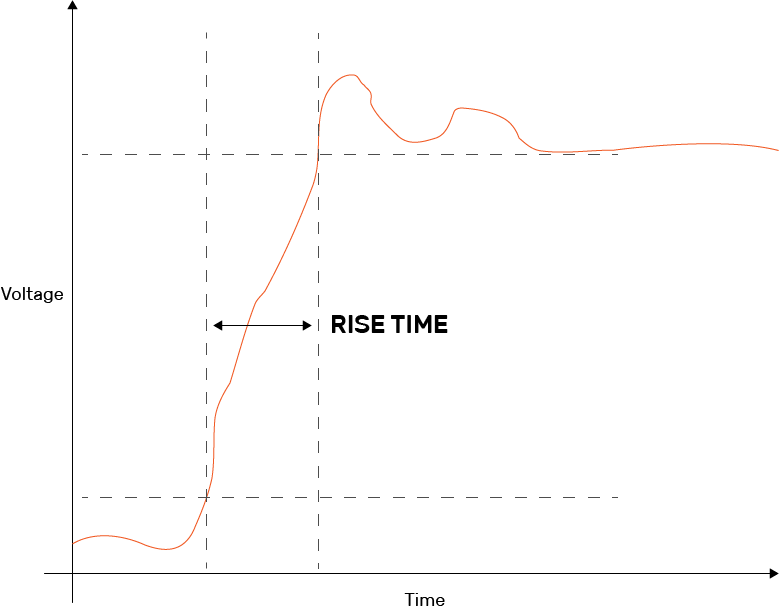

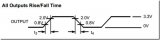

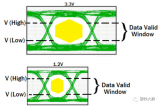

20:用示波器測試眼圖有三種方法,根據測試效果和對示波器的要求來分,如下:

1,示波器帶有眼圖測量功能。這種情況下,直接打開功能,儀器自動測試,自動恢復時鐘并測試出張開度、抖動等參數,效果最好,而且是定量測試

2,示波器不帶眼圖測量功能,測試的信號包括數據線和時鐘線。這時可以使用時鐘信號作為觸發信號來測試數據信號的眼圖。這種方法也很不錯,可以比較準確的看出眼圖形狀,誤差小,操作簡單

3,示波器不帶眼圖測量功能,信號只有一根數據線,這個時候是不能做眼圖測試的,如果一定要測也只能定性測試,方法是:使用示波器上升沿觸發信號,并將觸發點遷移到不能移動為止,觸發示波器,打開波形保持,可以大致看信號的眼圖,但是結果會偏好,至少抖動會偏小

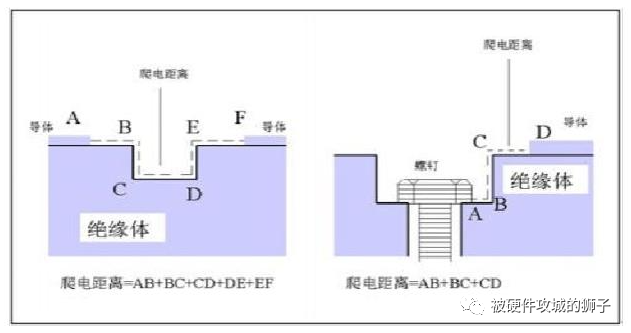

21:什么叫爬電距離

爬電距離是沿絕緣表面測得的兩個導電零部件之間或導電零部件與設備防護界面之間的最短路徑。即在不同的使用情況下,由于導體周圍的絕緣材料被電極化,導致絕緣材料呈現帶電現象。

UL、CSA和VDE安全標準強調了爬電距離的安全要求,這是為了防止器件間或器件和地之間打火從而威脅到人身安全。

絕緣子爬電距離是指絕緣子正常承載運行電壓的兩部件間沿絕緣表面的最短距離或最短距離的和。

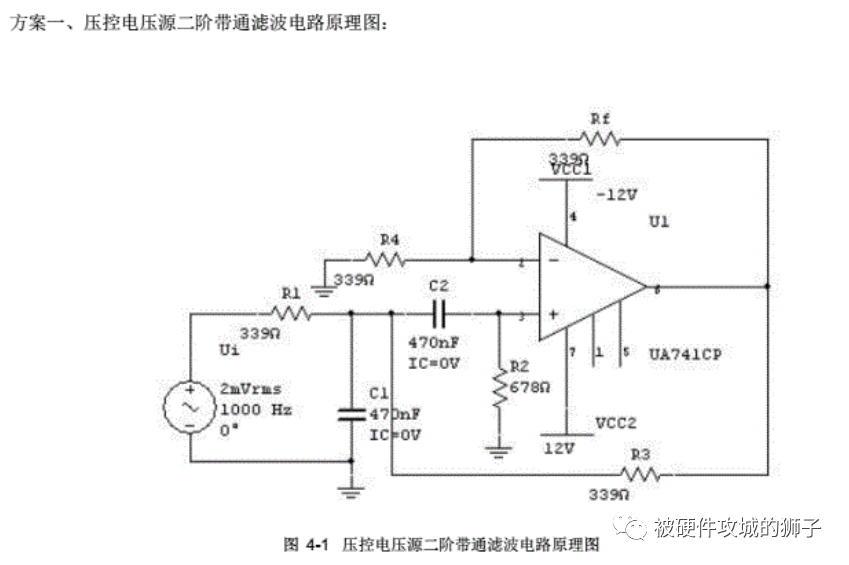

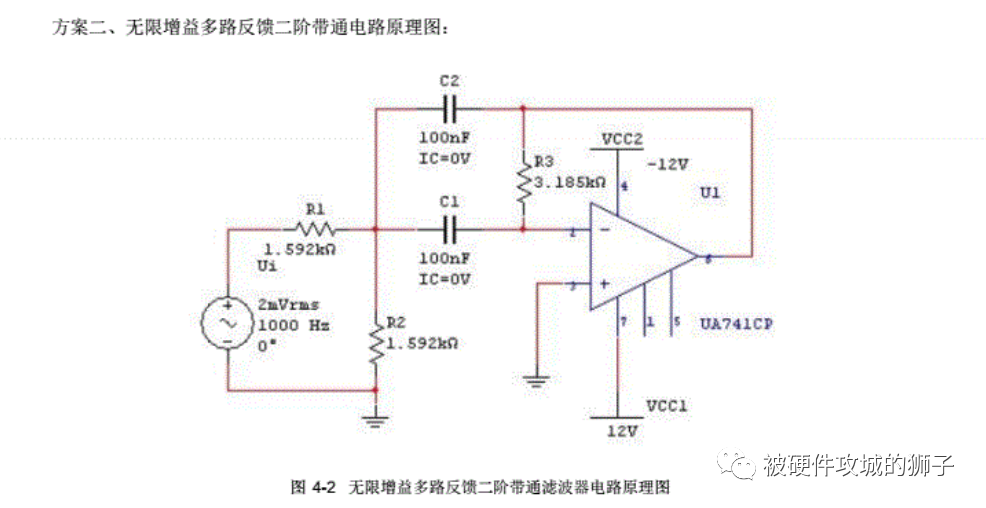

22.帶通濾波器形式

23.pcb布線線寬與電流的關系;過孔與過流的關系

推薦走線寬度:正常10mil=0.0254mm ,若兩線間距太小,考慮8mil=0.2mm

推薦過孔:信號過孔0.3mm/0.5mm,電源地過孔0.3mm/0.6mm

1 英寸=1000 密耳(mil)

10mil=0.254mm

一、關于PCB走線的過流能力

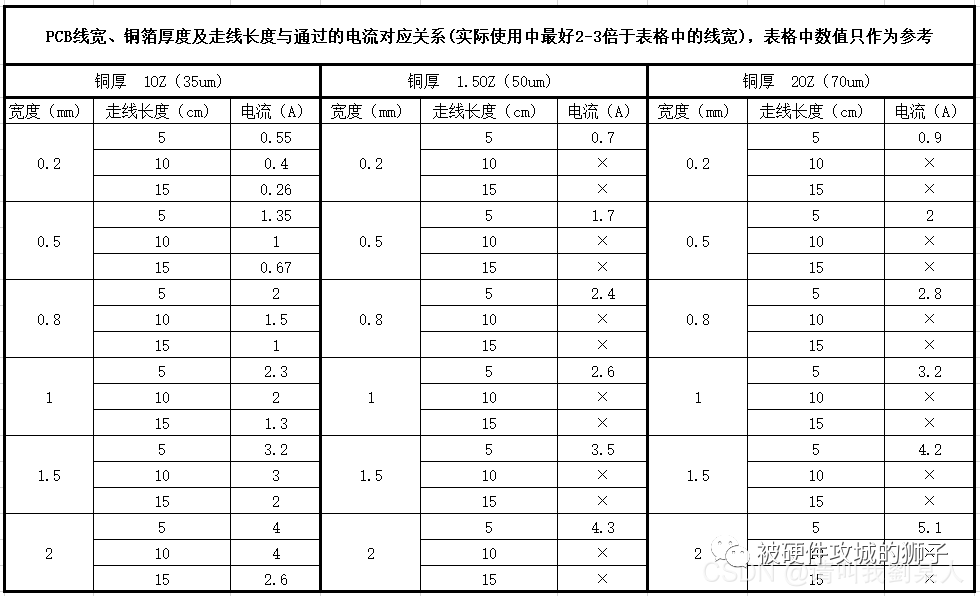

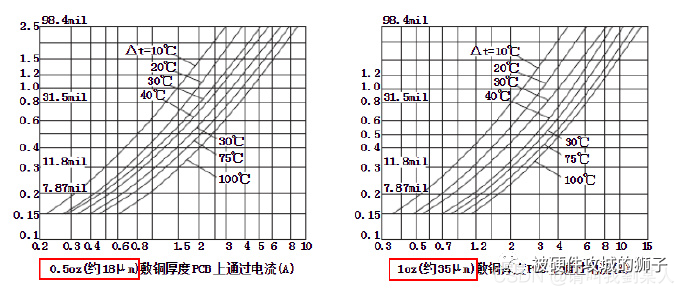

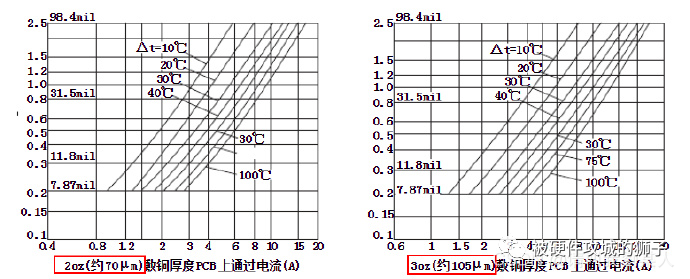

PCB走線的過流能力都與哪些因素有關,目前考慮有走線線寬、銅箔厚度、走線長度、溫升這些因素

下面我們逐個分析及整體分析

1、走線線寬、銅箔厚度以及走線長度對過流能力的影響

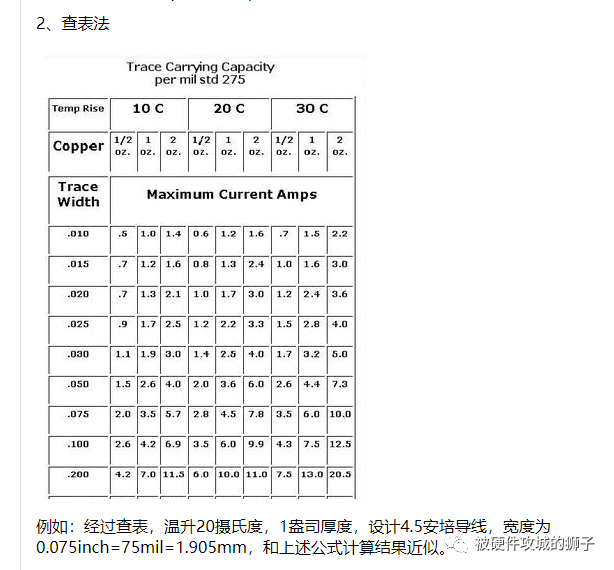

通過網上的收集及整理,統計出了下面的表格,大家做參考即可。

2、通過的電流大小引起的溫升

這里可能有個誤區,很多人看成,溫升越高,通過的電流越大;實際是通過的電流大小不同,引起的溫升。

3、PCB線寬與載流能力計算公式

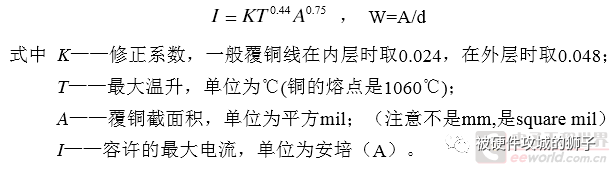

載流能力計算:

先由I、K、T導出A,再由A、d導出W(單位為mil)。常用PCB的覆銅厚度d=1.378mil,加厚的可查表或咨詢廠家得到,溫升T取10攝氏度。

4、舉例子

例子1:

弱電DC4V,需要2A的電流,銅厚為1OZ,走線長度為7cm,我們走線時應該如何走線?

(1)、根據表格查詢,我們大概能估算出,選用的線寬要在1.5mm左右;

(2)、根據計算公式,溫升選用10攝氏度(要根據實際情況),可知W=0.7mm,取值2-3倍,也大概為1.5mm。

例子2:

強電AC220V,需要5A的電流,銅厚為2OZ,走線長度為3cm,我們應該如何走線?

(1)、根據表格查詢,我們大概能估算出,選用的線寬要在3mm左右;

(2)、根據計算公式,溫升選用10攝氏度(要根據實際情況),可知W=1.17mm,取值2-3倍,也大概為2.3mm。

二、關于PCB過孔的過流能力

關于過孔的過流能力介紹,大家參考一下一搏科技的文章介紹:

PCB過孔的孔徑大小對通流的影響

那我們還是拿上面的例子做介紹:

例子1:

弱電DC4V,需要2A的電流,銅厚為1OZ,走線長度為7cm,如果打過孔,應該打幾個,過孔是多大?

我們可選用20mil的過孔孔徑,打3-5個。

例子2:

強電AC220V,需要5A的電流,銅厚為2OZ,走線長度為3cm,如果打過孔,應該打幾個,過孔是多大?

我們可選用20mil的過孔孔徑,打8-10個。

三、是否有其他增大過流能力方法?

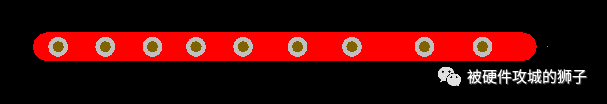

1、正反面走線,如下圖所示:

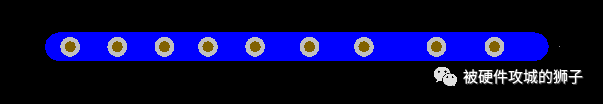

2、添加銅箔鍍錫(sloder層),如下圖所示:

3、短接線方式:

手里沒有合適的圖就不貼了,其實也很簡單,就是用硅膠線或者其他線材代替PCB走線,因為硅膠線的過流能力更好,1.5mm2的硅膠線都可以用在10A的線路上。

————————————————

24.pcb布線關鍵信號是包地

在PCB Layout中對于關鍵信號線兩邊是否地包,在平時做設計的時候經常看到有人糾結于包地這個問題。可能受到板子大小的限制,又聽說包地能讓信號屏蔽更好,于是在重要的時鐘線差分信號兩邊都盡量畫上兩條細細的地線。實際上這種做法不一定就對信號有好處,有時可能還會適得其反帶來更多問題。

包地主要的作用是為了減小串擾。那么除了包地以外還有什么方法能減小串擾呢?增加信號間距還有讓信號和參考平面緊耦合。如果是多層板,減小參考平面和信號層的距離,可以更好的控制阻抗的同時能夠讓信號與參考平面緊耦合,減少信號對附近信號的干擾。在通過增加信號線間距就能很好的減小串擾,這時候對信號包地的作用就不明顯了。尤其是空間比較小的情況下,加一根細細的地線,相當于在兩根信號線之間又增加了一根信號線,而地線上面并不是我們認為的一個“干凈”的地,它會把其他信號的干擾又傳導到這這里來。所以有空間包地 還不如拉開兩信號之前的距離。

有人說,不光要加地線包地還要在地線上多打地孔。當然,這樣的效果會比較好。但是既然能打地孔說明包地線寬最小也要有十幾個mil了,再加上線間距,原有兩根信號線間距都足夠滿足4W了,這樣串擾本身就很小了,去掉包地信號也不會增加多少串擾。

如果是兩層板,沒有參考平面,那么重要信號的包地就很重要。包地線的寬度要盡量寬,最好在信號寬度的兩倍以上。同時多打過孔,過孔間距小于信號線上信號波長1/5。

在一些非高頻的單片機布線中,晶振、串口、重要的信號線、中斷信號等進行包地處理。

25.固件的作用

固件是更靠近硬件的軟件代碼,起到一個管理硬件狀態以實現標準化接口的作用。BIOS無非是主要和用戶操作系統內核打交道的固件,別的硬件的固件則各自和對應的驅動打交道。這些固件的作用用一句話來總結就是“將硬件的功能提供給對應驅動進行管理和調用”。

固件的存在主要是為了隔離用戶軟件和硬件各自的實現細節,方便對接。固件是硬件廠商設計制作的,它更“了解”硬件,于是它能夠將硬件的具體細節隱藏掉,讓用戶操作系統只需要去按照一個標準化的方式去操作硬件。驅動那邊則負責隱藏用戶操作系統的細節,使得硬件能夠不需要了解操作系統的細節就能運作,從而讓硬件能夠簡單地跨平臺工作。

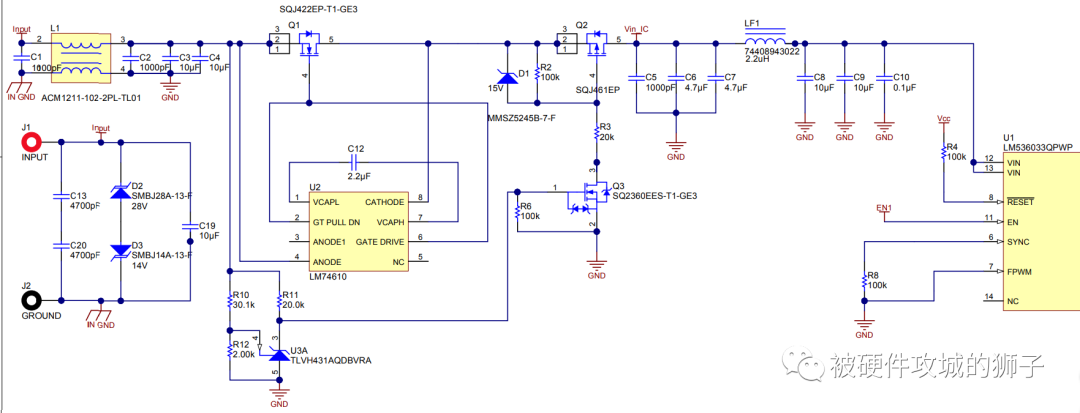

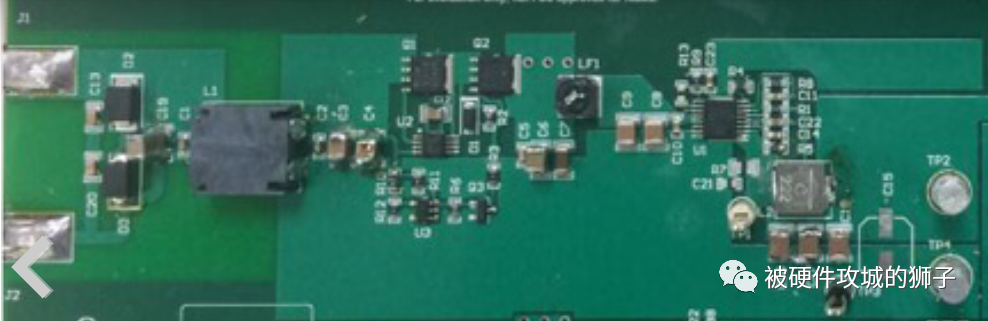

26.基于TL431精密穩壓源的過壓保護電路

27

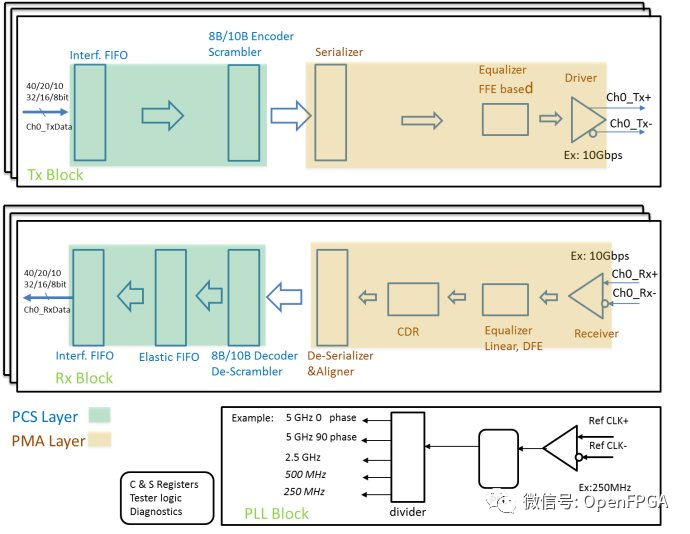

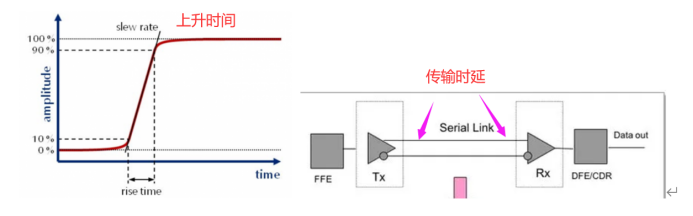

SerDes技術

Figure2.1 Basic Blocks of a typical SerDes

圖中藍色背景子模塊為PCS層,是標準的可綜合CMOS數字邏輯,可以硬邏輯實現,也可以使用FPGA軟邏輯實現,相對比較容易被理解。褐色背景的子模塊是PMA層,是數模混合CML/CMOS電路,是理解SerDes區別于并行接口的關鍵,也是本文要討論的內容。

發送方向(Tx)信號的流向: FPGA軟邏輯(fabric)送過來的并行信號,通過接口FIFO(InterfaceFIFO),送給8B/10B編碼器(8B/10B encoder)或擾碼器(scambler),以避免數據含有過長連0或者連1。之后送給串行器(Serializer)進行并->串轉換。串行數據經過均衡器(equalizer)調理,由驅動器(driver)發送出去。

接收方向(Rx)信號的流向,外部串行信號由線性均衡器(Linear Equalizer)或DFE (DecisionFeedback Equalizer判決反饋均衡)結構均衡器調理,去除一部分確定性抖動(Deterministic jitter)。CDR從數據中恢復出采樣時鐘,經解串器變為對齊的并行信號。8B/10B解碼器(8B/10B decoder)或解擾器(de-scambler)完成解碼或者解擾。如果是異步時鐘系統(plesio-synchronous system),在用戶FIFO之前還應該有彈性FIFO來補償頻差。

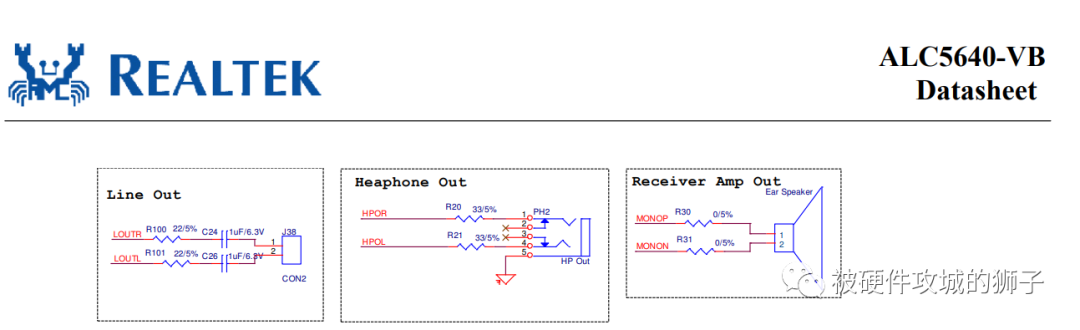

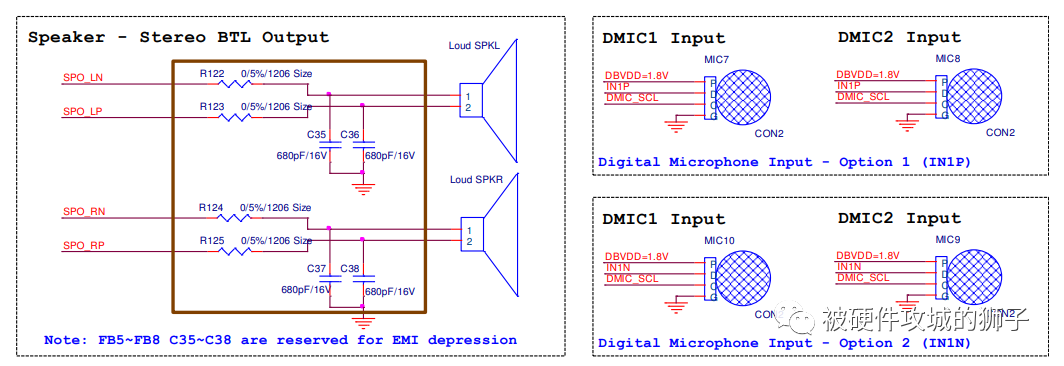

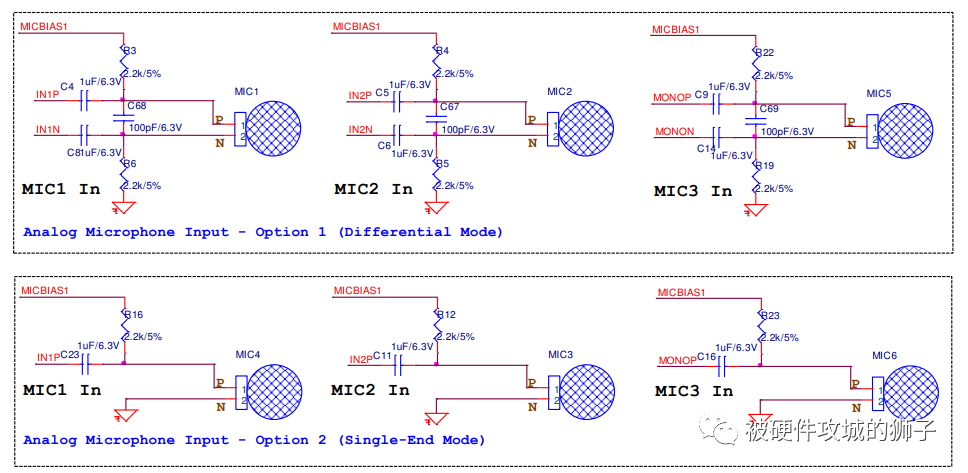

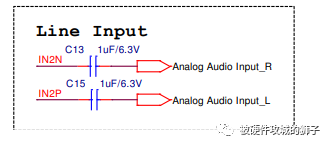

28.聲卡中的 line in line out

Mic:用來連接麥克風。

Line Out:用來輸出未經放大芯片放大的模擬音頻信號。

Speaket Out(現在通常和Line Out合為一個插孔):用來輸出經放大芯片放大的模擬音頻信號。

Line In/Out傳遞的是只經過A/D或D/A芯片轉換后的信號,還原度較高;而Speaker Out輸出的是經放大芯片(例如TDA1517P)放大過的信號,聲音會產生一定失真(但很小,人耳幾乎不能察覺)。

如果音箱上有放大電路,則連接到Line Out,如果沒有放大電路則連接到Speaker Out。無源音箱如果連接到Line Out上可能出現聲音很小或是聲音不正常的現象。音頻線line in接口,用于接駁主板背板的聲卡口的聲音輸出,連線后可用于顯示器自帶的喇叭播放。

LINE-IN是線路輸入的意思。它主要是用于通過專用的線路進行錄音或轉錄的,一般在MP3上見的較多,如果MP3上有這個功能,說明這個MP3支持CD直錄,可以直接把CD轉錄為MP3。

LINE-IN是直錄線,是錄音用的,其功能是把該線一端插入其它器具的音頻輸出端(比如聲卡、MP3、隨身聽、CD機等連接音箱、耳機的插孔),一端插入到MP3播放器的LINE-IN孔中,然后直接把聲音錄入到你的MP3播放器了。比如,你和你的朋友都有MP3播放器,而他的機子里有一首歌你非常喜歡,你想把它拷到自己的機子里,可是一時有找不到電腦可以傳輸,又或者你們有人忘了帶數據線,不過恰好你的機子帶有LINE-IN功能(也就是直錄功能),恰好你還把LINE-in線帶在身上,于是你就可以把你喜歡的歌錄到你的機子上了。因為直錄是把聲音播放器播放的聲音直接錄入到機子里,避免了外部環境的干擾,因此效果要比外錄的效果好很多。

如果你有設備有Line Out接口,又想在電腦上錄制外部音源的聲音,則可以將其連接到聲卡的Line In接口上(通過一根兩頭都是3.5mm音頻插頭的連接線)。如果只用電腦輸出聲音的話,建議在系統音量控制中將其他不用的通道設置為靜音(尤其是麥克風通道),這樣可以降低系統背景噪聲。

line in是音頻輸入口,line out是音頻輸出口,音箱應該接在 line out口上

line in: 主要指聲音(信號)輸出.line out: 主要指聲音(信號)輸入.是否可以接音像要看你的audio芯片(聲卡芯片)是什么規格。Line out 可以接2.1音箱.

音頻接口:音頻模擬接口包括Line In、Mic In、Speak Out和Lille Out。Line In接口主要用于將磁帶上的音頻信號傳輸到電腦硬盤中保存成文件,它通常與另一端設備的Line Out接口相連。Mic In接口主要用于連接麥克風,因而能實現錄音、在線聊天。Speak Out和Line Out兩個接口都能將聲卡處理后的模擬信號輸出到音箱等音頻設備上,很多主板會將它們合二為一,即在機箱背面只能看到一個音頻輸出接口。

29.趨膚效應

定義:當導體中有交流電或者交變電磁場時,導體內部的電流分布不均勻,電流集中在導體的“皮膚”部分,也就是說電流集中在導體外表的薄層,越靠近導體表面,電流密度越大,導體內部實際上電流較小。結果使導體的電阻增加,使它的損耗功率也增加。這一現象稱為趨膚效應(skin effect)。

在計算導線的電阻和電感時,假設電流是均勻分布于它的截面上。嚴格說來,這一假設僅在導體內的電流變化率(di/dt)為零時才成立。另一種說法是,導線通過直流(dc)時,能保證電流密度是均勻的。或者電流變化率很小,電流分布仍可認為是均勻的。對于工作于低頻的細導線,這一論述仍然是可確信的。

但在高頻電路中,電流變化率非常大,不均勻分布的狀態甚為嚴重。高頻電流在導線中產生的磁場在導線的中心區域感應出最大的電動勢。由于感應的電動勢在閉合電路中產生感應電流,在導線中心的感應電流最大。因為感應電流總是在減小原來電流的方向,它迫使電流只限于靠近導線外表面處。效應產生的原因主要是變化的電磁場在導體內部產生了渦旋電場,與原來的電流相抵消。

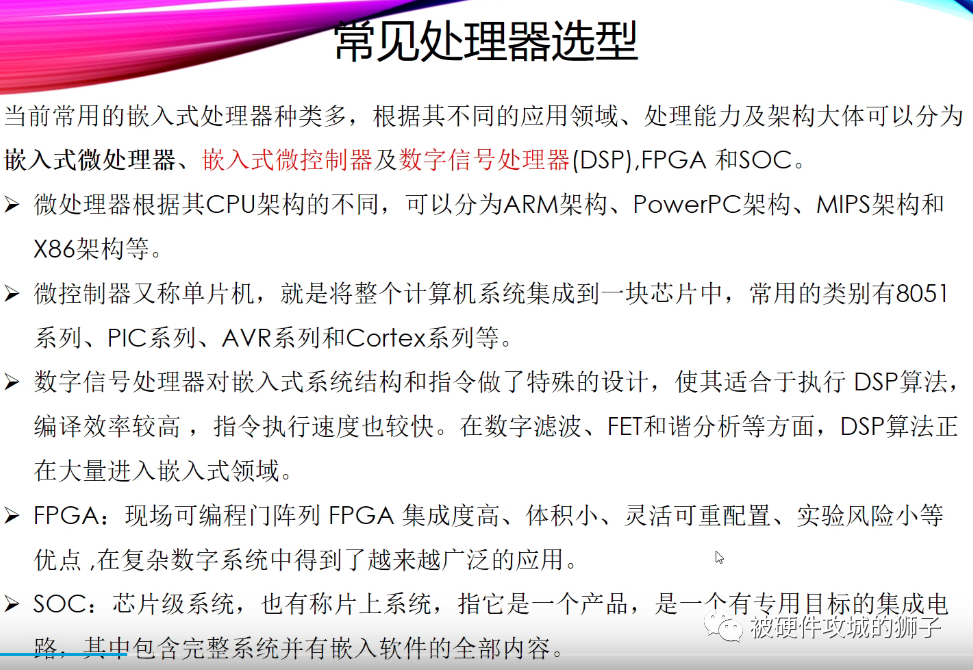

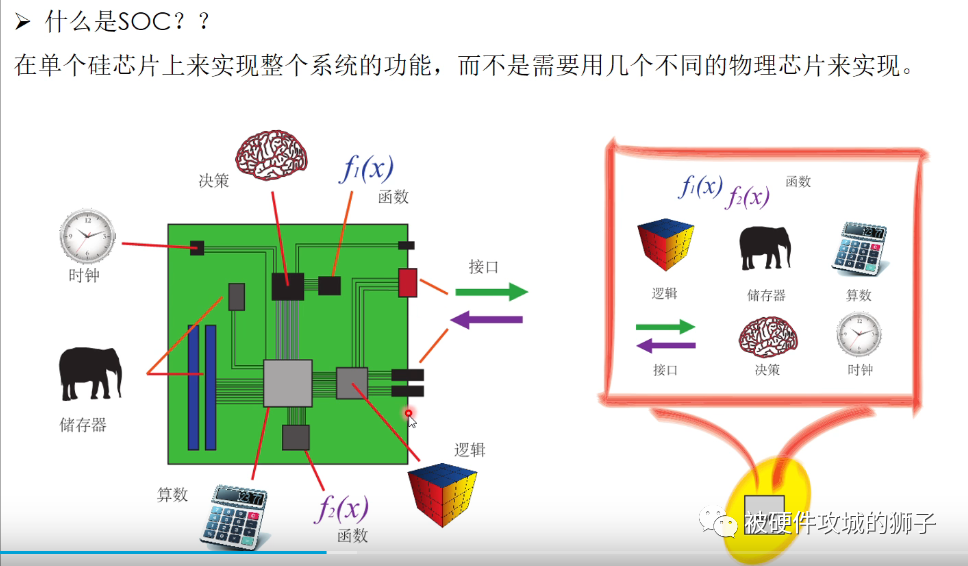

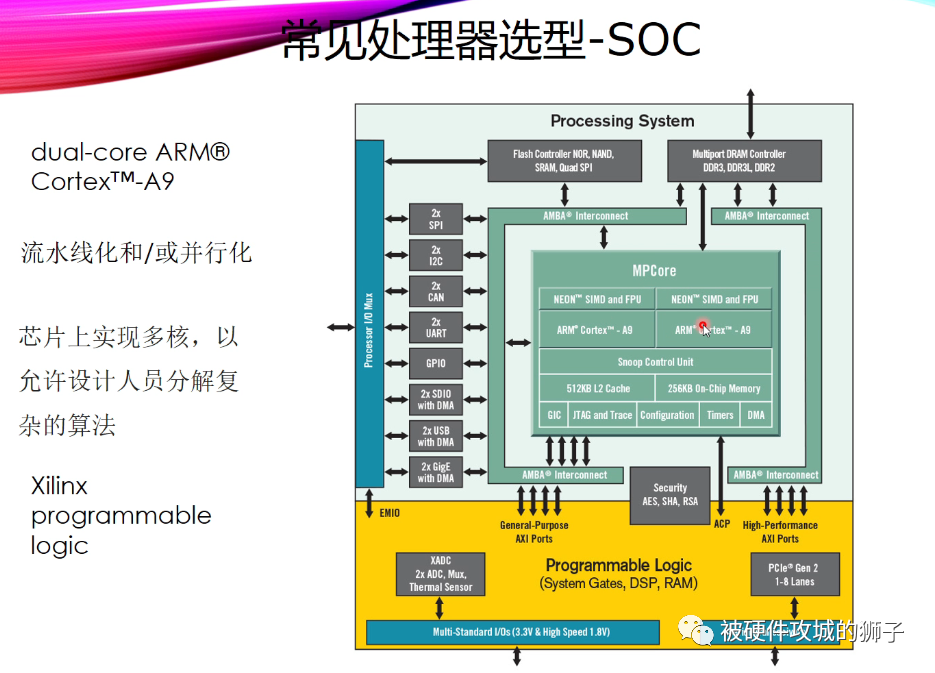

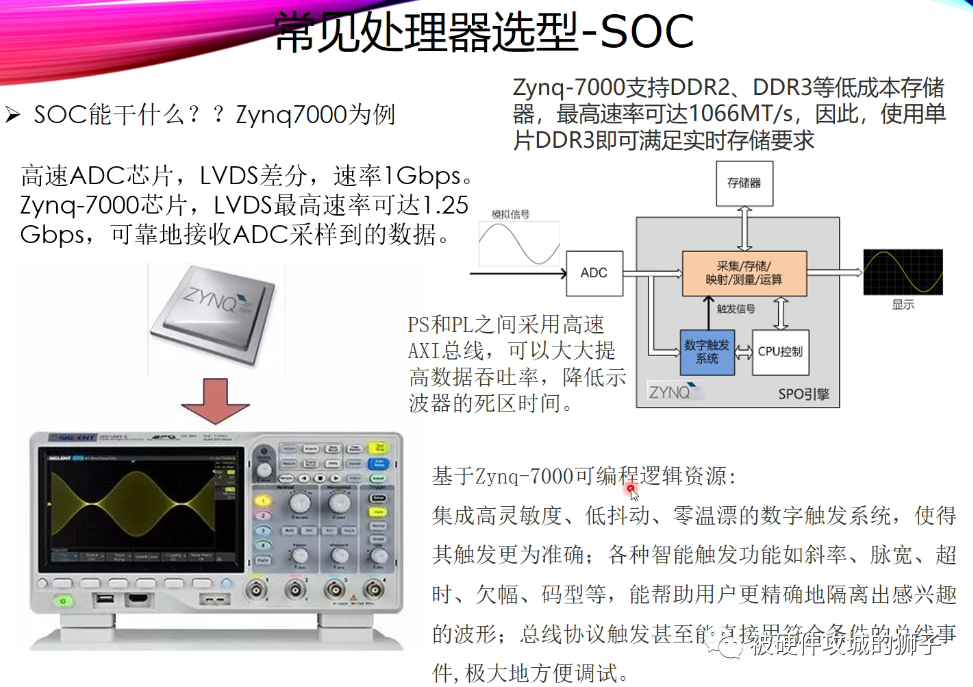

30.常見處理器選型

31.復位信號的必要性

復位信號的基本作用是將電路強制到一個確定的狀態 。在實際設計中是否需要復位,取決于芯片的應用和功能,如果一個芯片不需要一個確定的起始狀態,則沒有必要使用復位信號;相反,如果芯片的正常工作必須從一個確定狀態開始,那么復位信號就是必須的。

復位信號最基本的目的是使硬件電路能夠進入一個穩定操作的確定狀態

總的來說,認為不論對于系統來說是否需要,一個芯片的所有觸發器都應該是可以復位的。(在一些高速應用中,除去一些觸發器的復位可以提高設計的性能,例如應用在流水線的寄存器)。

在選擇復位實現的策略之前,需要思考一些問題。比如

使用同步復位還是異步復位;

是否每個觸發器都要收到復位信號;

復位樹的要求;

如何驗證復位信號的時序;

怎樣測試復位功能;

多時鐘域的設計中實現如何復位等等。

兩種復位方式-線與邏輯,一直手動MR復位,reset輸出,一種看門狗輸出,需要不斷喂狗。

兩種復位方式-線與邏輯,一直手動MR復位,reset輸出,一種上電復位,也是reset輸出;

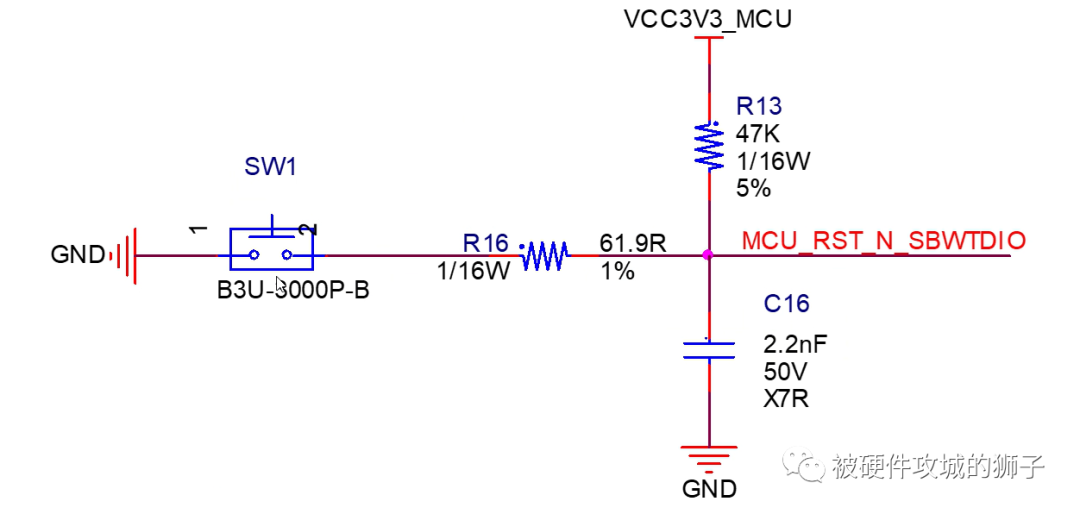

專用的復位芯片:

復位寬度 復位電平

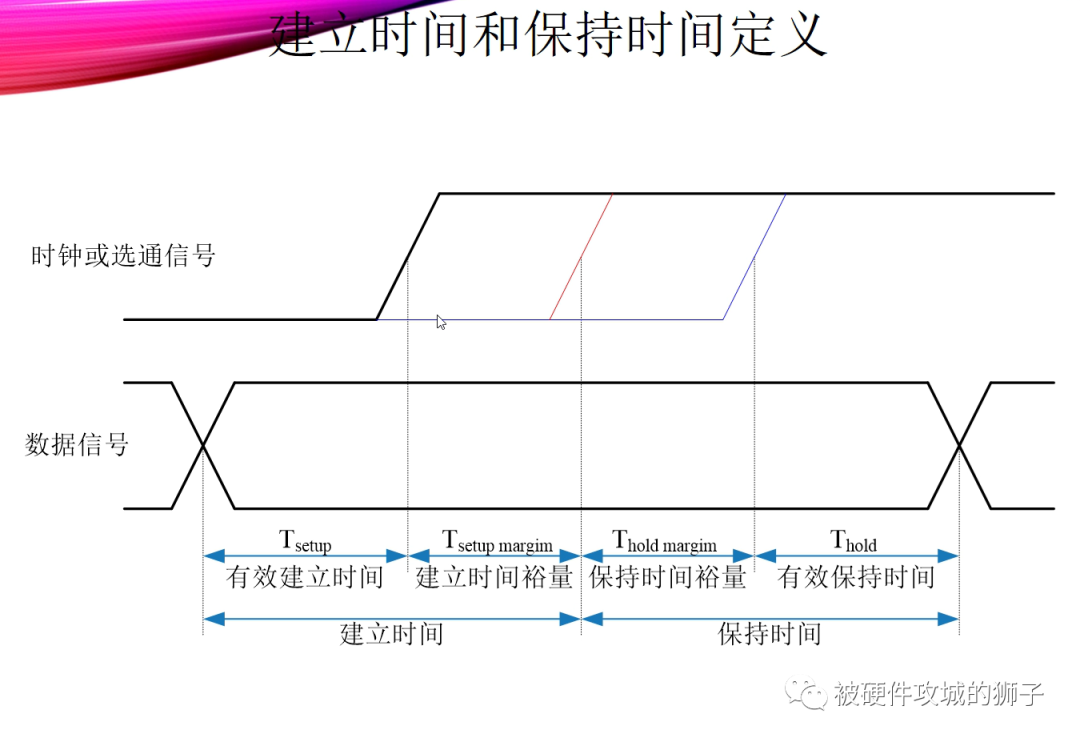

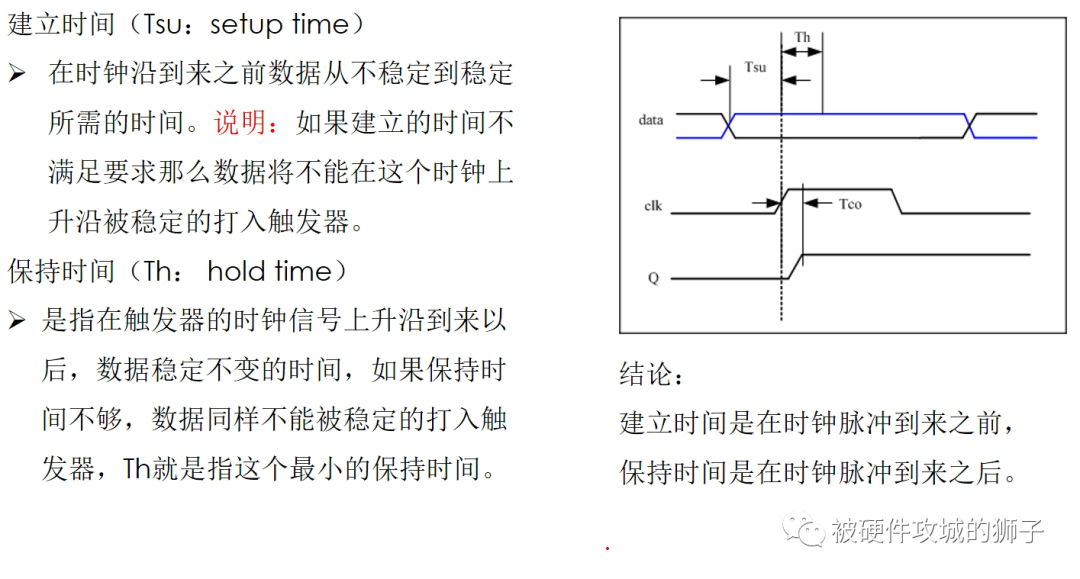

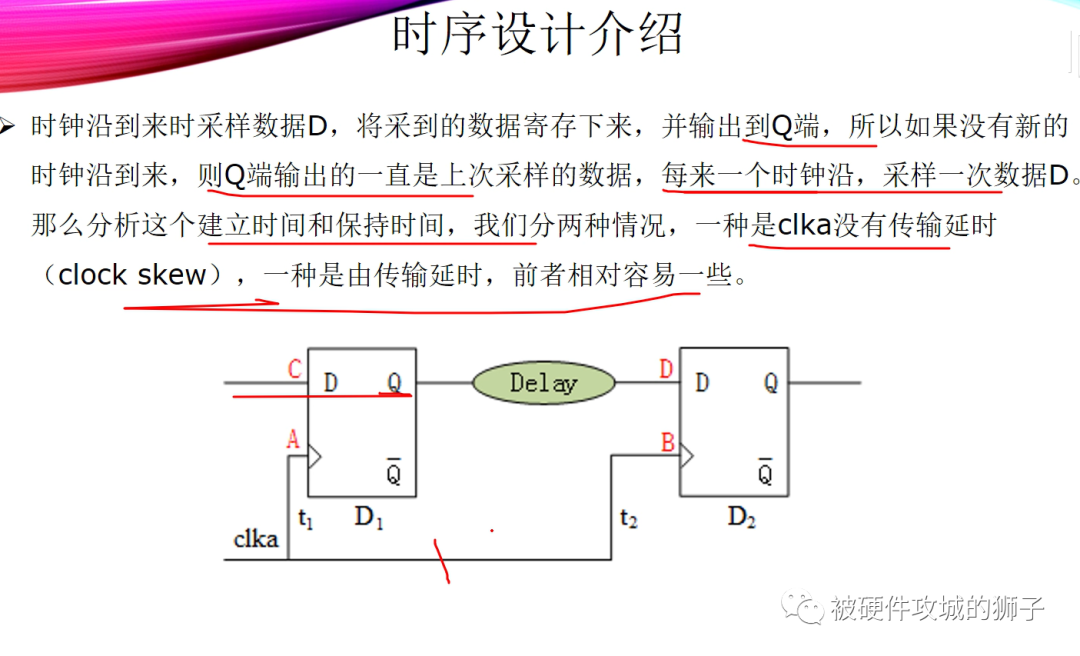

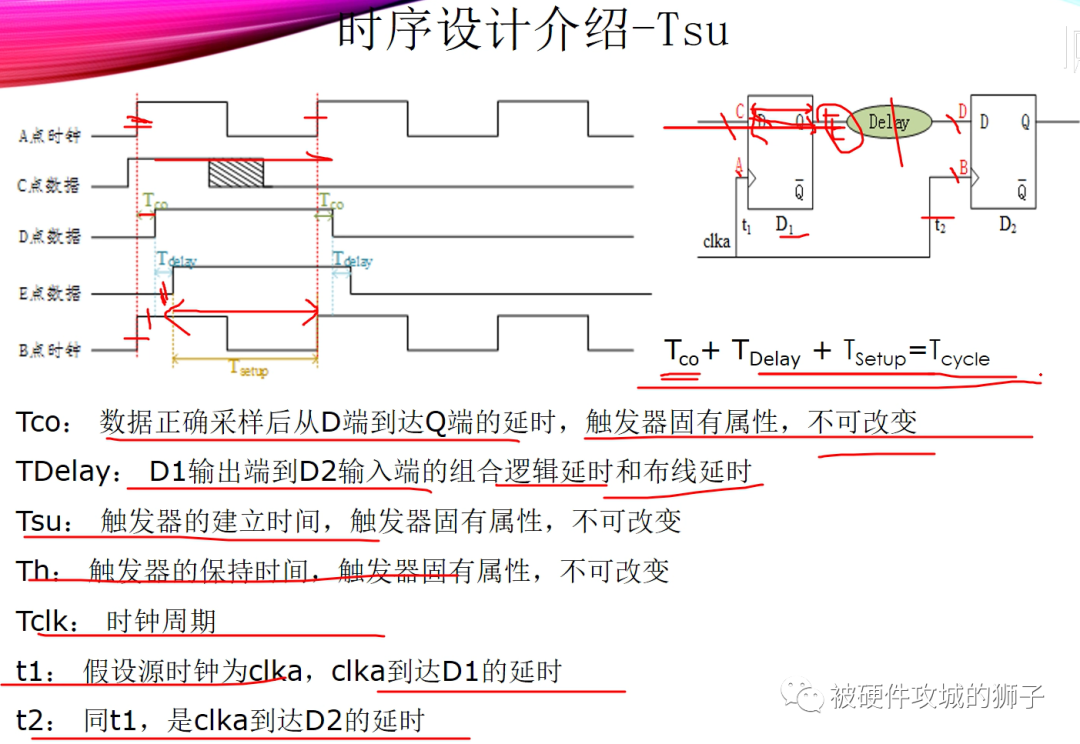

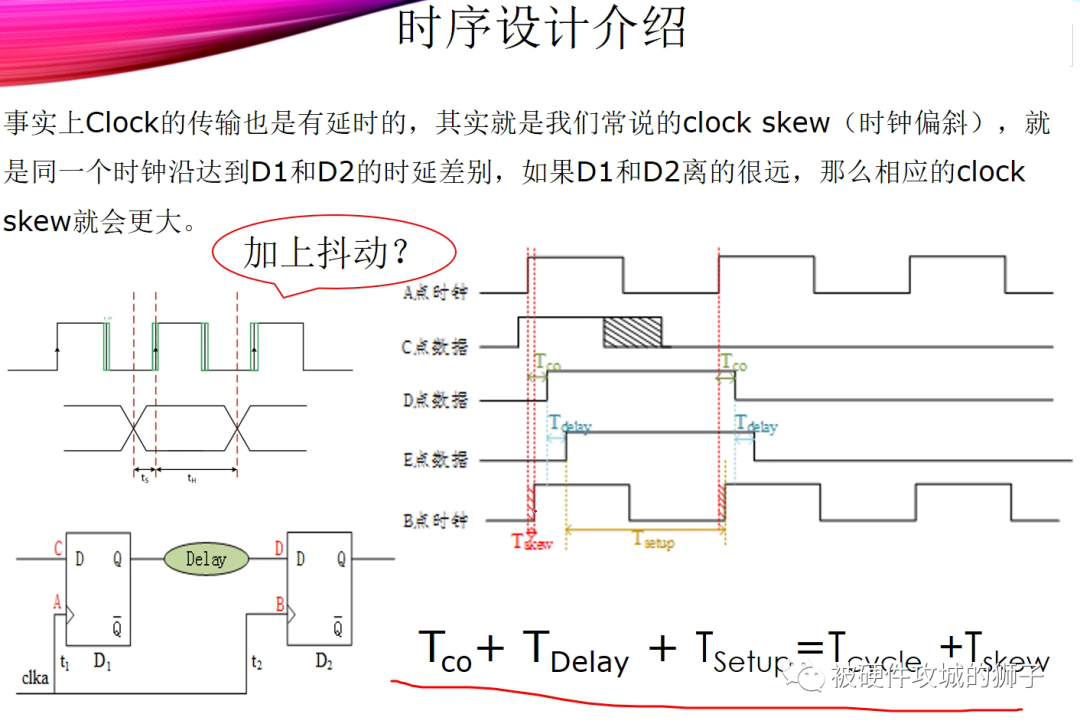

32.時序問題

33.USB接口

信號定義

電路部分:

?CPU端

?防護

?疊型連接器

PS:在TX端放置耦合電容,且最好放在連接器端

33.ARM Contex-A系列處理器

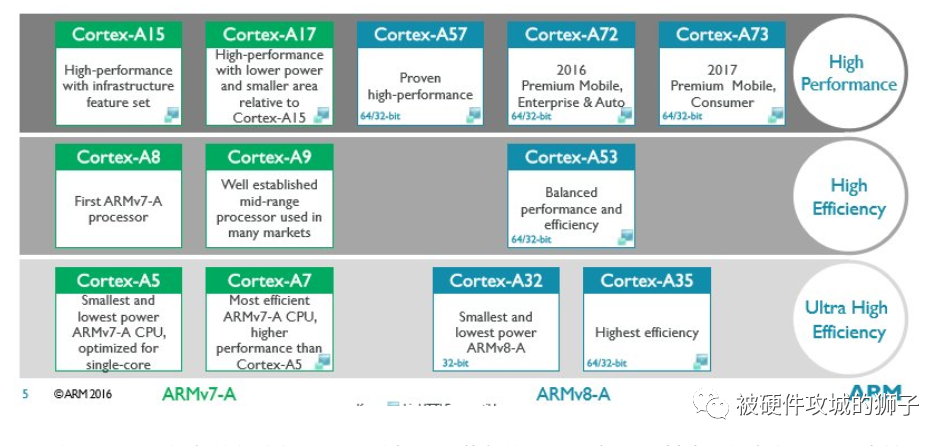

如圖所示,綠色的部分都是v7-A的架構,藍色的是v8-A架構,基本上綠色都是可以支持到32和64位的,除了A32,只支持到32位。在右邊的每個部分,比如說需要高效能的最上面的A15-A73這個部分是最高效的,接下來就是比較注重整個效率的部分了,中間那個部分是比較高效率的,最下面那欄的是效率最好的,在電池的效能方面達到了最好的標準。

如果非要給他們一個排序的話,從高到低大體上可排序為:Cortex-A73處理器、Cortex-A72處理器、Cortex-A57處理器、Cortex-A53處理器、Cortex-A35處理器、Cortex-A32處理器、Cortex-A17處理器、Cortex-A15處理器、Cortex-A7處理器、Cortex-A9處理器、Cortex-A8處理器、Cortex-A5處理器。

-

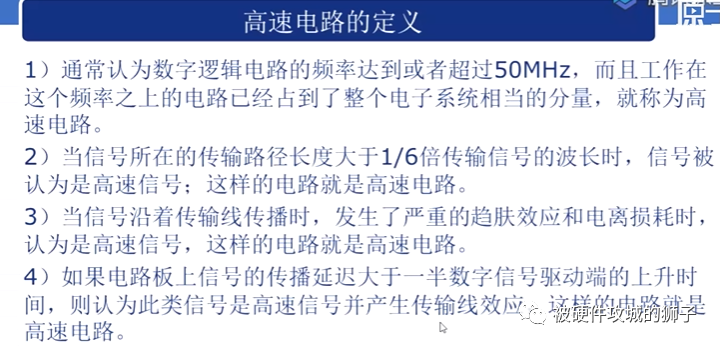

高速電路

+關注

關注

8文章

160瀏覽量

24358 -

CAN協議

+關注

關注

1文章

36瀏覽量

12765 -

網絡終端

+關注

關注

0文章

20瀏覽量

8439 -

歐姆電阻

+關注

關注

0文章

71瀏覽量

15617

原文標題:DDR3和eMMC區別

文章出處:【微信號:被硬件攻城的獅子,微信公眾號:被硬件攻城的獅子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

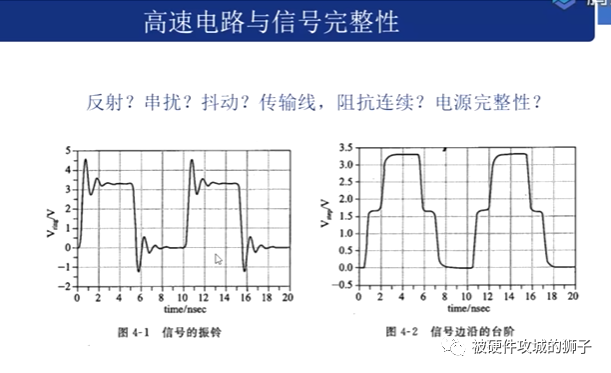

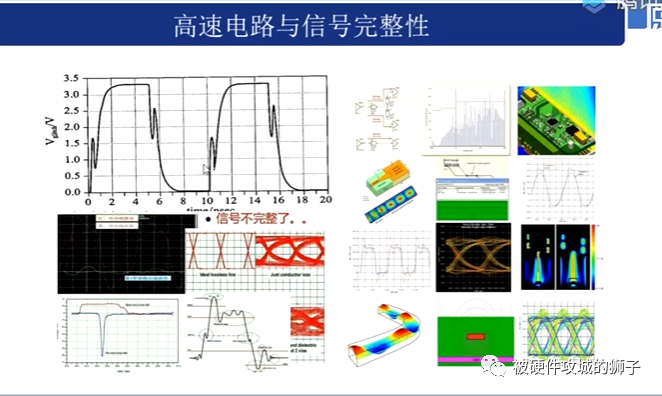

PCB設計之高速電路的定義及信號完整性問題總結

高速電路與射頻電路的區別

電路板制造標準和高速信號布線的約束定義和管理

看待高速信號的不同定義

淺述PCB設計中關鍵技術——信號完整性(SI)

高速電路是什么,什么信號才屬于高速信號?

高速電路的定義與信號完整性問題

定義和測試高速ADC中的動態參數

高速電路是什么,什么信號才屬于高速信號

高速pcb的定義是什么

高速信號的定義和仿真驗證分析

高速電路的定義

高速電路的定義

評論