FIFO的使用非常廣泛,一般用于不同時鐘域之間的數據傳輸,或者用于不同數據寬度之間的數據匹配。在實際的工程應用,可以根據需要自己寫FIFO。不考慮資源的情況下,也可以使用Xilinx提供的IP核來完成。

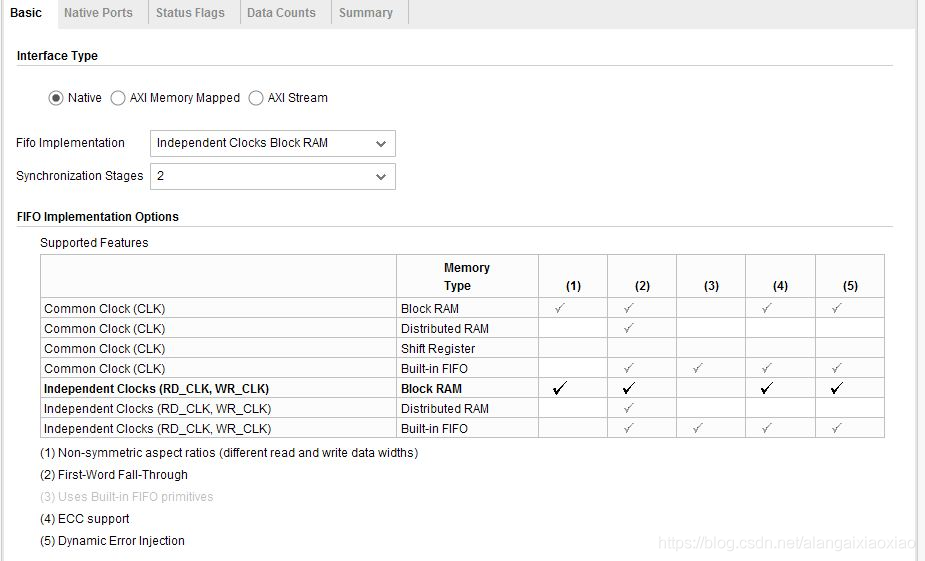

接口類型選擇Native,SOC芯片上也可以根據需要選擇AXI接口。

選擇存儲器類型:可以用塊RAM、分布式RAM,移位寄存器和內嵌FIFO來實現FIFO。這里主要是block RAM和distribute RAM之間的區別。簡而言之,block RAM是FPGA中定制的ram資源,而distribute RAM則是由LUT構成的RAM資源。由此區別表明,當FIFO較大時應選擇block RAM,當FIFO較小時,選擇distribute RAM.另外一個很重要的就是block RAM支持讀寫不同寬度,而distribute不支持。在這里為了更全面的了解FIFO,選擇block RAM以擁有非對稱方向速率的特性,內嵌FIFO(Builtin FIFO)在5以上的FPGA芯片中才存在。

時鐘:讀寫操作是否在相同的時鐘域中完成。如果是,可以選擇Common clock,否則,選擇Independent clcoks。

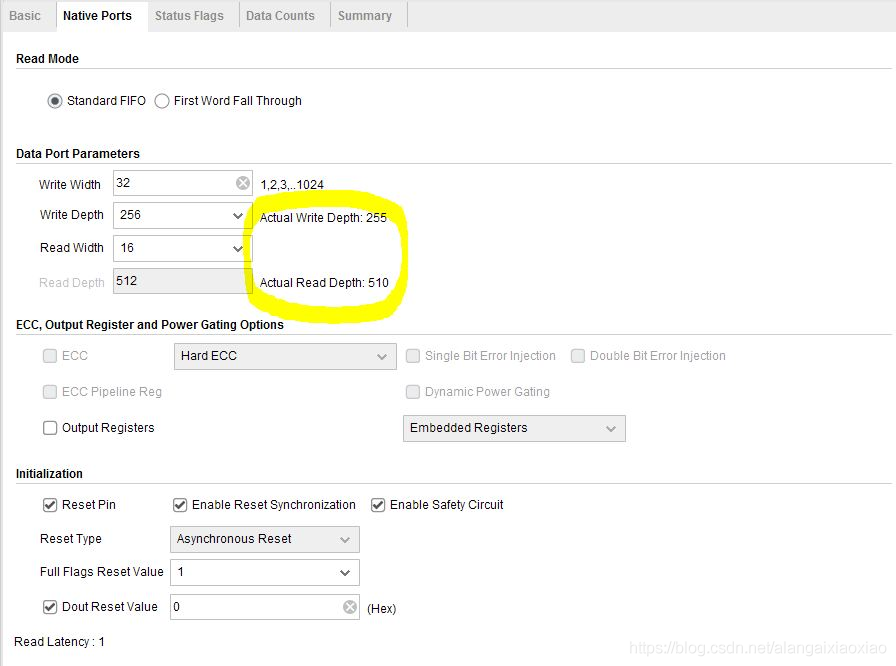

讀模式有兩種選擇,一般選擇標準模式,First-Word Fall-Fhrough模式為首字預現,FWFT是指在不影響FIFO讀操作的情況下,提前查看下一個數據的能力。即FIFO中不為空,有可用的數據時,FIFO中的第一個數據自動出現在輸出總線DOUT上。

Synchronization Stage:穿過交叉時鐘域的同步狀態(寄存器)數量,默認即可。

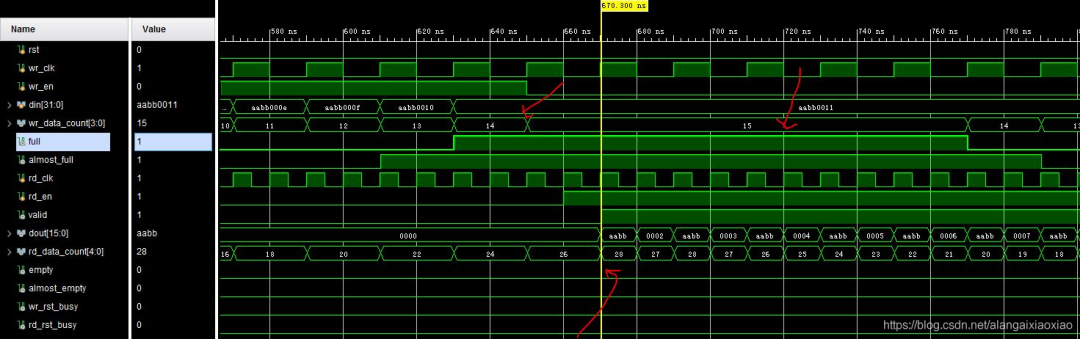

data port parameters處,有actual write depth和actual read depth,他們都比我們設置的要小,在實際的工程應用中,FIFO深度確實要比預設的小1,即當寫入了Write Width-1個數據之后,FIFO的滿信號full會拉高,這個時候如果還要寫入數據,則寫入的數據丟失。同理,讀出Read Width-1個數據后,FIFO的空信號empty會拉高,此時讀出信號無效。如下:

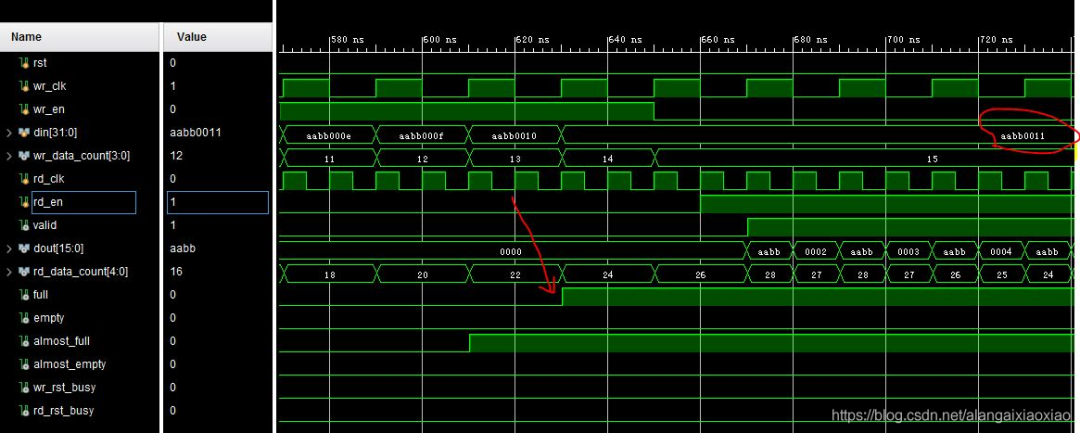

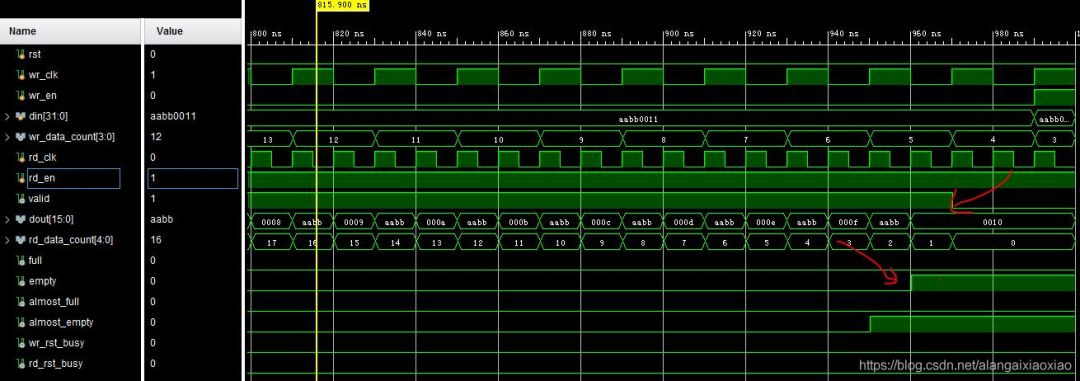

該FIFO數據深度為16,從aabb0002到aabb0011共寫入16個數據,當寫入到第15個時,FULL信號拉高,數據不能被有效的寫入,從讀狀態可以看出。當讀寫數據位寬不匹配時,寫入的位寬大于讀出的數據位寬,則先從高位開始讀;當寫入的數據位寬小于讀出時,先寫入的數據在讀數據的高位,如下:

關于FIFO復位,Xilinx FIFO默認為高電平復位,在Initialization 中可以設置復位信號到來之后,full、almost full、prog full等信號的復位值為0,或者為1。可以設置讀寫同步復位,或者異步復位。fifo的復位需要一段時間,期間wr_rst_busy和rd_rst_busy信號為高電平,此時應禁止讀寫FIFO,否則會造成數據丟失。

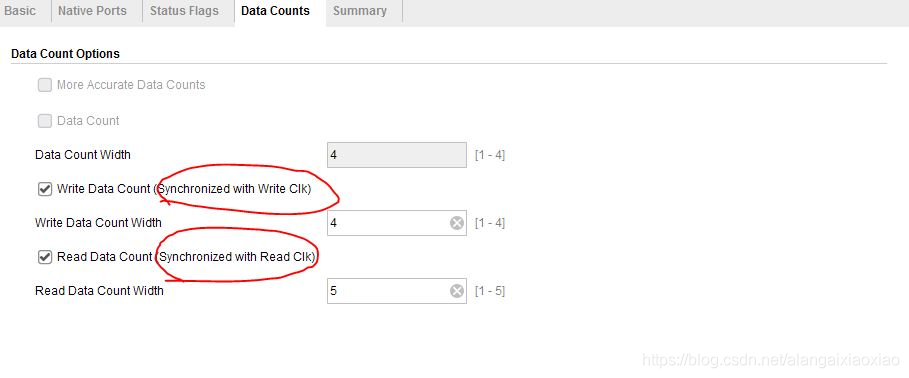

關于讀寫計數,讀計數是和讀時鐘同步的,寫計數是和寫時鐘同步的。讀計數是以讀數據寬度為單位,fifo中存在的數據個數;寫計數是以寫數據寬度為單位,fifo中存在的數據個數,這兩個值的結果,簡單理解就是fifo內部控制器讀寫地址的差,由于fifo讀寫時鐘可能異步,讀寫時鐘頻率不同,導致計算讀寫計數值時存在延遲,并不完全和讀寫操作同步。

讀寫計數仿真結果如下:

關于讀寫使能,寫使能wr_en為高時,數據立即被寫入到fifo中,讀使能為高時,下一個時鐘周期,有效數據才會出現在數據總線dout上。

一段簡單的仿真如下:

`timescale 1ns / 1ps

module tb_fifo_16x256(

);

reg rst;

reg wr_clk;

reg rd_clk;

reg [31:0] din;

reg wr_en;

reg rd_en;

wire [15:0] dout;

wire full;

wire empty;

wire valid;

wire almost_full;

wire almost_empty;

wire [4:0] rd_data_count;

wire [3:0] wr_data_count;

wire wr_rst_busy;

wire rd_rst_busy;

always #10 wr_clk <= ~wr_clk;

always #5 rd_clk <= ~rd_clk;

initial begin

rst <= 1;

wr_clk <= 0;

rd_clk <= 1;

din <= 32'haabb0001 ;

wr_en <= 0;

rd_en <= 0;

#20;

rst <= 0;

#300;

//======================================================empty

repeat(16) @(posedge wr_clk)

begin

din <= din + 1;

wr_en <= 1;

end

repeat(1) @(posedge wr_clk) wr_en <= 0;? ?

repeat(32) @(posedge rd_clk)

begin

rd_en <= 1;? ? ??

end

repeat(1) @(posedge rd_clk) rd_en <= 0;

//=======================================================full

repeat(16) @(posedge wr_clk)

begin

din <= din + 1;

wr_en <= 1;

end

repeat(1) @(posedge wr_clk) wr_en <= 0;? ??

end

initial begin

#900;

repeat(32) @(posedge rd_clk)

begin

rd_en <= 1;? ? ??

end

repeat(1) @(posedge rd_clk) rd_en <= 0;

end

fifo_16x256 fifo_16x256_inst (

.rst(rst), // input wire rst

.wr_clk(wr_clk), // input wire wr_clk

.rd_clk(rd_clk), // input wire rd_clk

.din(din), // input wire [31 : 0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [15 : 0] dout

.full(full), // output wire full

.almost_full(almost_full), // output wire almost_full

.empty(empty), // output wire empty

.almost_empty(almost_empty), // output wire almost_empty

.valid(valid), // output wire valid

.rd_data_count(rd_data_count), // output wire [8 : 0] rd_data_count

.wr_data_count(wr_data_count), // output wire [7 : 0] wr_data_count

.wr_rst_busy(wr_rst_busy), // output wire wr_rst_busy

.rd_rst_busy(rd_rst_busy) // output wire rd_rst_busy

);

endmodule

-

數據傳輸

+關注

關注

9文章

1919瀏覽量

64676 -

fifo

+關注

關注

3文章

389瀏覽量

43737 -

SoC芯片

+關注

關注

1文章

613瀏覽量

34947

原文標題:FPGA學習-FIFO使用小結

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【連載視頻教程(十六)】小梅哥FPGA設計思想與驗證方法視頻教程之FIFO介紹與時序驗證

spi通訊的發送中斷有什么意義

spi發送中斷有什么意義?

vivado的fifo生成步驟介紹

基于c語言的FIFO介紹

異步FIFO結構

Camera Link接口的異步FIFO設計與實現

微雪電子FT245USB轉FIFO介紹

同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO各在什么情況下應用

同步FIFO和異步FIFO區別介紹

FIFO的使用介紹

FIFO的使用介紹

評論