在日常PCB版圖設(shè)計中,阻抗突變是不可避免的事情。下圖為日常的版圖走線:

圖中標(biāo)記處為常見的阻抗突變。

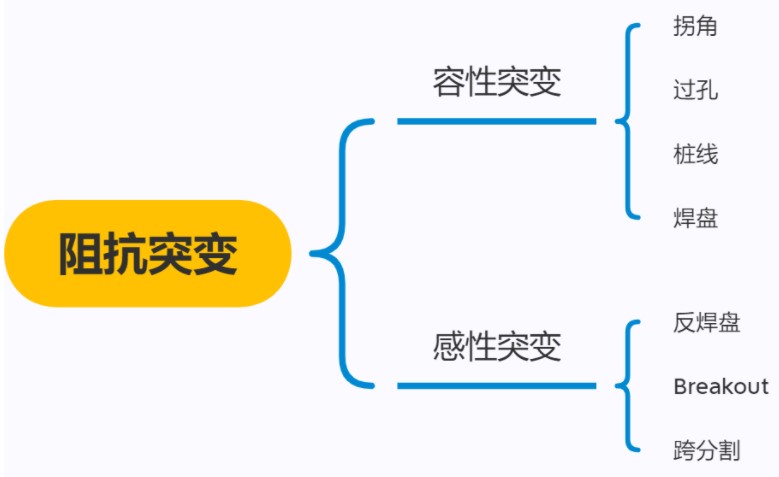

簡短意賅,直接給出阻抗突變總結(jié)圖:

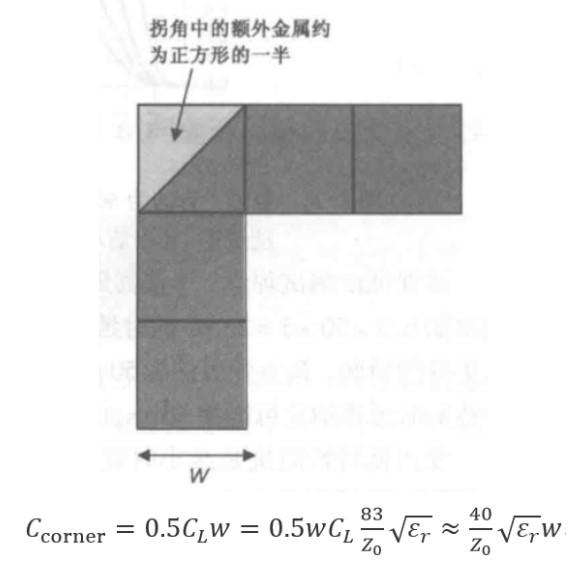

1、拐角

之前有推導(dǎo)過,導(dǎo)線中的電子速度為1cm/s, 所以90°拐角不會影響電子速度。90°拐角彎曲處更多影響是線寬,造成容性突變,影響信號質(zhì)量。

2、過孔

記得之前總結(jié)過孔經(jīng)驗法則的時候,有過這么兩條:

1.50?傳輸線單位長度電容約為3.3 pF/in;

2.過孔樁線的單位長度電容約為5 pF/in。

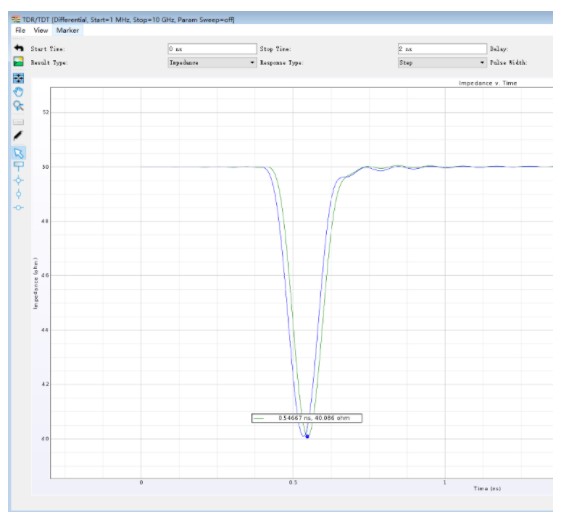

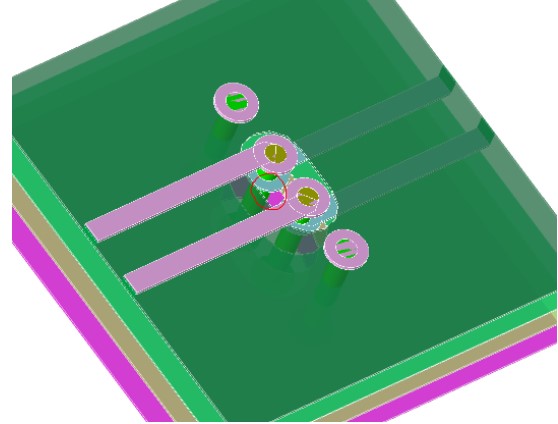

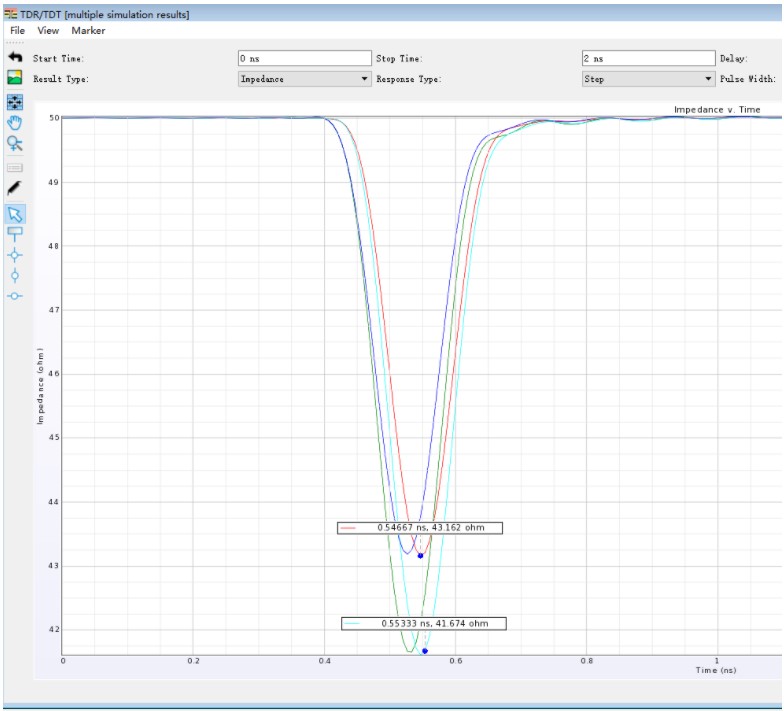

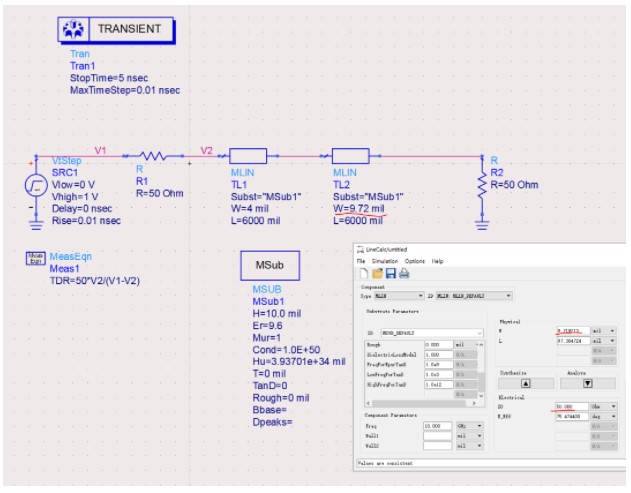

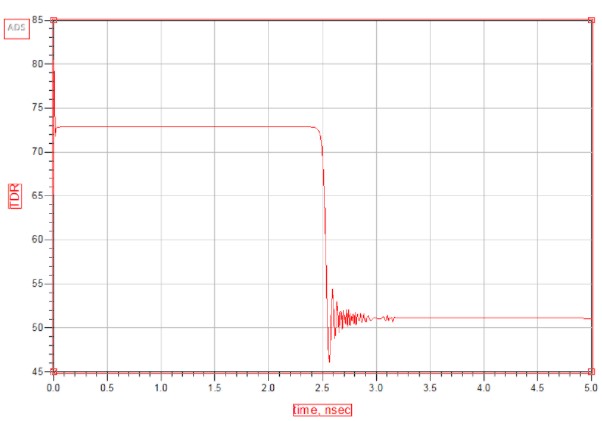

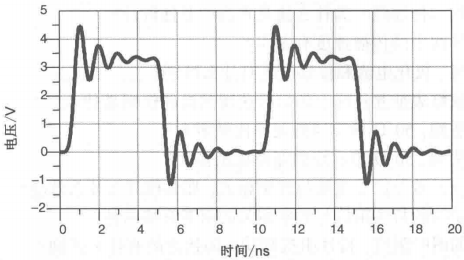

為了大家有個直觀的印象,對過孔的阻抗突變做了個仿真,見下圖:

在實際的工作中,所以才有對高速信號的過孔,進行優(yōu)化處理,比如stiching Via,Antipad等來減少阻抗突變

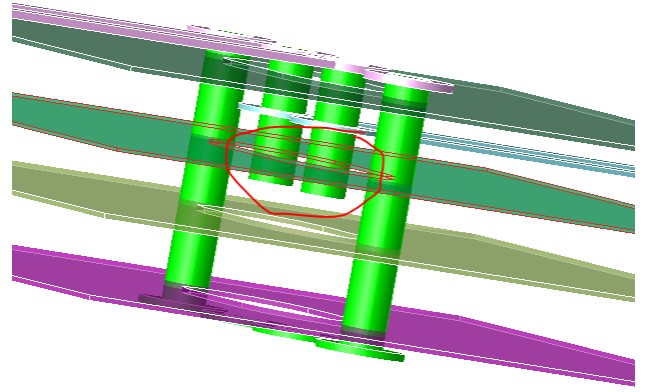

3、樁線

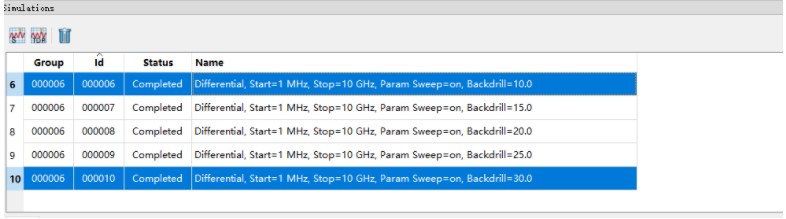

隨著產(chǎn)品的高速化,很多Stub都做了Backdrill的處理,來控制反射,優(yōu)化阻抗突變。這里面對高速率產(chǎn)品有需要考慮PCB工藝的誤差。

樁線越長,阻抗的容性突變越大

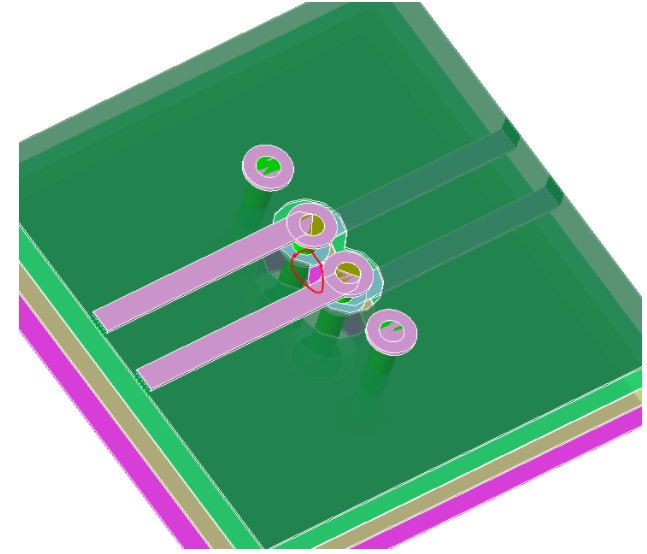

4、Breakout

芯片出Pin的Breakout(Pin field)區(qū)域,一般走線比較窄,出了這個區(qū)域走線恢復(fù)正常。

Breakout 區(qū)域線變窄,阻抗變大。

5、其他

信號在走線部分跨分割,除了增加感性突變,還會引起串?dāng)_和輻射。這里就不做展開。

信號經(jīng)過連接器從一塊電路板傳輸?shù)搅硪粔K電路板,連接器呈現(xiàn)出典型的感性負載特征。

6、影響

以上的這些突變會對信號產(chǎn)生什么影響呢?

容性突變使接收端產(chǎn)生下沖噪聲&接收端信號延遲。

感性突變使接收端產(chǎn)生上沖噪聲&接收端信號延遲。

7、總結(jié)

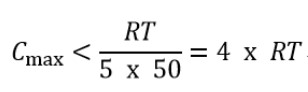

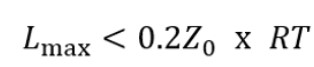

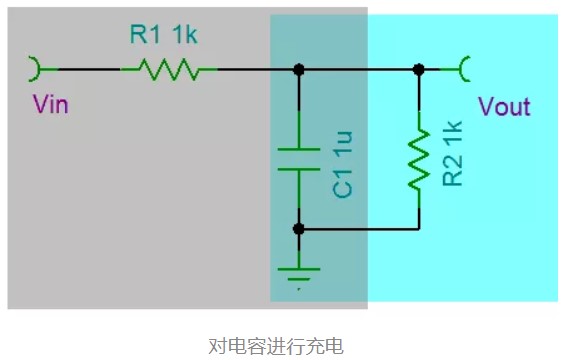

既然知道了阻抗突變的危害,我們就需要在實際的工作中,進行管控。之前的總結(jié)里給出過相關(guān)經(jīng)驗公式。

容性突變的裕量:

感性突變的裕量:

如果導(dǎo)線的特性阻抗為50?,信號上升邊為1 ns,則可容許的最大串聯(lián)電感約為0.2 x 50 x 1 ns=10 nH。

總之,管控也好,優(yōu)化也罷,信號完整性工程師所要做的就是保證鏈路在裕量范圍之內(nèi)。

審核編輯:劉清

-

連接器

+關(guān)注

關(guān)注

98文章

14631瀏覽量

136956 -

串聯(lián)電感

+關(guān)注

關(guān)注

0文章

29瀏覽量

8075 -

高速信號

+關(guān)注

關(guān)注

1文章

231瀏覽量

17728 -

PCB

+關(guān)注

關(guān)注

1文章

1823瀏覽量

13204

發(fā)布評論請先 登錄

相關(guān)推薦

信號完整性傳輸線引起阻抗突變會怎樣?

TL062流壓轉(zhuǎn)換,輸入電流≥15.5mA以后輸出電壓突變為10.42V,為什么電壓會突變呢?

如何判斷信號突變點,截取波形數(shù)組

D觸發(fā)器,CLK突變時,輸入D也突變,觸發(fā)器的輸出應(yīng)該如何判定?

鏈路上小段線的阻抗突變到底會不會影響信號質(zhì)量?

基于小波變換的信號突變檢測

電路中電容電壓和電感電流的突變

電容電壓、電感電流為什么不能突變呢?

是什么引起了反射?為什么信號遇到阻抗突變時會發(fā)生反射?

電力電容器如何應(yīng)對電壓突變?

常見的阻抗突變有哪些?這些突變會對信號產(chǎn)生什么影響呢?

常見的阻抗突變有哪些?這些突變會對信號產(chǎn)生什么影響呢?

評論