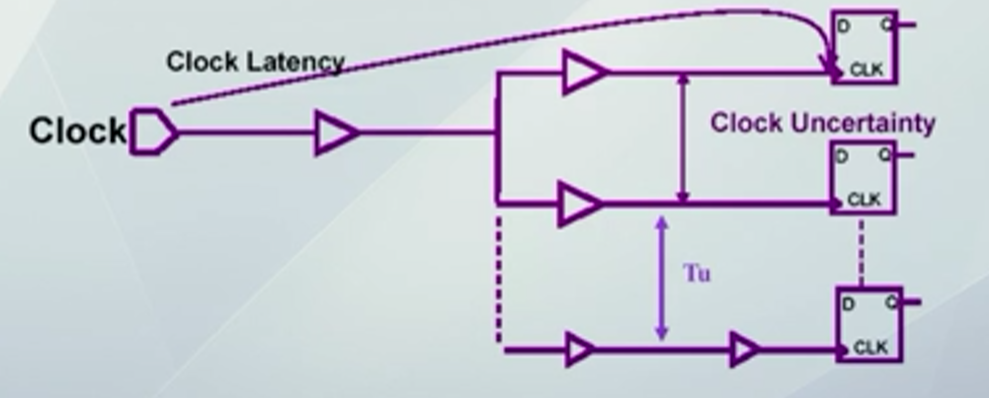

邏輯綜合過程(5)設置約束中,時序約束除需估計電路中的連線參數外,還需要關注時鐘網絡。在復雜網絡中,輸入的時鐘信號可能會連接數百個D觸發器,需要通過樹狀網絡連接,樹狀網絡的每個分叉連接有限個D觸發器。為使時鐘信號到達每個D觸發器的時間近似相等,樹狀網絡需要盡可能均勻。

描述時鐘網絡信號的參數有兩個:Clock Latency和Clock Uncertainty。Clock Latency表示時鐘信號經由其他元器件和連線到達D觸發器的延時,Clock Uncertainty表示各個D觸發器間時鐘延時的微小差異。

綜上,過程(5)設置約束中,時序約束通過靜態時序分析的準則、估算連線參數、確定時鐘網絡參數完成約束。

圖片來源:學堂在線《IC設計與方法》

當時序約束滿足后,綜合邏輯所需的軟件將嘗試滿足面積約束要求,一般面積約束的要求是將芯片的面積最小化。

以下是描述芯片的面積的三種方式:

(1)通過與非門對芯片進行描述,得出芯片等效多少門。

(2)通過等效晶體管數量的方式進行描述。

(3)通過物理面積的方式進行描述,常用的面積單位是平方微米。

非專業人員傾向使用方式(1)和方式(2)描述芯片面積。EDA軟件(根據代碼自動生成芯片電路的軟件)中對芯片面積的描述不清晰,需要設計人員判斷數值的單位是門、晶體管、物理面積三種中的哪一種。如果數值包含0.5,可能是以門為單位,因為一個非門大約等效0.5個與非門;如果數值為整數,可能是以晶體管為單位;如果數值有多個小數位,可能是以物理面積為單位。

設置約束結束后,可以進行邏輯綜合操作。邏輯綜合操作中軟件可以對電路做以下優化:

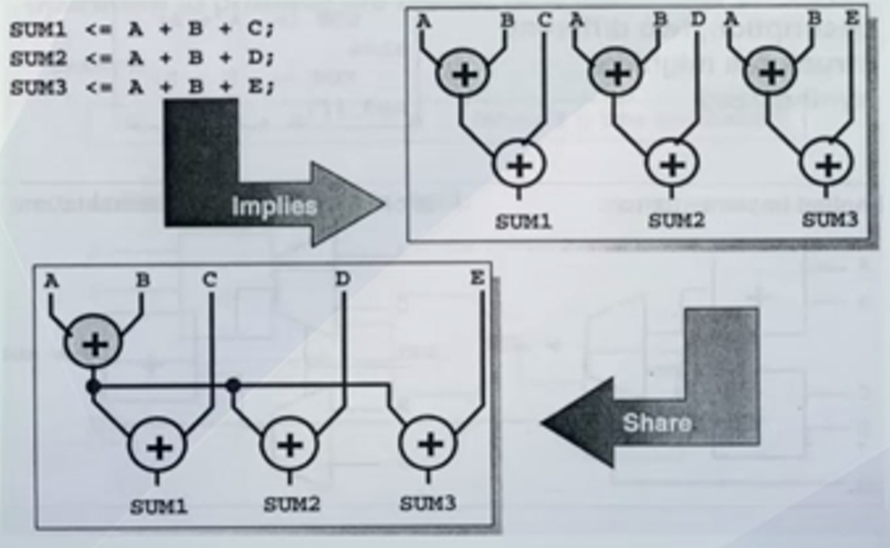

(1)共享表達式:如下圖所示,三個表達式中均有A+B,軟件會將重復的A+B電路化簡。

圖片來源:學堂在線《IC設計與方法》

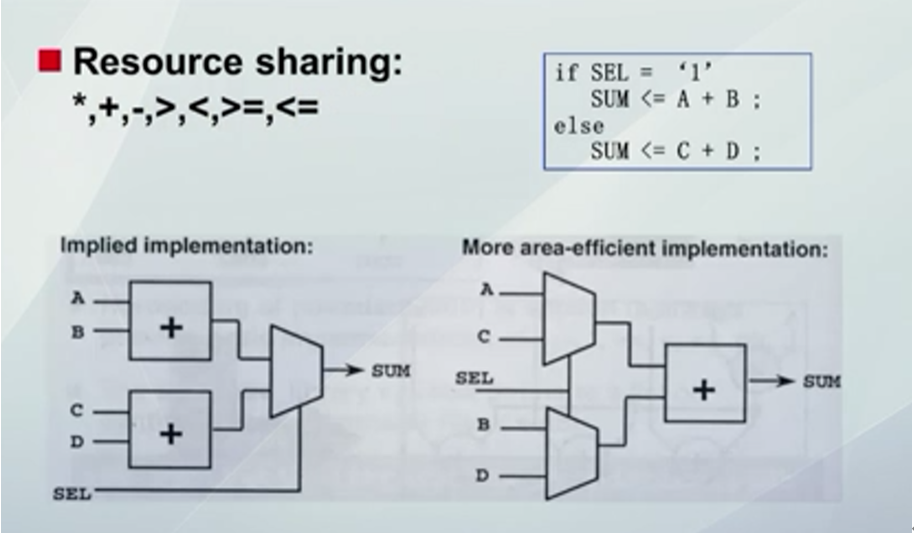

(2)資源共享:加法器(下圖電路中帶加號的正方形)所需的資源多于多路選擇器(下圖電路中的梯形)所需的資源,通過改變電路結構,將資源選擇器共享轉化為加法器共享,節省資源。

圖片來源:學堂在線《IC設計與方法》

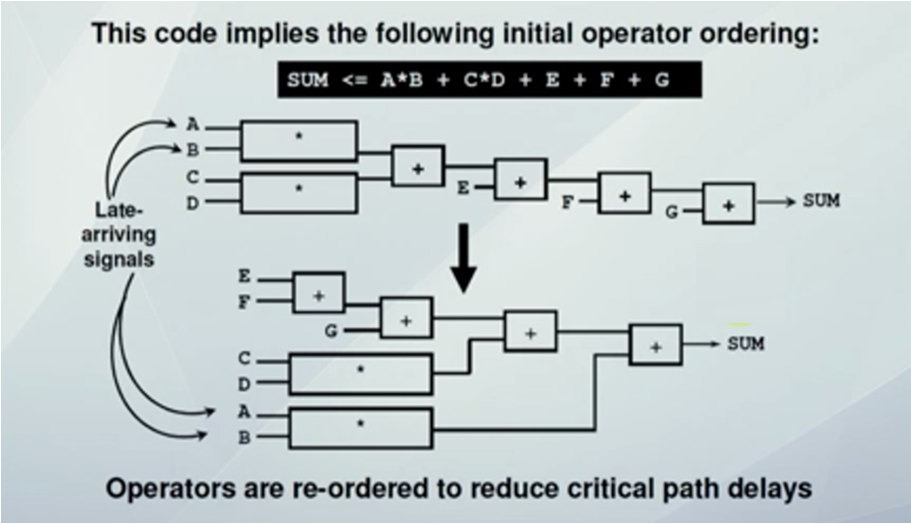

(3)操作重新排序:下圖是操作重新排序的案例,如果A、B、C、D、E、F信號不能同時到達,如A、B信號到達較晚,操作重新排序后的電路(圖中箭頭指向的電路)運算速度更快。

圖片來源:學堂在線《IC設計與方法》

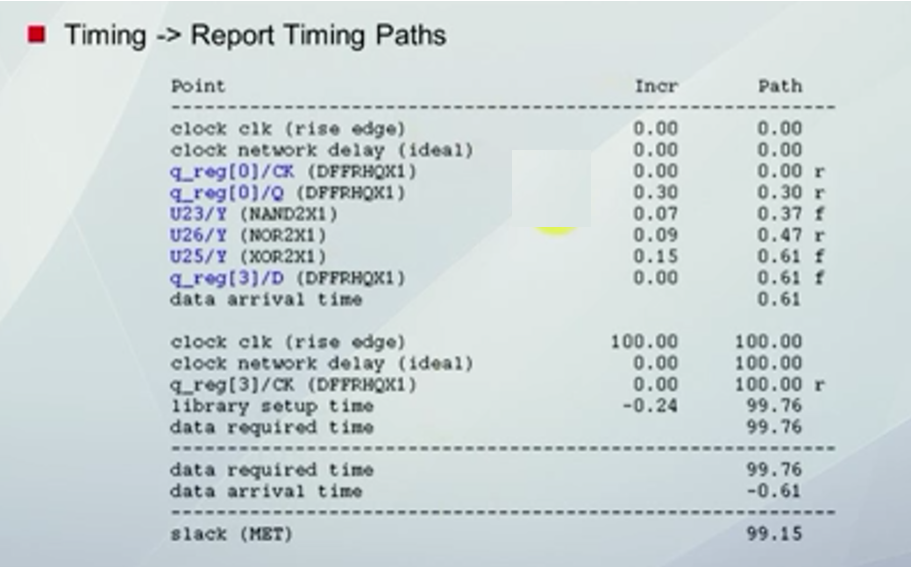

邏輯綜合操作后,進行結果分析。首先需要關注時序報告。

時序報告的第一部分是數據到達時間(data arrival time),表示上一級觸發器時鐘信號出現開始,經過所有元器件所需要的時間(個人理解)。

時序報告的第二部分是數據需求時間(data required time),表示數據傳輸可以使用的時間。

如果數據需求時間-數據到達時間>0,則滿足時序約束,可以進行面積報告分析,否則需修改約束或設計代碼。根據時序分析結果,可以重建關鍵路徑,進一步優化電路。

圖片來源:學堂在線《IC設計與方法》

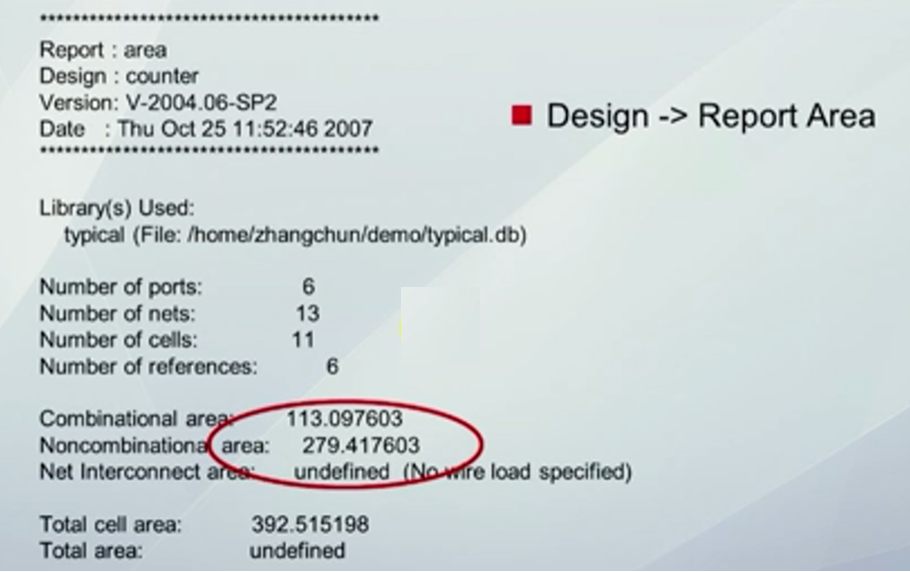

其次關注面積報告,下圖報告中紅圈內表示芯片的面積參數,因為報告中數值有多個小數位,所以數值的單位是平方微米。

在商業設計中,需要定義芯片內連線的模型以更準確地估算出芯片面積(含個人理解),Net Interconnect area會有具體數值,不會如下圖中表示的undefined。

結果分析滿足設計條件后,保存結果,邏輯綜合過程結束。

審核編輯 :李倩

-

芯片設計

+關注

關注

15文章

1021瀏覽量

54912 -

觸發器

+關注

關注

14文章

2000瀏覽量

61185 -

時鐘網絡

+關注

關注

0文章

16瀏覽量

6575

原文標題:芯片設計相關介紹(25)——邏輯綜合過程(下)

文章出處:【微信號:行業學習與研究,微信公眾號:行業學習與研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時鐘芯片綜合測試策略:從生成過程到關鍵模塊

邏輯電路芯片-組合邏輯電路芯片-時序邏輯電路芯片

常用邏輯門芯片有哪些

存儲芯片和邏輯芯片的差異

邏輯芯片:現代電子技術的基石

揭秘邏輯芯片與存儲芯片背后的工藝差異!

邏輯控制芯片為什么要流過足夠的電流才會翻轉?

芯片中EDC的含義

交換芯片的構建過程

LED顯示屏模組邏輯驅動芯片:SM245的功能和應用

芯片設計之邏輯綜合過程(下)

芯片設計之邏輯綜合過程(下)

評論