電子發燒友網報道(文/周凱揚)對于近幾年推出的HPC系統來說,高能效已經成了大家無法規避的話題,就連TOP500上的超算,比如排名第一的超級計算機,美國能源部下屬國家實驗室的Frontier系統,也憑借單機柜原型機在GREEN500能效榜上拿下第一,整個系統拿下了第二的成績。與十多年前的那些HPC系統相比,現在的設計不僅是在性能上不可同日而語,連能效比也提升了百倍以上。

能做到如此高的能效,除了CPU、GPU本身的設計外,也要歸功于先進的冷卻系統和電源管理。對于已經走向多核異構時代的HPC系統而言,系統級別的電源與熱管理尤為重要,而且還得做到精心調校、針對負載進行智能調整的動態電源管理。

已有的電源控制器方案

針對不同的CPU系統,市面上已經有了不少商用電源控制器,比如英特爾的CPU有用于C-States管理的電源控制單元(PCU),ARM有幫助應用處理器卸載電源與系統管理任務的系統控制處理器(SCP)和可管理控制處理器(MCP),AMD有采集傳感數據進行快速調整的系統管理單元(SMU),IBM的Power處理器有片上控制器(OCC)等。

然而,不少已有的方案都是基于單核心的MCU打造的,在面對單片核心數越來越多以及逐漸普及的Chiplet設計時,這些方案就因為缺乏擴展性而顯得力不從心了。除此之外,主辦的尺寸、布局和成本的因素,進一步限制了HPC處理器本身的片上電源管理。正因如此,在擁有龐大核心數量的HPC系統上,我們需要一個可擴展的控制器方案。

在這些要求下,瑞士蘇黎世聯邦理工學院(ETH)的集成系統實驗室就基于開源的RISC-V架構,打造了這樣一個擁有并行控制規則計算加速的電源控制器IP——ControlPULP。

可擴展的電源控制器

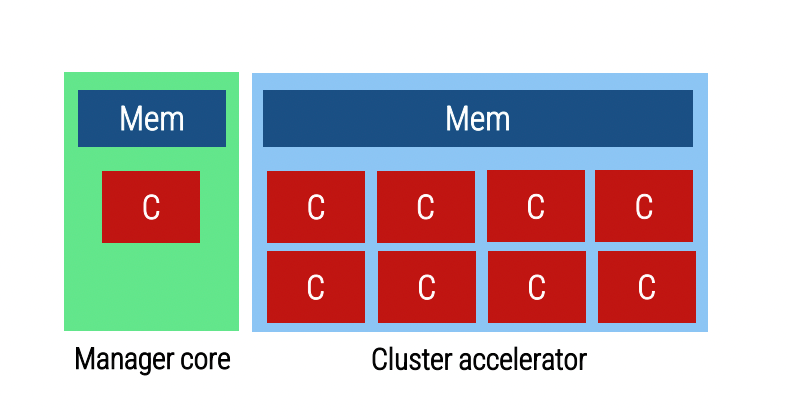

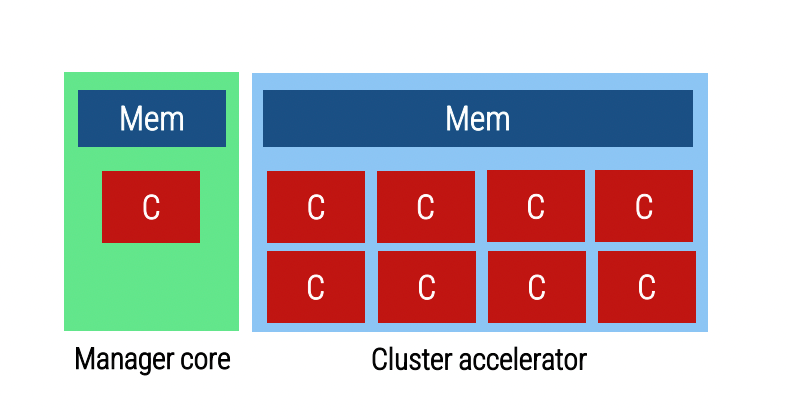

ControlPULP采用了九核的設計,一個單核管理器核心,和8核的加速器簇來加速電源控制固件的工作負載,而這九個核心全部基于CV32E40P,這是一個32位4級流水線的RISC-V開源核心,由瑞士蘇黎世聯邦理工學院和意大利博羅尼亞大學合作的PULP平臺維護,他們也將CV32E40P捐獻給了開放硬件聯盟OpenHW。

ControlPULP架構 / 瑞士蘇黎世聯邦理工學院

此外,ControlPULP集成了一個直接內存訪問引擎,用于獲取片上傳感器的數據,還有一個uDMA引擎,用于支持基于標準電源管理接口(比如電壓調節總線AVSBUS/PMBUS)的片外外圍設備以及通過I2C或MTCP協議的BMC通信。至于底層控制策略的調度,則靠PULP平臺自己開發的開源FreeRTOS來實現。

在其電源控制策略中,ControlPULP主要負責兩大主要控制任務,一個是定期控制任務,一個是電源控制任務。定期控制任務結合溫度傳感器、功耗傳感器內的數據,以及目標頻率、預期負載和總功耗預算等數據,來進行電源調度和熱管理。電源控制任務則是通過PMBUS/AVSBUS獲得的電壓軌功耗和BMC通信來完成快速電源控制。

根據他們測試的結果,這種多核加速器簇的結構相較過去的單核方案來說,在控制策略的執行速度上快了5倍,而且集成在HPC處理器中并不會占用多大的面積。他們在格芯的GF22FDX工藝下得到的綜合結果中,ControlPULP所占處理器面積甚至不到百分之一。

開源電源控制器的未來

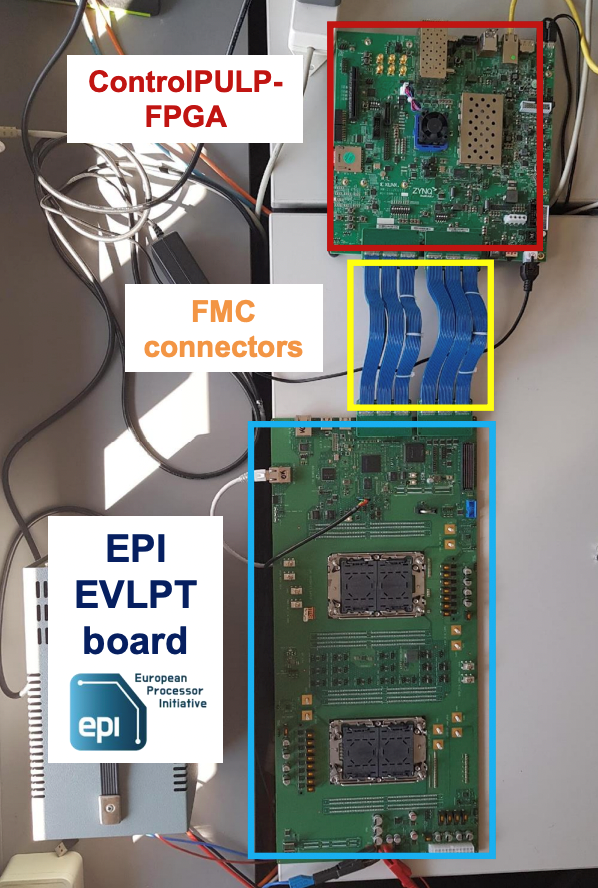

ControlPULP作為一個軟硬件完全開源的集成IP方案,不少人擔心是否真的會有人將其投入商用,事實上,這樣的案例已經快要面世了。根據ETH透露,歐洲處理器計劃(EPI)的先行者,法國企業SiPearl的E級HPC芯片,72核的Rhea處理器就將集成ControlPULP。

不過,這還只是ControlPULP邁出的第一步,未來PULP團隊還計算完成65nm的流片來進一步開展硬件驗證,并探索更先進的預測性電源控制策略。但不管怎么說,這都是首個RISC-V的HPC電源控制器方案,RISC-V在HPC市場也需要更多的亮相,而不僅僅只是作為加速器。

能做到如此高的能效,除了CPU、GPU本身的設計外,也要歸功于先進的冷卻系統和電源管理。對于已經走向多核異構時代的HPC系統而言,系統級別的電源與熱管理尤為重要,而且還得做到精心調校、針對負載進行智能調整的動態電源管理。

已有的電源控制器方案

針對不同的CPU系統,市面上已經有了不少商用電源控制器,比如英特爾的CPU有用于C-States管理的電源控制單元(PCU),ARM有幫助應用處理器卸載電源與系統管理任務的系統控制處理器(SCP)和可管理控制處理器(MCP),AMD有采集傳感數據進行快速調整的系統管理單元(SMU),IBM的Power處理器有片上控制器(OCC)等。

然而,不少已有的方案都是基于單核心的MCU打造的,在面對單片核心數越來越多以及逐漸普及的Chiplet設計時,這些方案就因為缺乏擴展性而顯得力不從心了。除此之外,主辦的尺寸、布局和成本的因素,進一步限制了HPC處理器本身的片上電源管理。正因如此,在擁有龐大核心數量的HPC系統上,我們需要一個可擴展的控制器方案。

在這些要求下,瑞士蘇黎世聯邦理工學院(ETH)的集成系統實驗室就基于開源的RISC-V架構,打造了這樣一個擁有并行控制規則計算加速的電源控制器IP——ControlPULP。

可擴展的電源控制器

ControlPULP采用了九核的設計,一個單核管理器核心,和8核的加速器簇來加速電源控制固件的工作負載,而這九個核心全部基于CV32E40P,這是一個32位4級流水線的RISC-V開源核心,由瑞士蘇黎世聯邦理工學院和意大利博羅尼亞大學合作的PULP平臺維護,他們也將CV32E40P捐獻給了開放硬件聯盟OpenHW。

ControlPULP架構 / 瑞士蘇黎世聯邦理工學院

此外,ControlPULP集成了一個直接內存訪問引擎,用于獲取片上傳感器的數據,還有一個uDMA引擎,用于支持基于標準電源管理接口(比如電壓調節總線AVSBUS/PMBUS)的片外外圍設備以及通過I2C或MTCP協議的BMC通信。至于底層控制策略的調度,則靠PULP平臺自己開發的開源FreeRTOS來實現。

在其電源控制策略中,ControlPULP主要負責兩大主要控制任務,一個是定期控制任務,一個是電源控制任務。定期控制任務結合溫度傳感器、功耗傳感器內的數據,以及目標頻率、預期負載和總功耗預算等數據,來進行電源調度和熱管理。電源控制任務則是通過PMBUS/AVSBUS獲得的電壓軌功耗和BMC通信來完成快速電源控制。

根據他們測試的結果,這種多核加速器簇的結構相較過去的單核方案來說,在控制策略的執行速度上快了5倍,而且集成在HPC處理器中并不會占用多大的面積。他們在格芯的GF22FDX工藝下得到的綜合結果中,ControlPULP所占處理器面積甚至不到百分之一。

開源電源控制器的未來

ControlPULP作為一個軟硬件完全開源的集成IP方案,不少人擔心是否真的會有人將其投入商用,事實上,這樣的案例已經快要面世了。根據ETH透露,歐洲處理器計劃(EPI)的先行者,法國企業SiPearl的E級HPC芯片,72核的Rhea處理器就將集成ControlPULP。

不過,這還只是ControlPULP邁出的第一步,未來PULP團隊還計算完成65nm的流片來進一步開展硬件驗證,并探索更先進的預測性電源控制策略。但不管怎么說,這都是首個RISC-V的HPC電源控制器方案,RISC-V在HPC市場也需要更多的亮相,而不僅僅只是作為加速器。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電源控制器

+關注

關注

0文章

150瀏覽量

32829 -

HPC

+關注

關注

0文章

318瀏覽量

23813 -

RISC-V

+關注

關注

45文章

2300瀏覽量

46261

發布評論請先 登錄

相關推薦

基于risc-v架構的芯片與linux系統兼容性討論

)、中斷控制器、I/O接口等。

Linux內核需要與這些硬件接口進行緊密配合,提供合適的驅動程序和管理機制。因此,在RISC-V架構的芯片上運行Linux系統時,需要確保Linux內核與RIS

發表于 11-30 17:20

RISC-V內核的32位通用微控制器 GD32VF103芯片簡介

1. 芯片簡介

GD32VF103系列MCU是基于RISC-V內核的32位通用微控制器,具備均衡的處理效能和系統資源,適用于工業控制、消費電子、新興IoT等嵌入式市場應用。

內核:芯

發表于 10-23 06:46

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

控制器等豐富外設資源,適于光伏、儲能電源等相關應用。

4 RISC-V+藍牙+雙USB+以太網+CAN

多種有線連接+藍牙無線,打造多形式連接的全能小網關,簡化邊緣節點組網。

06 USB/藍牙

發表于 08-30 17:37

rIsc-v的缺的是什么?

通過軟件模擬或復雜的指令序列來實現一些高級功能,這可能會增加執行時間和功耗。

2. 生態系統支持不足

軟件和工具鏈的可用性:盡管RISC-V社區在快速發展,但與成熟的ARM等架構相比,

發表于 07-29 17:18

RISC-V在中國的發展機遇有哪些場景?

:RISC-V處理器在性能和能效比方面表現出色,適用于數據中心和高性能計算領域的需求。

自主可控:RISC-V的開源特性使得中國可以在這一領域實現自主可控的技術發展,減少對外國技術的依

發表于 07-29 17:14

淺析RISC-V領先ARM的優勢

和成本要求。

ARM雖然也具有一定的可定制性,但受限于其指令集架構的復雜性和歷史包袱,其定制化的靈活性和自由度相對較低。

生態系統的快速發展:

隨著RISC-V的開源特性得到越來越多開

發表于 06-27 08:45

risc-v的mcu對RTOS兼容性如何

內存大小、中斷控制器等。

芯片制造商的支持 :

RISC-V MCU的制造商通常會提供與RTOS集成的支持,這包括驅動程序、板級支持包(BSP)以及可能的RTOS優化和補丁。

一些制造商甚至可能提供預集成

發表于 05-27 16:26

RISC-V有哪些優點和缺點

新的、尚未被廣泛驗證的技術。

需要注意的是,隨著RISC-V技術的不斷發展和生態系統的逐步完善,其缺點可能會逐漸被克服。同時,RISC-V的優點也使其在多個領域具有廣闊的應用前景,包括

發表于 04-28 09:03

RISC-V有哪些優缺點?是堅持ARM方向還是投入risc-V的懷抱?

的架構,而不是嘗試新的、尚未被廣泛驗證的技術。

需要注意的是,隨著RISC-V技術的不斷發展和生態系統的逐步完善,其缺點可能會逐漸被克服。同時,RISC-V的優點也使其在多個領域具有廣

發表于 04-28 08:51

國產RISC-V MCU推薦

也基本上符合RISC-V JTAG標準。芯片的軟件庫也較為齊全,不過在模擬性能方面,精度和可重復性相較一般。

官網顯示,GD32VF103系列MCU是

發表于 04-17 11:00

RISC-V邁入HPC市場,性能與生態缺一不可

時代,后發的RISC-V是否有機會在HPC市場占據一席之地,是不少廠商和開發者都在琢磨的問題。 ? 其實從去年開始,RISC-V就已經在往這個方向發力了,各種高性能

RISC-V 基礎學習:RISC-V 基礎介紹

10

機器特權級

3

M

11

一個RISC-V 硬件線程(hart),相當于一個CPU 內獨立的可執行核心,在任意時刻,只能運行在某一個特權級上,這個特權級由CSR(

發表于 03-12 10:25

芯來科技正式發布基于RISC-V處理器的HSM子系統解決方案

本土RISC-V CPU IP領軍企業——芯來科技正式發布基于RISC-V處理器的HSM子系統解決方案,提供專業有效的信息安全保護以及加解密

HPC系統的電源控制器,RISC-V也來插一腳?

HPC系統的電源控制器,RISC-V也來插一腳?

評論