內(nèi)核到 I/O 口的躁聲串?dāng)_

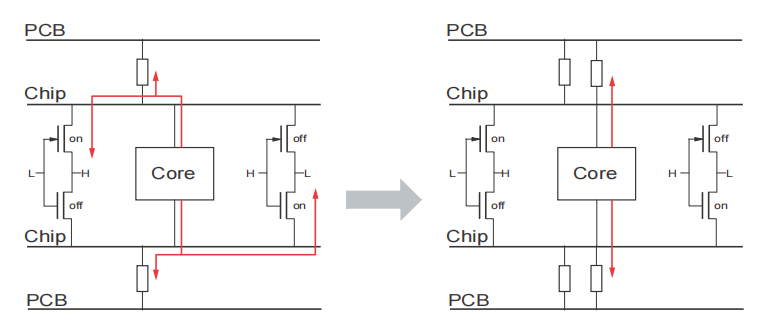

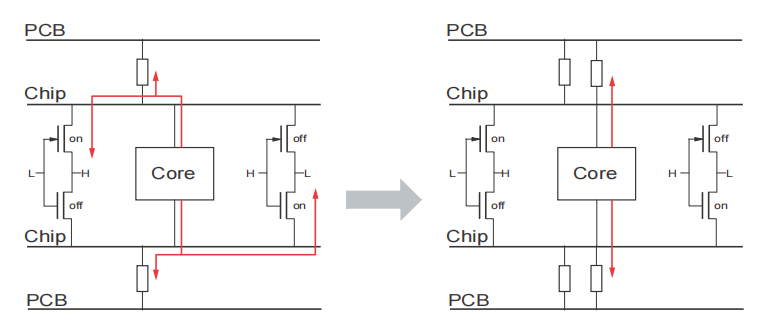

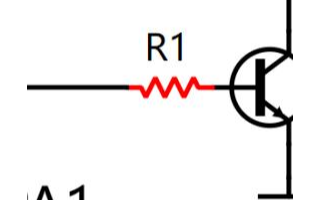

任何兩個電路在它們的供電時共用同一阻抗,彼此之間將會產(chǎn)生串?dāng)_。下例圖左邊部分說明了核和

I/O 利用同一電源的情況下的核噪聲。 這個噪聲是由與壓降相關(guān)的核電流引起的,這里的壓降是通過粘

合線和引腳自感引起的,在圖 3-3 中,以電阻的形式表示。即使 PCB 的電源電壓系統(tǒng)是遠離各種紋波電

壓,但片內(nèi)電源也是有躁聲的。因為端口緩沖區(qū)和內(nèi)核是同一種內(nèi)部電源,噪聲通過激活的晶體管傳遞到

每個輸出接腳,這不僅影響輸出管腳,還影響輸入引腳,輸入引腳被影響取決于芯片內(nèi)部的寄生電容(例

如保護電路)。 在對 EME 敏感的情況下,可能需要對每一個引腳濾波,至少對于多引腳的微控制器,這是

基于成本和空間的原因。

共用與隔離電源的串?dāng)_

審核編輯 黃昊宇

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

相關(guān)推薦

,ADC是SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數(shù)字信號處理之后再畫到顯示屏上顯示實時波形。

調(diào)試發(fā)現(xiàn)顯示的信號有串擾,表現(xiàn)為某一路信號懸空之后,相

發(fā)表于 01-07 06:15

改善串擾的設(shè)計方法據(jù)說有兩種:很多人知道的方法:信號線之間通過“包地”改善串擾……幾乎只有高速先生知道的方法:信號線之間通過“割地”改善串

![的頭像]() 發(fā)表于

發(fā)表于 11-11 17:26

?260次閱讀

IO口和串口的區(qū)別 IO口,即輸入輸出端口(Input/Output Port),是單片機或其他微控制器與外部設(shè)備之間進行數(shù)據(jù)交換的接口。它們通常用于控制外部設(shè)備的狀態(tài),如LED燈的亮

![的頭像]() 發(fā)表于

發(fā)表于 10-06 10:06

?1895次閱讀

MCU(微控制器)的IO口(Input/Output Port,輸入輸出端口)是單片機與外界進行信息交互的關(guān)鍵接口。這些IO口在微控制器的功

![的頭像]() 發(fā)表于

發(fā)表于 09-30 11:52

?1016次閱讀

在高頻電路的精密布局中,信號線的近距離平行布線往往成為引發(fā)“串擾”現(xiàn)象的潛在因素。串擾,這一術(shù)語描述的是未直接相連的信號線間因電磁耦合而產(chǎn)生的不期望

![的頭像]() 發(fā)表于

發(fā)表于 09-25 16:04

?319次閱讀

單片機IO口配置成輸出口的過程通常涉及對單片機內(nèi)部寄存器的操作。不同型號的單片機在寄存器配置和編程方式上可能有所不同,但基本原理是相似的。以下是一個通用的步驟,用于將單片機IO口配置成

![的頭像]() 發(fā)表于

發(fā)表于 09-14 14:33

?912次閱讀

單片機IO口的輸出電流大小會受到多種因素的影響,包括單片機的型號、IO口的配置模式以及外部電路的設(shè)計等。以下是對單片機IO

![的頭像]() 發(fā)表于

發(fā)表于 09-14 14:29

?2218次閱讀

信號串擾(Crosstalk)是指在信號傳輸過程中,一條信號線上的信號對相鄰信號線產(chǎn)生的干擾,這種干擾是由于電磁場耦合或直接電容、電感耦合引起的。根據(jù)耦合類型和位置的不同,信號串擾主要

![的頭像]() 發(fā)表于

發(fā)表于 09-12 08:08

?1380次閱讀

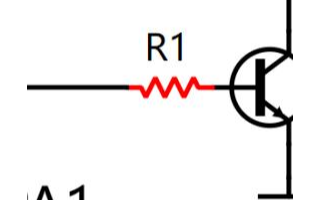

拉電流就是流出,灌電流就是流入,二者都是有限制的,不可超過IC規(guī)格書中規(guī)定的最大值。回到我們最開始的問題,當(dāng)MCU IO口用作輸出和輸入時要串聯(lián)多大的電阻才合適呢?其實就是去查閱MCU

![的頭像]() 發(fā)表于

發(fā)表于 09-09 18:34

?4087次閱讀

電子發(fā)燒友網(wǎng)站提供《緩解ADC存儲器串擾的方法.pdf》資料免費下載

發(fā)表于 09-06 10:15

?0次下載

德索工程師說道要減少M9航空接口3芯的串擾,首先需要深入了解串擾產(chǎn)生的原因。串擾通常是由于電磁耦

![的頭像]() 發(fā)表于

發(fā)表于 04-26 16:11

?418次閱讀

mcu儀器儀表

安泰儀器維修

發(fā)布于 :2024年04月01日 15:25:47

電路布線常會有串擾的風(fēng)險,最后簡單說明幾個減小串擾的方法,常見增大走線間距、使兩導(dǎo)體的有串擾風(fēng)險的區(qū)域最小化、相鄰層走線時傳輸線互相彼此垂直

發(fā)表于 03-07 09:30

?1864次閱讀

串擾,也稱為串音干擾,是指由于線路之間的電磁耦合導(dǎo)致的信號和噪聲的傳播。串擾可以引起信號質(zhì)量下降、數(shù)據(jù)錯誤和系統(tǒng)性能受限,因此在高速數(shù)字設(shè)計

![的頭像]() 發(fā)表于

發(fā)表于 02-04 18:17

?1986次閱讀

在PCB設(shè)計中,如何避免串擾? 在PCB設(shè)計中,避免串擾是至關(guān)重要的,因為串擾可能導(dǎo)致信號失真、

![的頭像]() 發(fā)表于

發(fā)表于 02-02 15:40

?1881次閱讀

MCU—IO口的噪聲串?dāng)_

MCU—IO口的噪聲串?dāng)_

評論