本文主要來源為學堂在線《IC設計與方法》學習筆記

Quarus Ⅱ工具的整體編譯過程包括邏輯綜合、布局布線、時序分析、I/O分析(個人理解芯片引腳的分析)等編譯子過程。

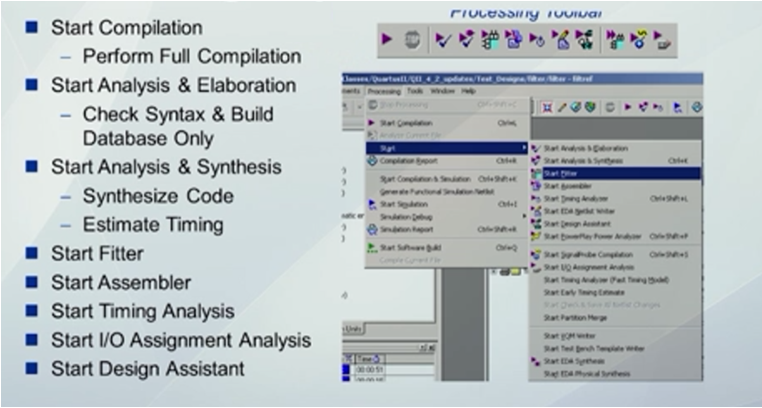

Quarus Ⅱ工具提供了如圖一右上角的工具條,設計人員可以直接點擊工具條第一個紫色的三角形按鈕完成整體編譯過程,也可通過點擊其他帶有紫色三角形的按鈕完成某一子過程的編譯。

對于簡單的芯片設計,設計人員可以點擊一個按鈕完成整體編譯過程。對于復雜的芯片設計,邏輯綜合、布局布線、時序分析子過程可能需要花費數小時到數天的時間。如果每次編譯都進行整體編譯,會浪費時間,所以復雜的芯片設計通常分步完成每個子過程的編譯。

圖一,圖片來源:學堂在線《IC設計與方法》

設計人員需要關注Quarus Ⅱ工具提供的報告。

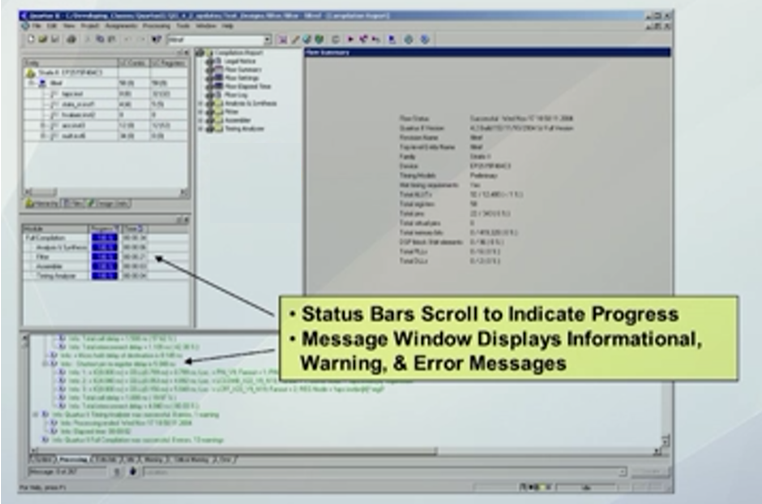

圖二左側中間帶有多個藍色進度條的窗口會報告編譯過程是否百分之百正確,如果編譯有錯誤,Quarus Ⅱ工具可能會在錯誤處停滯。

圖二最靠下寫有綠色文字的窗口會報告編譯過程的一些相關信息,設計人員需要仔細檢查是否有error或warning,除非可以確認warning對芯片設計沒有影響,否則設計人員需要排除所有的error或warning。

圖二,圖片來源:學堂在線《IC設計與方法》

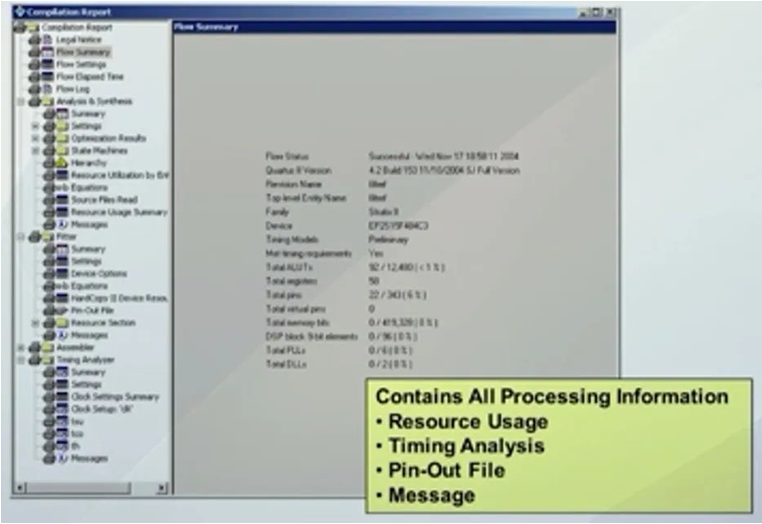

圖三是圖二右上角部分的放大,展示的是Quarus Ⅱ工具可以報告每一編譯子過程的相關信息,如邏輯綜合、時序分析、I/O分析等相關信息。

圖三,圖片來源:學堂在線《IC設計與方法》

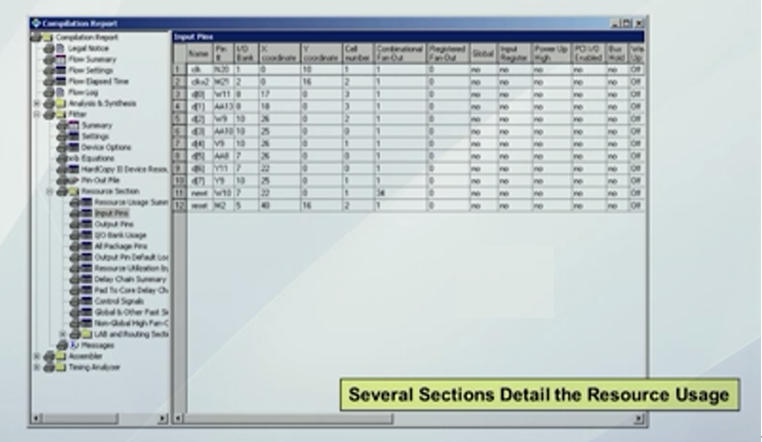

圖四是Quarus Ⅱ工具對芯片引腳資源使用(I/O分析)情況的報告,包括輸入引腳的信號、名稱、是否為特殊引腳等信息。

圖四,圖片來源:學堂在線《IC設計與方法》

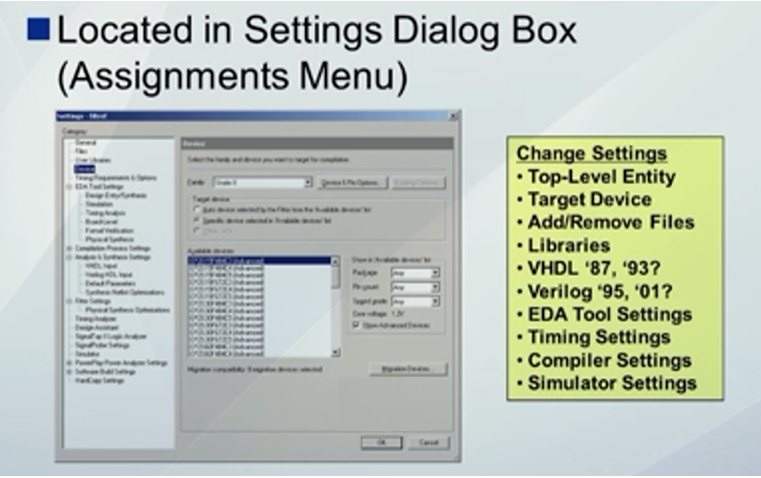

圖五展示了Quarus Ⅱ工具邏輯綜合(將芯片代碼設計轉化成電路設計)相關設置界面,需要設計人員檢查的設置包括頂層樹狀結構(Quarus Ⅱ工具會分析芯片設計的樹狀結構)、目標器件的類型、設計文件和庫文件、代碼語法標準(確定語法標準采用的版本)、EDA(邏輯綜合所使用的平臺)工具的選擇(Quarus Ⅱ工具內嵌的工具或其他EDA工具)、時序分析設置、邏輯綜合操作設置、仿真工具設置。

圖五,圖片來源:學堂在線《IC設計與方法》

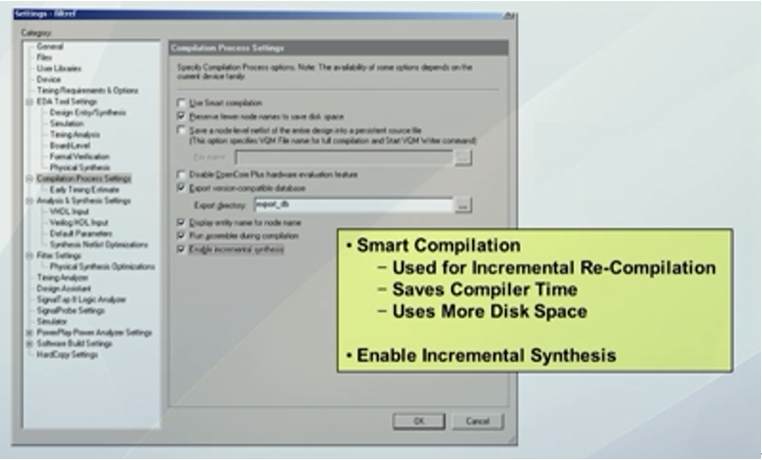

Quarus Ⅱ工具可以提供多種邏輯綜合的方法,如智能綜合,智能綜合采用增量綜合方式,可以節省時間和磁盤空間。其他的邏輯綜合的方法還包括:節省綜合時間的綜合方法和使用更多磁盤空間的綜合方法(這兩種方法課程中未提及,根據圖六翻譯)。

圖六,圖片來源:學堂在線《IC設計與方法》

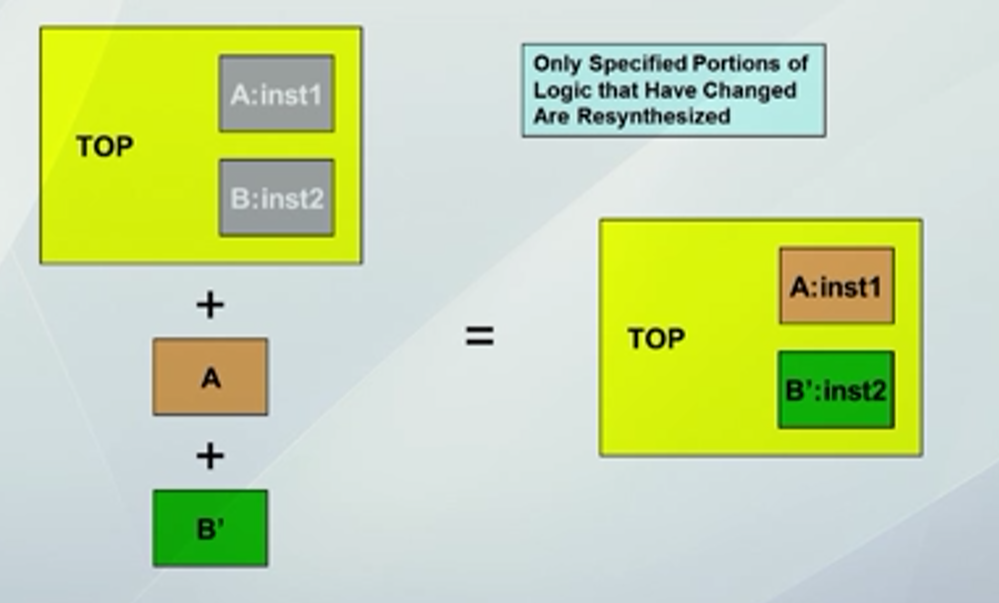

上文提及的增量綜合通過只對電路修改部分進行再次邏輯綜合,節省時間和磁盤空間。

如圖七所示,芯片頂層設計(TOP)包含設計A和B的連接方式,設計A、B的底層設計(具體設計內容)分別包含于A、B中。若第一次邏輯綜合后,問題只出現在B的底層設計中,在修改出問題的設計后,軟件可以通過只對修改部分(個人理解:頂層設計部分和B的底層設計可能均發生修改,A的底層設計沒有修改)進行邏輯綜合,以節省時間和磁盤空間。

圖七,圖片來源:學堂在線《IC設計與方法》

-

IC設計

+關注

關注

38文章

1304瀏覽量

104544 -

編譯

+關注

關注

0文章

666瀏覽量

33213 -

可編程芯片

+關注

關注

0文章

53瀏覽量

18690

原文標題:芯片設計相關介紹(28)——Quarus Ⅱ工具部分功能簡介(上)

文章出處:【微信號:行業學習與研究,微信公眾號:行業學習與研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種基于Logical Effort理論的IC設計方法解析

增大三極管集電極電流Ic的方法

咨詢:增大三極管集電極電流Ic的方法

低功耗數字IC設計方法及示例

嵌入式SoC IC 的設計方法和流程

一種全新的深亞微米IC設計方法

基于Logical Effort理論的全新IC設計方法

傳統MEMS-IC 設計方法和驗證的機構化方法介紹

PCB電路設計代換IC的技巧與方法

ic設計是什么專業_IC設計的設計方法

簡述進行?IC設計的方法和設計流程

IC設計與方法

IC設計與方法

評論