IBIS建模——第2部分:為何以及如何創建您自己的IBIS模型

【導讀】本文提供有關在創建IBIS模型時如何使用LTspice?的說明指南,涵蓋從IBIS預建模程序到IBIS模型驗證的整個過程。本文還詳細介紹如何在LTspice中為IBIS模型準確提取I-V、V-T、斜坡和C_comp數據。此外,還提供定性和定量FOM方法,用于驗證IBIS模型的性能。該應用案例展示了為假設的ADxxxx三態數字緩沖器開發IBIS模型的過程,其中包含適合輸入和三態CMOS接口的可用IBIS模板,有助于即刻開始創建您的IBIS模型。

簡介

在構建任何系統時,仿真都發揮著關鍵作用。它幫助設計人員預見問題,進而避免費時且成本高昂的修改。我們的目標始終是一次就成功!在仿真高速數字接口時,如果設計不當,簡單的PCB走線可能會影響信號質量。在信號完整性仿真中,IBIS(輸入/輸出緩沖器信息規范)模型用來表示器件的數字接口。

如IBIS系列文章的第1部分所述,IBIS是一個行為模型,通過以表格形式列出的電流與電壓(I-V)和電壓與時間(V-T)數據來描述器件的數字接口的電氣特征。IBIS模型應盡量準確,且不含任何解析錯誤,避免在之后使用時出現問題。此外,對于具有數字接口的每個部件或器件,都應該提供可用的IBIS模型。這樣客戶需要時,可直接從制造商的網頁上下載。但是,事實并非總是如此。對于IBIS模型用戶,他們常遇到的一個問題就是模型的可用性。當他們在設計中選用的部件沒有IBIS模型時,其產品開發可能受阻。

IBIS模型最好是由其制造商提供;但是,用戶也可以創建IBIS模型。本文介紹如何使用LTspice,基于SPICE模型創建最基礎的IBIS模型。下文使用IBIS建模手冊(IBIS 4.0版)中的規格來介紹LTspice仿真設置。還要介紹如何使用定性和定量品質因數來驗證IBIS模型。

何謂“最基本的”IBIS模型?

為了幫助客戶使用LTspice創建基本的IBIS模型,需要先定義“基本”一詞。基本的IBIS模型不僅取決于I/O模型關鍵字,還取決于需要建模的數字緩沖器的類型。這意味著需要重新審視IBIS的早期版本,以定義建立緩沖器模型需要滿足的最低要求,以及當時建模的數字接口的類型。事實證明,單端CMOS緩沖器是可以使用IBIS建模的最簡單的數字IO之一,本文將予以介紹。

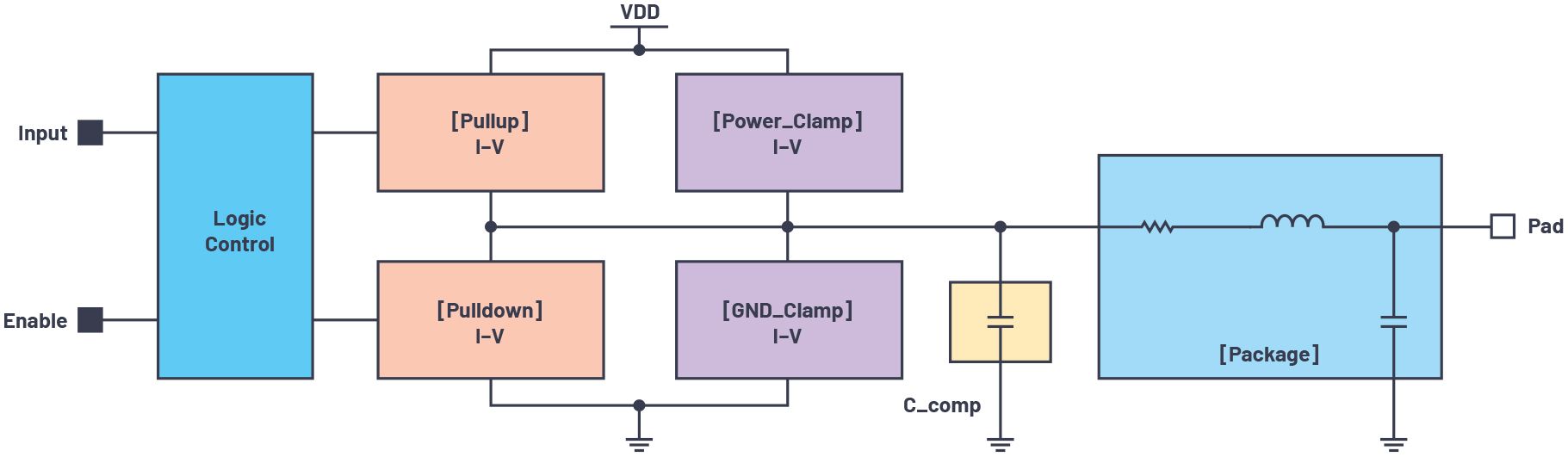

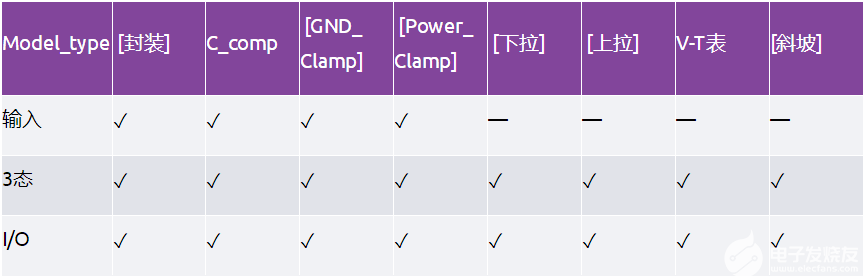

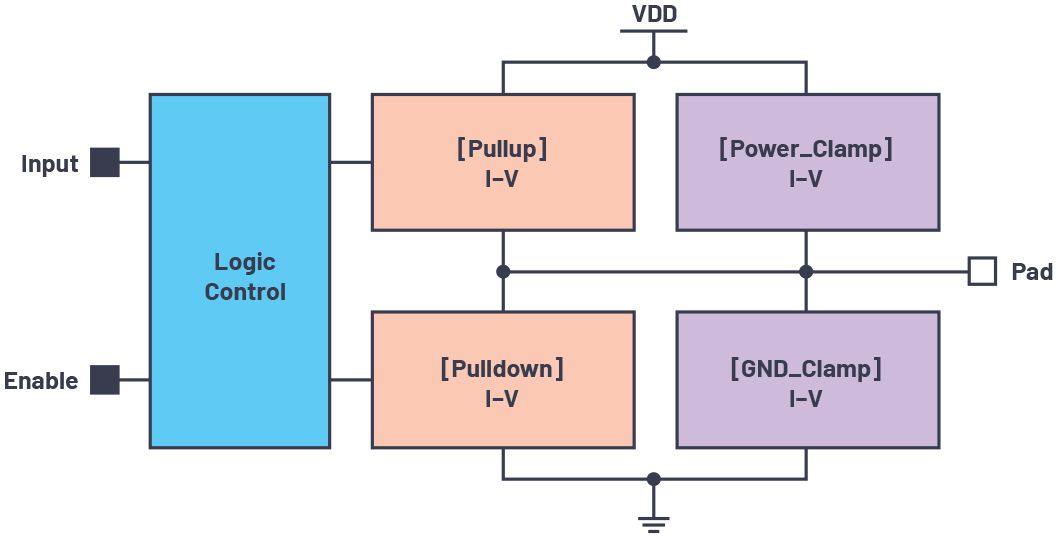

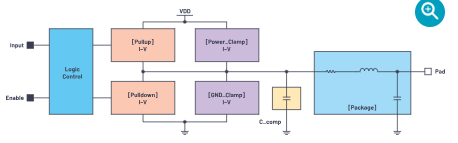

圖1.3態CMOS緩沖器的IBIS模型

表1.基于Model_type的IBIS模型組件匯總

圖1顯示3態CMOS緩沖器IBIS模型的結構。如第1部分所述,IBIS模型中的組件或關鍵字取決于模型類型。表1匯總列出基本的IBIS模型的組件,具體由Model_type決定。

應用案例

在本文中,我們將使用一個假設的ADxxxx器件的LTspice模型來創建IBIS模型。它是一個帶有使能引腳的單輸入和單輸出數字緩沖器。因此,得到的IBIS模型將具有兩個輸入(DIN1和EN)、一個三態輸出(DOUT1)。

一般來說,生成IBIS模型有五個基本步驟:

● 建立預建模程序。

● 對從SPICE模型中提取的C_comp、V-I和V-T數據進行LTspice仿真。

● 格式化IBIS文件。

● 使用IBIS解析器測試檢查文件。

● 比較IBIS模型與SPICE模型在相同加載條件下的仿真結果。

IBIS模型提供典型數據、最小數據和最大數據。它們通過工作電源電壓范圍、溫度和工藝來確定[HA1] 。為簡潔起見,本文只討論典型條件。

Ibischk Golden Parser系列可用于檢查IBIS模型是否符合IBIS規范。ibischk可執行文件可從IBIS.ORG網頁免費獲取。本文使用集成ibischk的第三方IBIS模型編輯軟件。

預建模程序

在開始仿真之前,用戶應該下載器件的數據手冊,并安裝SPICE模型和LTspice文件。通過確定部件具備的數字接口數量和類型(例如,輸入、開漏、三態等),對部件進行初始評估。

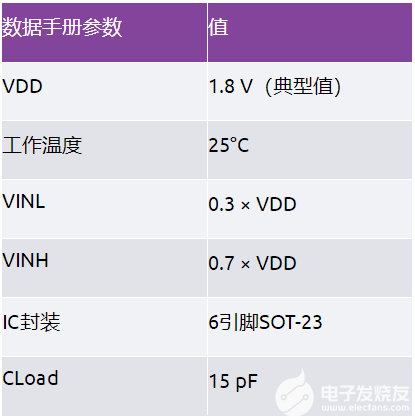

根據器件數據手冊,確定工作電源電壓、工作溫度、集成電路(IC)封裝類型、器件引腳排列、數字輸出時序規格的加載條件(RLoad和/或CLoad),以及數字輸入的低電平輸入電壓(VINL)和高電平輸入電壓(VINH)。ADxxx SPICE模型如圖1所示,其指標參數列在表2。

通過使用關鍵字,將有關器件數字接口的所有信息匯集到一個IBIS文件中。關鍵字是IBIS模型中用括號括起來的標識符,如第1部分所述。更多詳細信息請參閱此部分內容。

圖2.Adxxxx 3態數字緩沖器SPICE模型。

表2.ADxxxx數據手冊參數

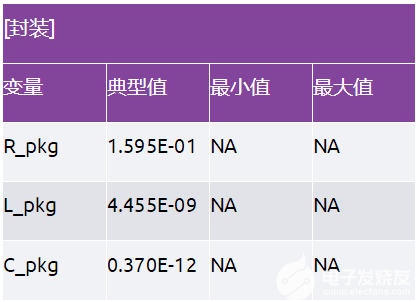

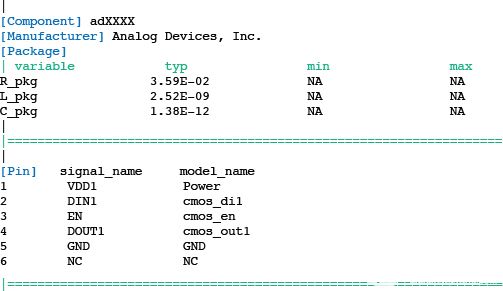

與IC封裝模型相關的關鍵字是[Package]。它包含RLC(電阻-電感-電容)寄生參數,代表從芯片焊盤到IC焊盤/引腳的連接。此信息可從制造商處獲得。也可以查找另一個IBIS文件的[Package]數據,只要該器件采用的封裝與正在評估的器件完全相同,并且來自同一制造商。6引腳SOT-23封裝的器件封裝寄生參數如表3所示。

表3.6引腳SOT-23封裝寄生參數

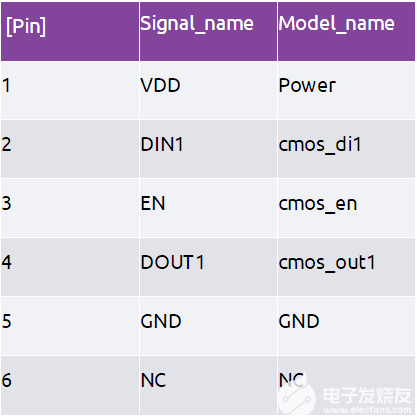

器件引腳排列如表4所示。關鍵字[Pin]用于描述引腳及其對應的模型名稱。[Pin]一般為3列格式。第一列是引腳編號,第二列是引腳描述,第三列是模型名稱。有些封裝包含[HA2] 類似的引腳(VCC、GND)。這些引腳可以按模型分組和描述。在這種情況下,由于SPICE模型沒有給出有關內部晶體管級原理圖的信息,因此最好為每個數字接口創建單獨的模型。在IBIS文件中,模型名稱“Power”和“GND”用于命名電源和接地引腳。非數字接口和“請勿連接”引腳則描述為“NC”或無連接。請注意,模型名稱是區分大小寫的。由于在稍后的建模程序中還會用到,所以需給出具體的模型名稱。

表4.ADxxxx引腳列表

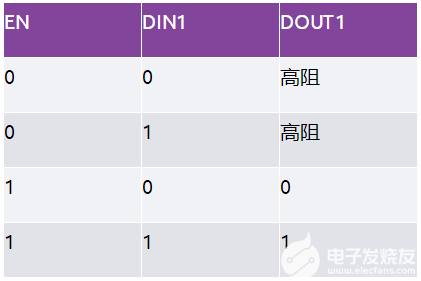

ADxxxx真值表如表5所示。這在建立LTspice仿真時非常有用。還必須要知道如何將DOUT1引腳設置為高阻抗(高阻)模式、邏輯1和邏輯0。

表5.ADxxxx真值表

LTspice設置和仿真

一般來說,IBIS模型通過前面提到的I-V(電流與電壓)和V-T(電壓與時間)數據描述數字緩沖器的行為。進行IBIS建模時,每種類型的數字接口都擁有[HA3] 一組自己的I-V和/或V-T數據,如表1所示。表6更加詳細地列出了這些數據集。注意查看每個數據集的注釋。那些標記為“推薦”的數據,表示這些數據缺失不會在ibischk解析器測試中導致誤差。但是,這些數據集對通道仿真有一定的作用。例如,鉗位數據有助于分析信號反射。

表6.輸入和3態接口的I-V和V-T數據集

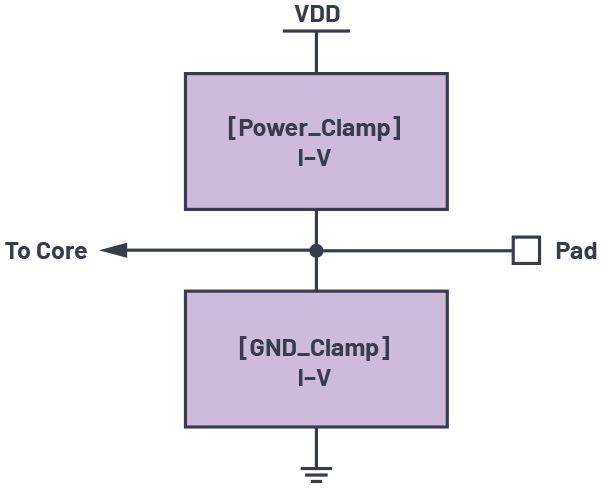

[Power_Clamp]和[GND_Clamp]

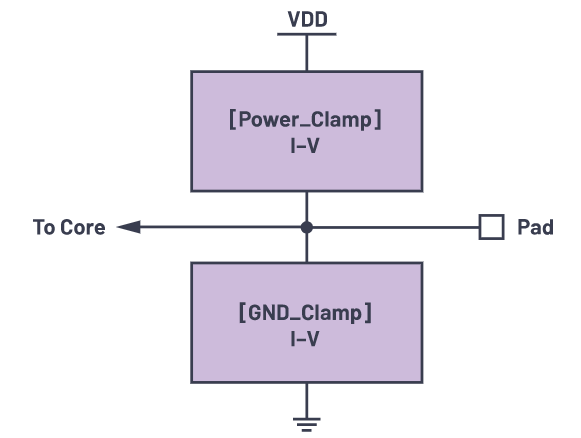

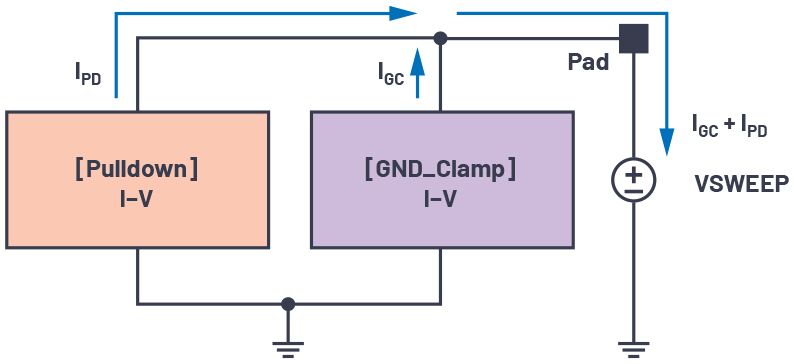

圖3.[Power_Clamp]和[GND_Clamp]關鍵字結構的概念圖

[GND_Clamp]和[Power_Clamp]通過以表格形式列出的I-V數據顯示數字緩沖器的靜電放電(ESD)器件的行為。[Power_Clamp]表示以VDD為基準的ESD器件的整體行為,接地箝位表示以GND為基準的ESD器件的整體行為。

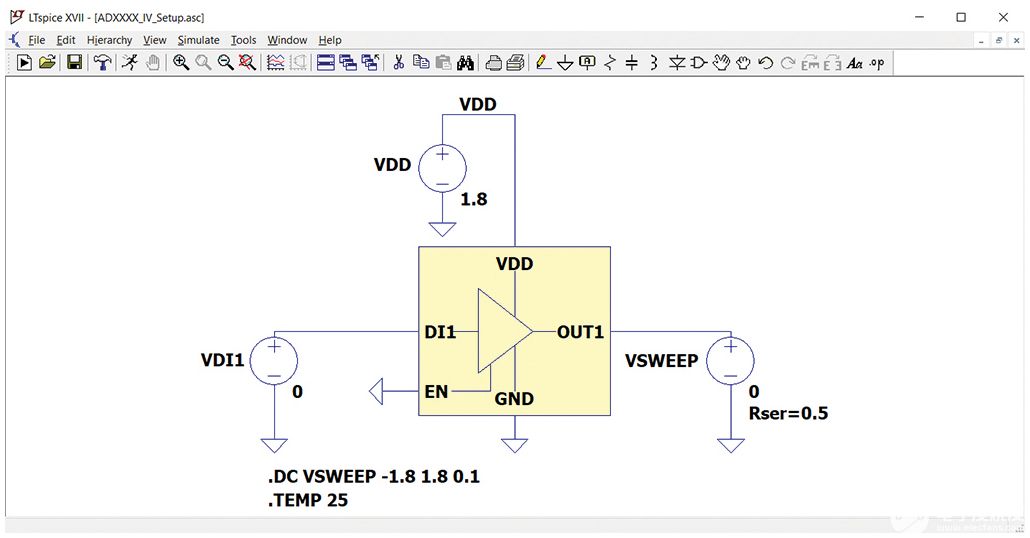

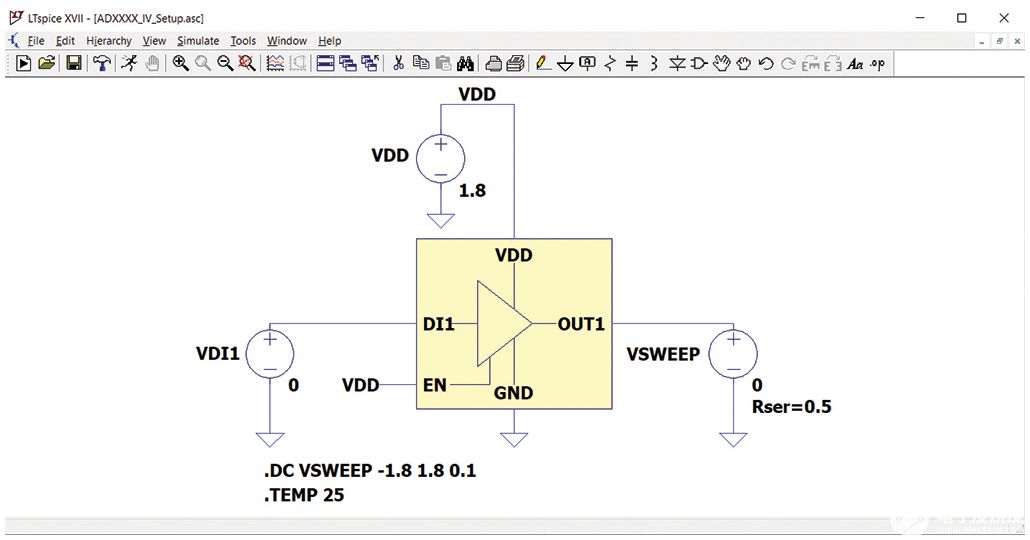

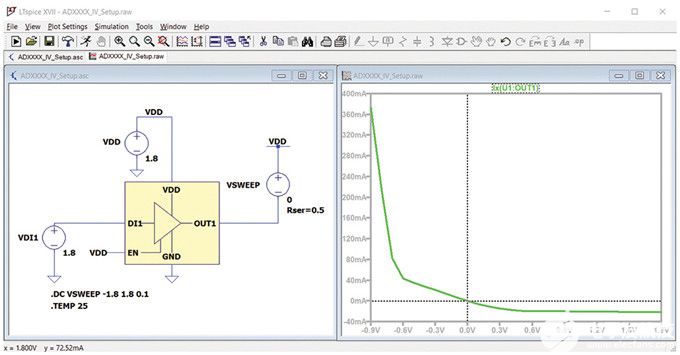

在LTspice中,I-V數據可以使用.DC SPICE命令/指令進行測量。DOUT1的接地箝位用圖4所示設置進行測量。在該設置中,使用適當的電源電壓將該器件配置為高阻態模式(請參見表5)。這可以確保將ESD器件與核心電路隔離。VSWEEP是以GND為基準的掃描電壓。使VSWEEP基準電壓接地,確保只顯示GND箝位ESD器件的特征。

根據IBIS規格,應掃描電壓軌以外(最好從-VDD到2 × VDD)的I-V數據,本例中是從–1.8 V到+3.6 V。通過直接執行此操作,掃描VDD以外的電壓將會開啟電源箝位ESD器件。為了避免這種情況,首先在–1.8 V至+1.8 V范圍內掃描VSWEEP,并使用外推方法添加3.6 V數據點。此方法適用于所有I-V數據集。

另外,請注意所有I-V數據集最多只接受100個數據點。如果數據點超過這個數目,在ibischk解析器測試中會提示錯誤。設置.DC命令的增量,使得到的數據點數量小于或等于99。這是為了容納用于2 × VDD外推的一個額外數據點。

進行直流掃描時,仿真中可能出現非常大的反向電流。要解決這個問題,將起始掃描從近似二極管勢壘電位(-0.7 V)設置為VDD (+1.8 V)。然后將數據外推至符合–VDD至2 × VDD I-V數據。另一種方法是將一個小電阻Rser與VSWEEP串聯,以限制極端電流。

圖4.ADxxxx DOUT1接地箝位設置

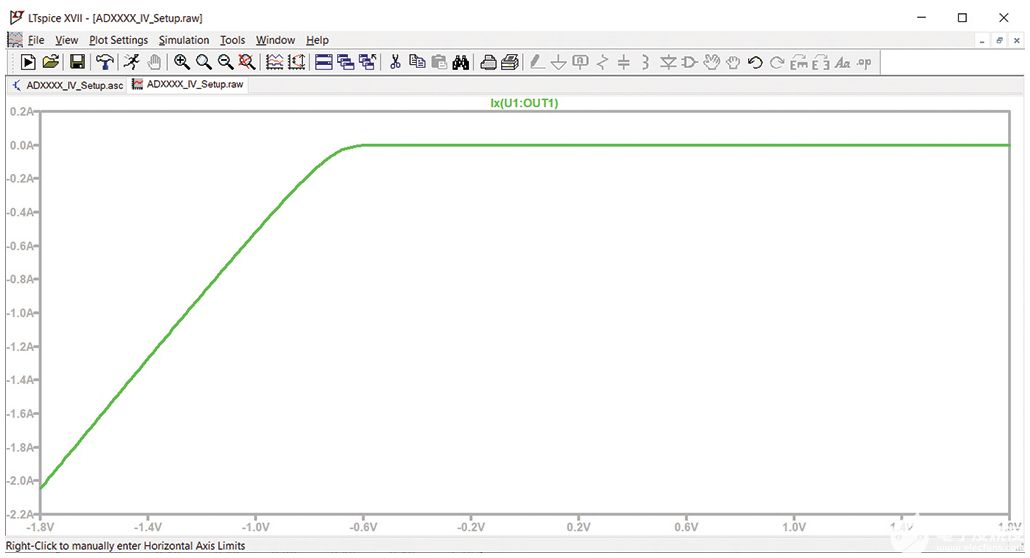

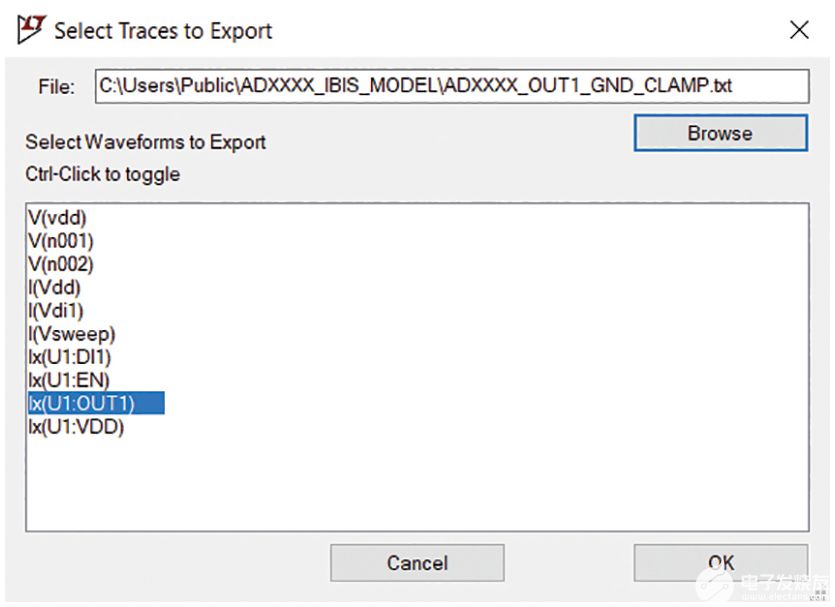

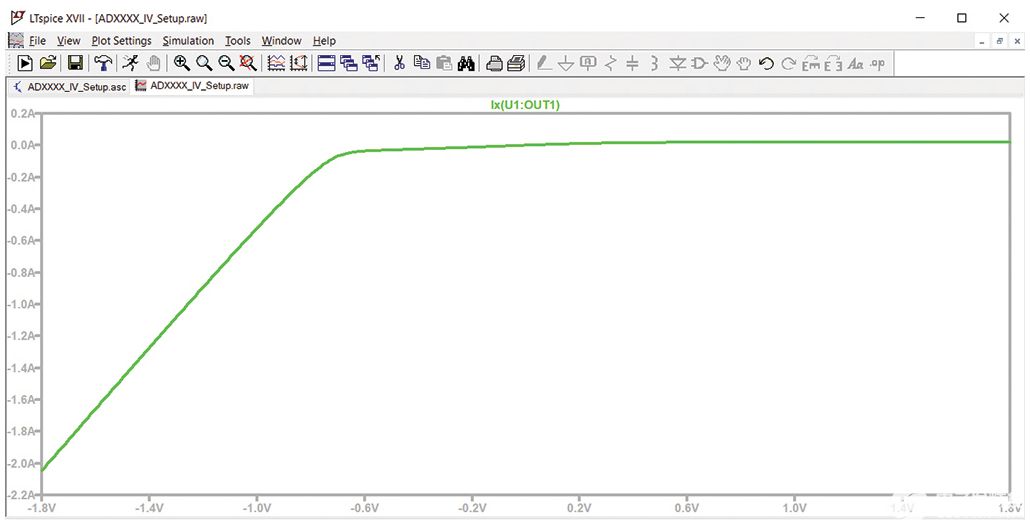

單擊運行按鈕,LTspice開始運行仿真。由于正在評估DOUT1,所以目標節點為Ix(U1:DOUT1)。雖然從技術角度來看I(VSWEEP)也是正確的,但IBIS模型需要Ix(U1:DOUT1)上的電流極性。這是為了最大限度減少I(VSWEEP)數據的進一步格式化,使其適合模型。結果應該如圖5所示。仿真完成后,先單擊結果窗口保存數據,然后單擊文件 -> 將數據導出為文本。導航至要保存的目錄,單擊受測節點,然后單擊OK(如圖6所示)。

圖5.接地箝位仿真結果

圖6.將仿真數據導出為文本

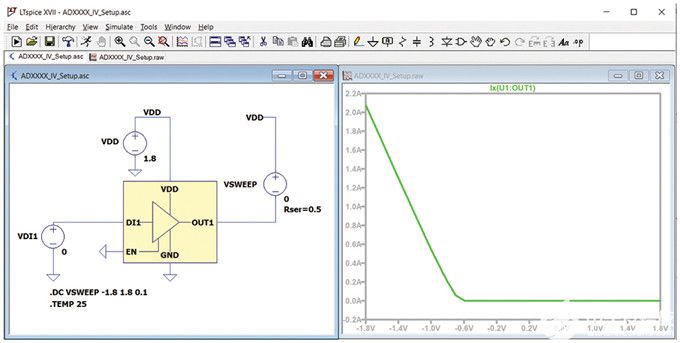

[Power_Clamp]數據提取與接地箝位設置類似,因此掃描電壓VSWEEP以VDD為基準。設置和結果如圖7所示。

圖7.ADxxxx OUT1電源箝位設置和結果

[下拉]和[上拉]

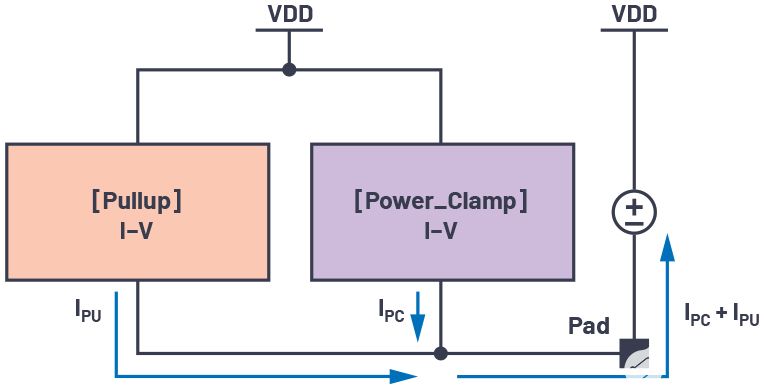

圖8.I-V關鍵字結構的概念圖

圖8顯示了I-V關鍵字結構的概念圖。[下拉]和[上拉]表示緩沖器中上拉和下拉元素的行為。如果以圖表形式表示,它們看起來就像MOSFET的I-V特征曲線。在提取[下拉]和[上拉]數據時,了解如何通過器件的真值表操控從輸出引腳輸出的信號非常重要。提取[下拉]和[上拉]數據的設置與[GND_Clamp]和[Power_Clamp]類似,即DOUT1引腳使能,且不處于高阻模式。

要提取[下拉]數據,DOUT1引腳應設置為邏輯0輸出或0 V。所以,必須設置適當的電源電壓,如圖9所示。對EN引腳施加1.8 V的等效邏輯高壓,以使能DOUT1引腳,對DIN1引腳施加邏輯0或0 V,將DOUT1引腳設置為邏輯0輸出。可以通過真值表(表5)進行確認。結果如圖10所示。

圖9.ADxxxx OUT1下拉設置

圖10.ADxxxx OUT1下拉圖

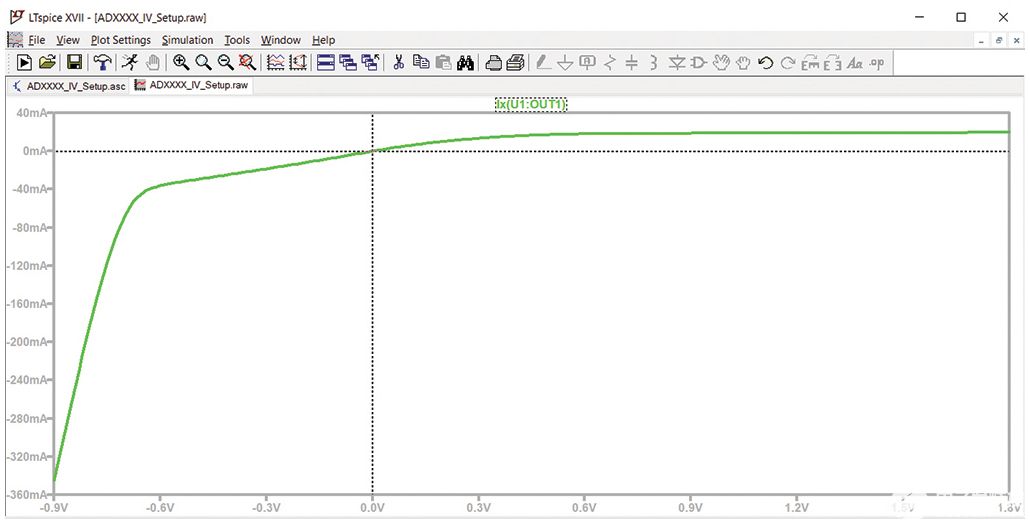

放大[下拉]數據,它類似于MOSFET的I-V特征曲線,如圖11所示。

圖11.ADxxxx DOUT1下拉圖(縮放視圖)

在保存下拉數據時,請注意它構成了[GND_Clamp]和[下拉]的總電流。圖12可以更好地說明這一點。要移除[GND_Clamp]組件,只需從[下拉]保存數據中逐點減去它。為了簡化這一操作,[GND_Clamp]和[下拉]直流分析的電壓增量、開始電壓和結束電壓必須相同。

圖12.來自下拉保存數據的實際電流

獲取上拉數據的設置如圖13所示。提供適當的電源電壓,以將DOUT1設置為邏輯1 (1.8 V)。這將確保上拉元件激活/開啟。然后,VSWEEP也在–1.8 V至+1.8 V范圍內掃描,并且以VDD為基準。以這種方式連接VSWEEP,可以防止用戶格式化數據以符合IBIS規范。

圖13.ADxxxx DOUT1上拉設置和結果

與[下拉]一樣,保存的[上拉]數據是從[Power_ Clamp]和[上拉]總電流得出的結果。因此,用戶需要從保存的[上拉]數據中逐點減去數據,以去除[Power_Clamp]組件,如果它們的直流掃描參數相同,這很容易完成。提醒大家,對所有的I-V數據測量使用相同的直流掃描參數。

圖14.來自保存的[上拉]數據的實際電流

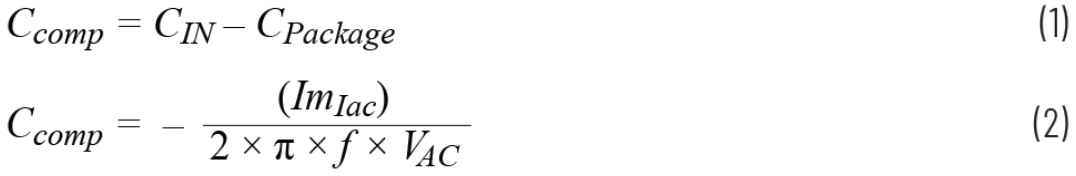

[C_comp]

[C_comp]關鍵字代表緩沖器的電容,其最小、典型和最大拐角的值各不相同。它是晶體管和裸片的電容,與封裝電容不同。可以采用兩種方式提取[C_comp]。當引腳由交流電壓供電時,可以使用方程1中的公式來得出近似值,也可以使用方程2中的公式進行計算。

其中:

ImIac:被測電流的虛值

F:交流電源的頻率

VAC:交流電源的幅度

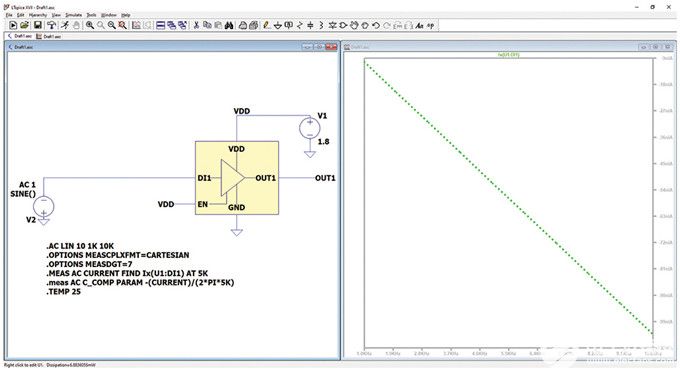

使用LTspice進行C_Comp提取

如圖15所示,可以通過提供交流電壓和頻率掃描來提取緩沖器電容。由于提供的是交流電壓,所以要測量電流的實部和虛部部分。當用交流電壓供電時,必須反轉電流的極性,以測量緩沖器的輸入電流值。測量輸出緩沖器電容時,對于圖15所示的圖,唯一要做的更改就是必須將交流電源連接至輸出引腳。

圖15.ADxxxx C_comp提取設置

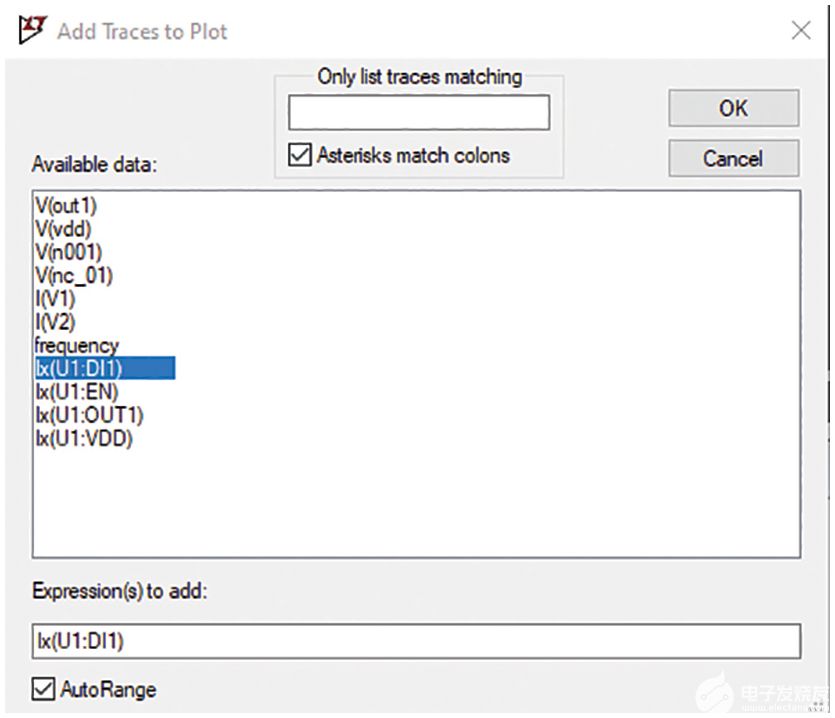

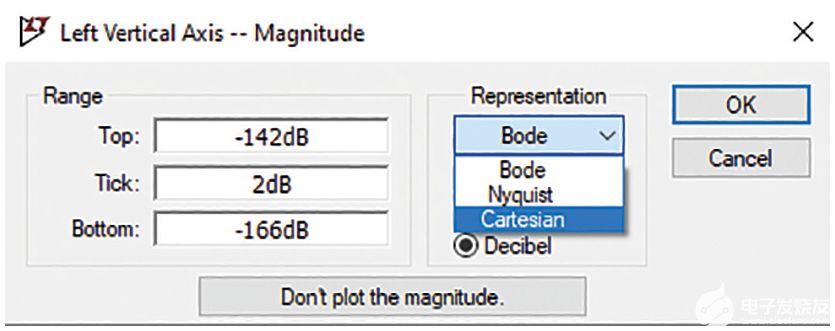

交流電壓的幅值可以是任意值,但通常設置為1 V。它將按照SPICE指令進行頻率掃描。使用.AC命令繪制波形時,默認設置為以波特模式顯示,單位為dB。必須將其設置為笛卡爾模式才能查看電流值,這樣可以直接使用緩沖器電容公式進行處理。要查看緩沖器電容波形,用戶必須先右鍵單擊波形窗口,然后單擊添加走線,再選擇被測量的引腳。波形圖窗口將顯示兩條線。

實線表示被測電流的實部,虛線表示被測電流的虛部。

圖16.向圖中添加走線對話框

若要將圖形設置從波特改為笛卡爾,右鍵單擊波形窗口左側的y軸,以打開左縱軸—幅度對話框。然后將圖示方式從波特改為笛卡爾。

圖17.將圖設置從波特改成笛卡爾

用于C_Comp設置的LTspice指令

LTspice指令用于設置電路的工作模式、測量變量和過程參數,以計算C_comp。以下是用來測量緩沖器的C_comp值的LTspice指令:

● AC Lin 10 1k 10k:將電路的工作模式設置為從1 kHz至10 kHz的交流線性頻率掃描。

● .Options meascplxfmt:將.meas命令的默認結果更改為波特、奈奎斯特或笛卡爾模式。

● .Options measdgt:設置.meas語句的有效數字位數。

● .meas語句:這些指令用來找出電路中某些參數的值。

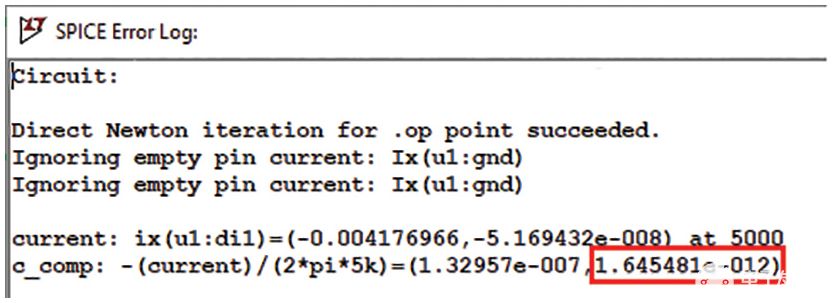

這些SPICE指令可以根據用戶想要顯示的參數進行修改。有關在LTspice中可使用的指令的詳細說明,請參閱LTspice Help。測量語句的結果可以在工具 > SPICE錯誤日志中查看。

圖18.SPICE錯誤日志中的測量語句結果。

SPICE錯誤日志中顯示的結果將采用笛卡爾形式。X坐標為電流和緩沖電容的實部,Y坐標為電流和緩沖器電容的虛部。如上所述,在測量緩沖器電容時,電流的虛部是緩沖器電容所需的部分,所以C_comp的實際值就是圖18中突出顯示的值。

[上升波形]和[下降波形]

什么是上升和下降波形?

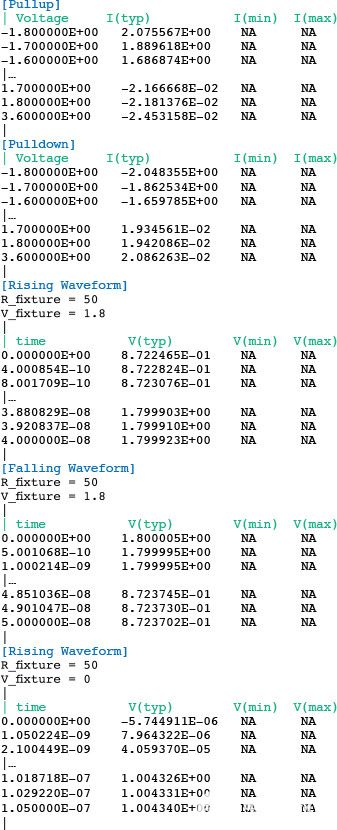

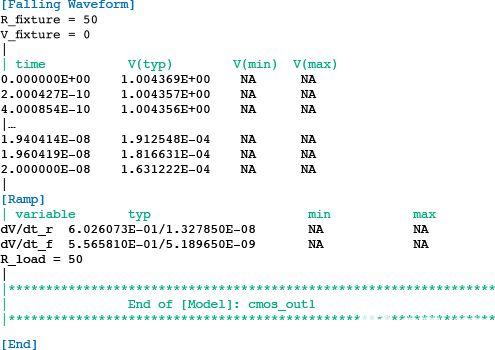

[上升波形]和[下降波形]關鍵詞模擬輸出緩沖器的切換行為。對于輸出模型,建議包含四個V-T數據集:上升和下降波形,以地為基準加載;上升和下降波形,以VDD為基準加載。

提取上升和下降V-T數據

要在LTspice中提取OUT1的上升或下降波形,以分段線性(PWL)信號或將脈沖電壓電源的形式向輸入引腳發送上升沿或下降沿輸入激勵。仿真中使用的輸入刺激的轉換必須要快,以便為模型提取出最快的輸出轉換。在測量輸出引腳的電壓時,將使用.TRAN命令對原理圖進行瞬態分析。將一個50 Ω電阻用作負載,用于提取3態輸出緩沖器的4個V-T波形的數據,但它可能會因緩沖器設計和驅動能力有所不同,以進行輸出轉換。50 Ω為V-T數據提取的默認加載值,因為它是PCB走線電阻的典型值。將50 Ω負載連接到緩沖器相對地(加載至接地)或VDD(加載至VDD)的輸出引腳。

圖19.使用脈沖電壓電源的采樣上升沿輸入刺激

通過以地為基準50 Ω負載獲取下降波形

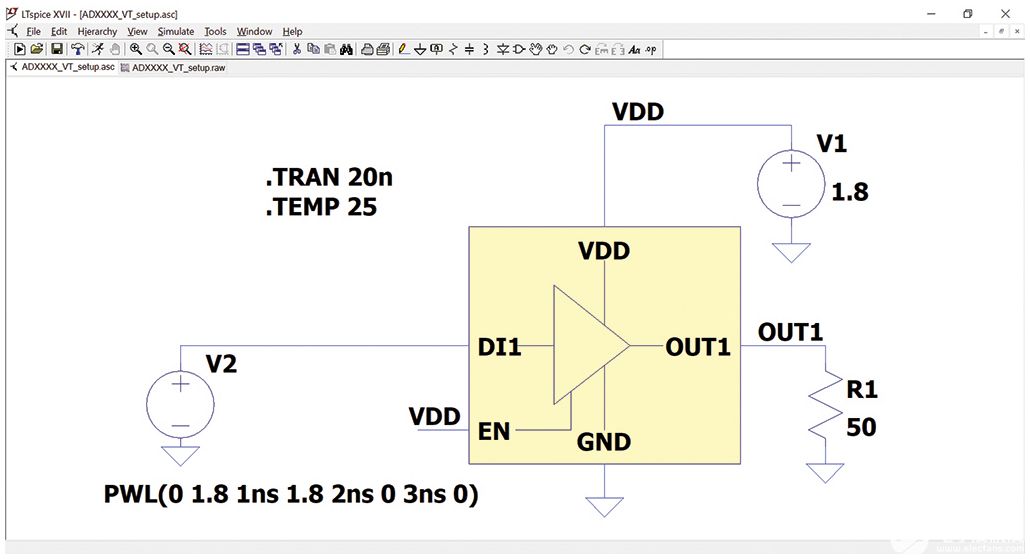

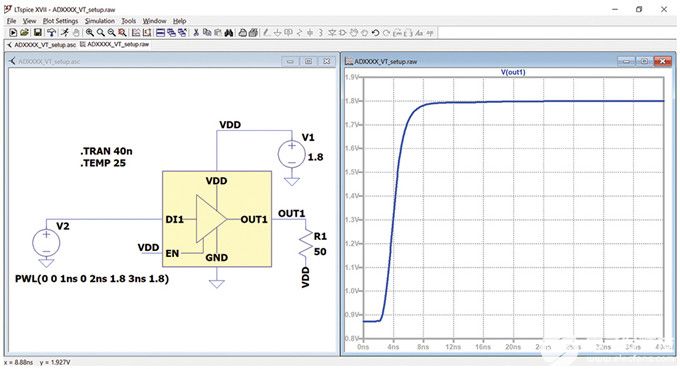

為了產生一個以地為基準的下降輸出波形,需要一個下降沿輸入,并且50 Ω負載需要以GND為基準,如圖20所示。得到的V-T波形如圖21所示,其中輸出穩定在16 ns到20 ns左右。需要注意的是,瞬態分析時間應足以捕捉下降波形(在穩定時)。

圖20.通過以地為基準的50 Ω負載獲取下降波形的ADxxxx設置

圖21.通過以地為基準的50 Ω負載獲取下降波形的ADxxxx結果

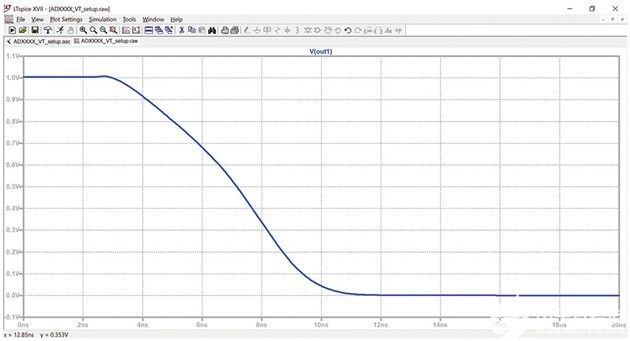

通過以VDD為基準50 Ω負載獲取下降波形

圖22顯示通過以VDD為基準50 Ω負載獲取下降波形的設置和結果。如圖所示,要完全捕獲輸出的下降躍遷,需要50 ns瞬態時間。

圖22.采用以VDD為基準50 Ω負載的ADxxxx設置和DOUT1下降波形圖

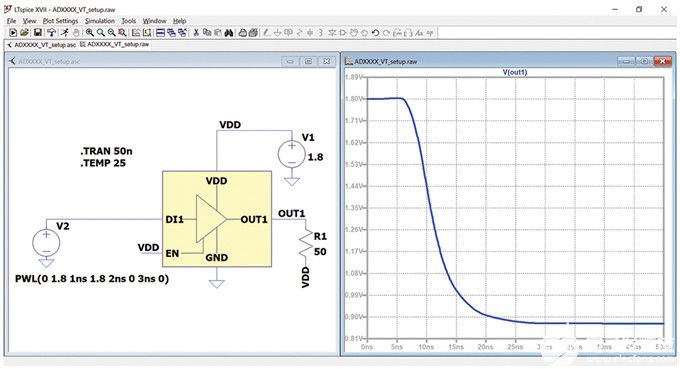

通過以地為基準50 Ω負載獲取上升波形

對于上升波形,采用PWL信號形式的上升沿輸入刺激。圖23中的設置顯示,負載電阻連接至相對于地的輸出引腳,這將產生上升負載對地的V-T數據。

圖23.采用以地為基準50 Ω負載的ADxxxx設置和DOUT1上升波形圖

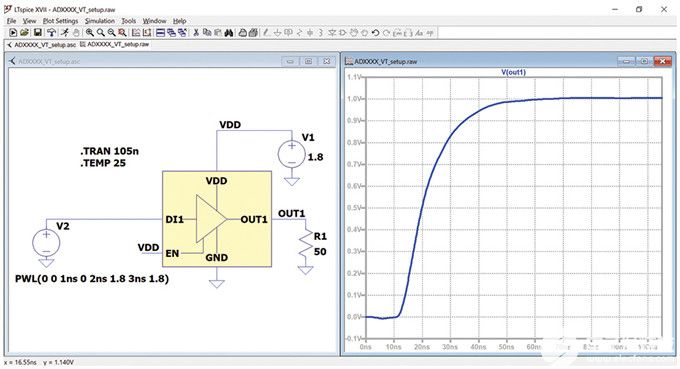

負載連接至VDD時的上升波形

使用相同的上升沿輸入刺激,但50 Ω需要以VDD為基準。

檢查V-T數據正確性的一種方法是查看邏輯低電壓和邏輯高電壓。在VDD為基準波形應具有相同的邏輯低電壓和邏輯高電壓電平,并且邏輯高電壓應與VDD相同。另一方面,以GND為基準波形也應具有相同的邏輯低電壓和邏輯高電壓,并且邏輯低電壓電平應為約0 V。

圖24.采用以VDD為基準50 Ω負載的ADxxxx設置和DOUT1上升波形圖

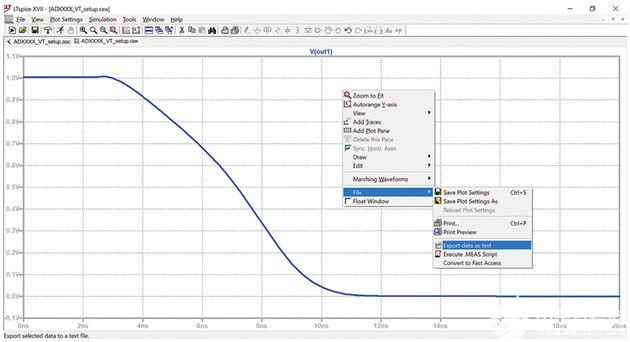

導出波形

然后,必須執行以下步驟,以保存從四個設置中提取的V-T波形:

● 右鍵單擊圖。

● 將鼠標懸停在文件上,然后單擊將數據導出為文本。

圖25.將LTspice圖保存為文本文件

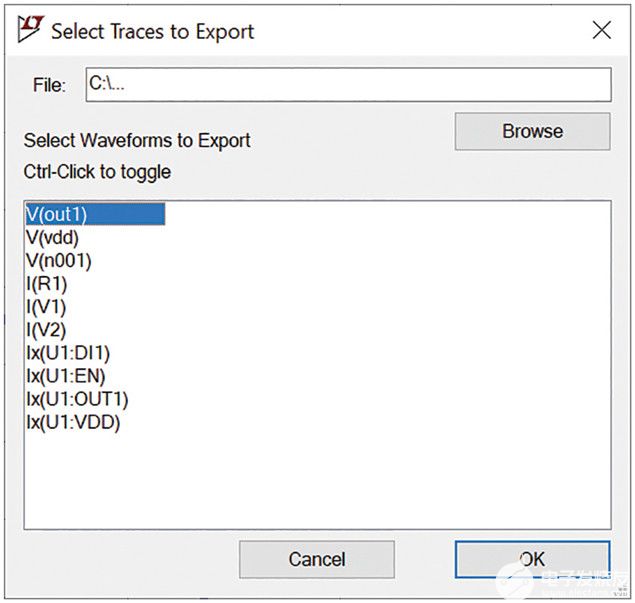

● 選擇要導出的波形和導出波形的目錄。

圖26.選擇走線,設置保存目錄

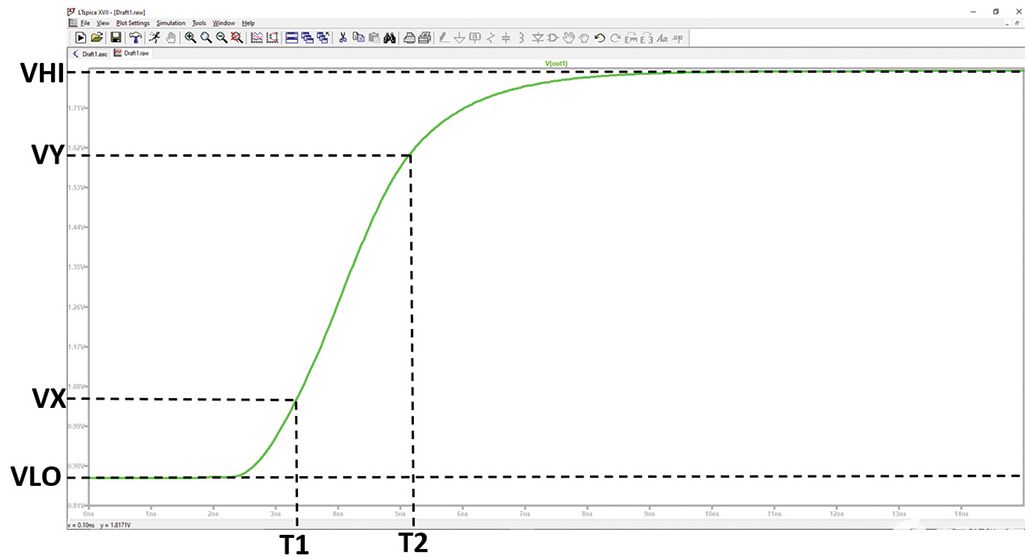

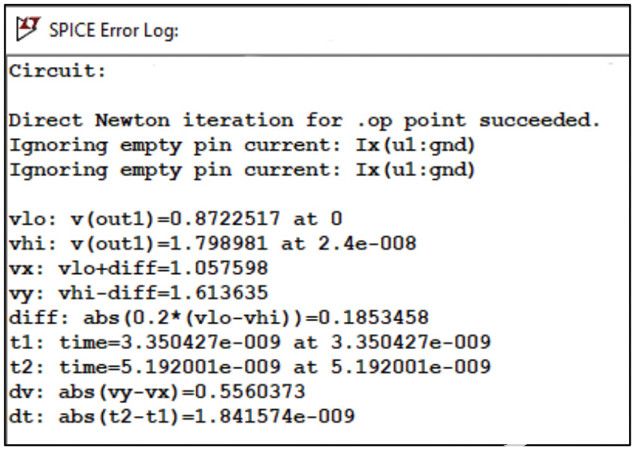

使用LTspice提取斜坡數據

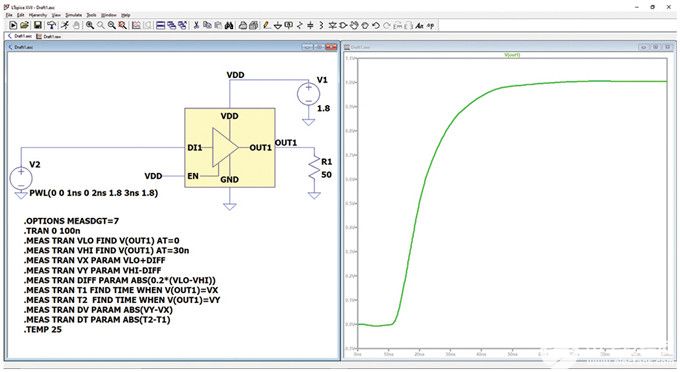

[斜坡]關鍵字是斜坡率(dV/dt),表示在上升或下降轉換沿的20%到80%位置捕捉的上升和下降VT數據。此方法可以在LTspice上實現,因為它能夠使用.MEAS和.PARAM指令計算這些參數。可以通過在VT波形設置上添加SPICE指令來完成斜坡提取過程。這意味著斜坡和VT波形可以同時提取。

圖27.ADxxxx VT設置,以及用于提取上升波形的斜坡的附加指令

圖27顯示上升波形斜坡計算的設置。為了計算下降波形的斜坡,應該互換VLO和VHI的時間值,因為下降斜坡的輸出波形從緩沖器的邏輯高電平開始,并轉變為邏輯低電平。

用于斜坡提取的LTspice指令

用于斜坡提取的SPICE指令如下:.TRAN,這是用于VT上升/下降波形的SPICE指令;.OPTIONS,用于將SPICE錯誤日志上顯示的輸出設置為笛卡爾模式,并將其限制為所需的有效位數;.MEAS,用于斜坡的實際計算。

● VLO:表示邏輯低電壓。

● VHI:表示邏輯高電壓。

● Diff:表示轉換的20%點位置的電壓,該電壓將分別與VLO和VHI參數相加和相減,以得到轉換的20%和80%點位置。

● VX和VY:表示上升/下降轉換沿的20%和80%點位置的電壓。

● dV和dT:這些是IBIS模型的[斜坡]關鍵字的計算值。

圖28.上升斜坡波形描述

圖29.SPICE錯誤日志,用于計算斜坡率

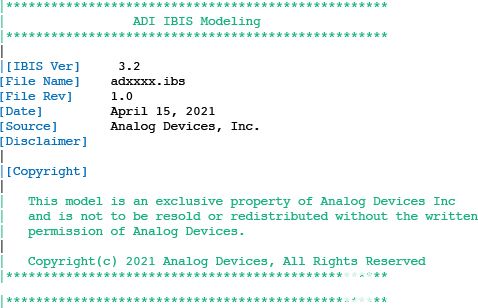

構建IBIS模型

所有提取的I-V和V-T數據都將編譯到BIS模型(.ibs)文件中。以下是IBIS文件的實際模板,用戶可以在構建IBIS模型時用作參考。

.ibs文件以[IBIS Ver]關鍵字開頭,后接文件名和修訂號。IBIS版本3.2將在[IBIS Ver]關鍵字中使用,因為它是構建3態輸出緩沖器所需的最低版本。.ibs文件的文件名應和[文件名稱]關鍵字中的文件名相同;否則,解析器會將其檢測為錯誤。此外,文件名不得包含任何大寫字母,因為解析器只允許文件名使用小寫字母。有關其他重要的關鍵字,將在后面章節中討論。

.ibs文件的下一部分包括[組件]、[制造商]、[封裝]和[引腳]關鍵字。ADxxxx有兩個輸入緩沖器(DIN1和EN)和一個輸出緩沖器(DOUT1),因此它的IBIS模型總共有三個緩沖器模型。[封裝]關鍵字通過RLC封裝寄生值作為器件的封裝模型。所有器件緩沖器的模型名稱在[引腳]關鍵字下定義,這與在[模型]關鍵字下定義命名變量類似。

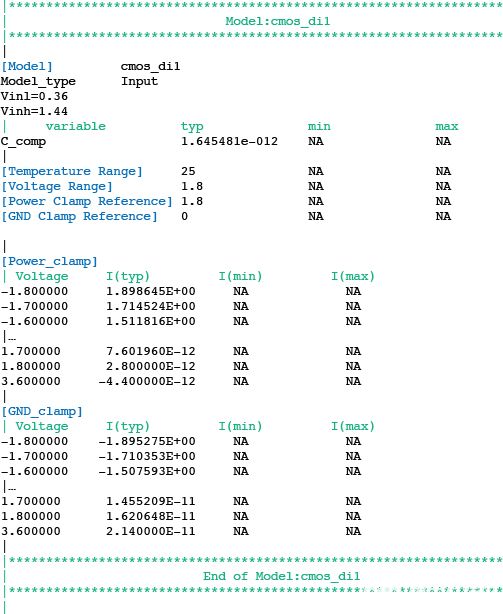

在.ibs文件的下一部分,使用測量得出的I-V和V-T數據構建器件的數字緩沖器的模型。緩沖器模型的內容因Model_type變量中指定的緩沖區類型而異。由于模型cmos_di1是一個輸入緩沖器,它的緩沖器模型只包含C_comp、[Power_Clamp]和[GND_Clamp]數據。輸入緩沖器模型還包括VINH和VINL值,這兩個值都可以在器件的數據手冊中找到。由于DIN1和EN都是輸入緩沖器,所以它們的緩沖器模型具有相同的結構。

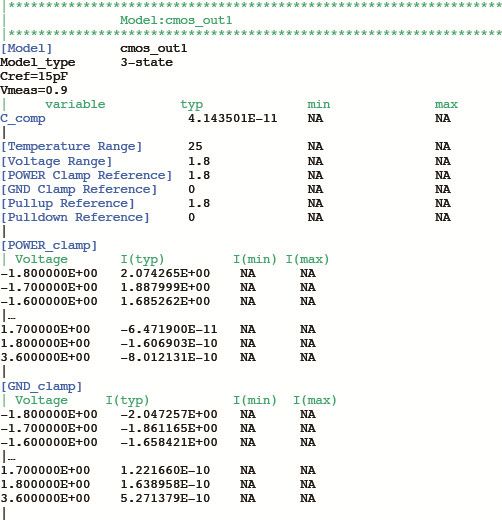

另一方面,3態緩沖器模型包含一些與輸入緩沖器模型類似的關鍵字,但包含額外的I-V和V-T數據。cmos_out1的緩沖器模型包括一個額外的子參數Cref,它代表輸出電容負載,還包括Vmeas,它代表基準電壓電平。通常情況下,使用的Vmeas是VDD值的一半。

除了C_comp、[Power_Clamp]和[GND_Clamp],3態緩沖器還包含額外的I-V數據:[上拉]和[下拉]。

最后,所有IBIS模型都應該用[結尾]關鍵字作為結尾。

IBIS模型驗證

正如本系列文章的第1部分所述,IBIS模型驗證由解析器測試和相關過程組成。這些是確保IBIS文件符合IBIS規范的必要步驟,并且模型的執行盡可能接近參考SPICE模型。

解析器測試

對于上一節中創建的IBIS文件,首先應進行解析器測試,然后再繼續執行相關過程。ibischk是用于檢查IBIS文件的Golden Parser。它用于檢查IBIS文件是否符合IBIS協會設置的規范。有關更多信息,請訪問ibis.org。在撰寫本文時,使用的最新解析器是ibischk版本7。

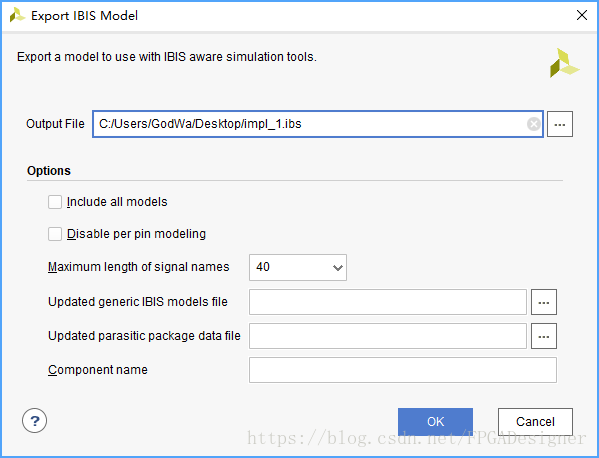

在執行解析器測試時,最好使用集成了ibischk的IBIS模型編輯軟件,例如Cadence Model Integrity和Hyperlynx Visual IBIS Editor。這些工具有助于簡化語法檢查。但是,如果用戶沒有這些工具,可以訪問ibis.org免費下載可執行代碼。它是在各種操作系統上編譯的,所以用戶不必擔心應使用哪種操作系統。

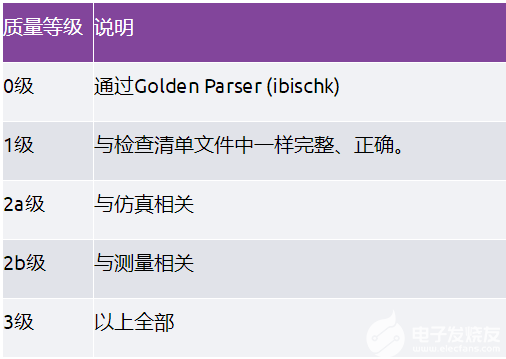

相關程序

在這個驗證階段,需要檢查IBIS模型的性能是否與參考模型(在本例中為SPICE模型)相同。表7顯示不同的IBIS質量級別(從0級到3級)。它描述了經受不同程度測試后,IBIS模型的精確程度。在本例中,由于參考模型是ADxxxx SPICE模型,所以生成的IBIS模型的質量等級為2a。這意味著它通過了解析器測試,具有數據手冊中所描述的一組正確完整的參數,并通過了相關程序。

表7.IBIS質量等級

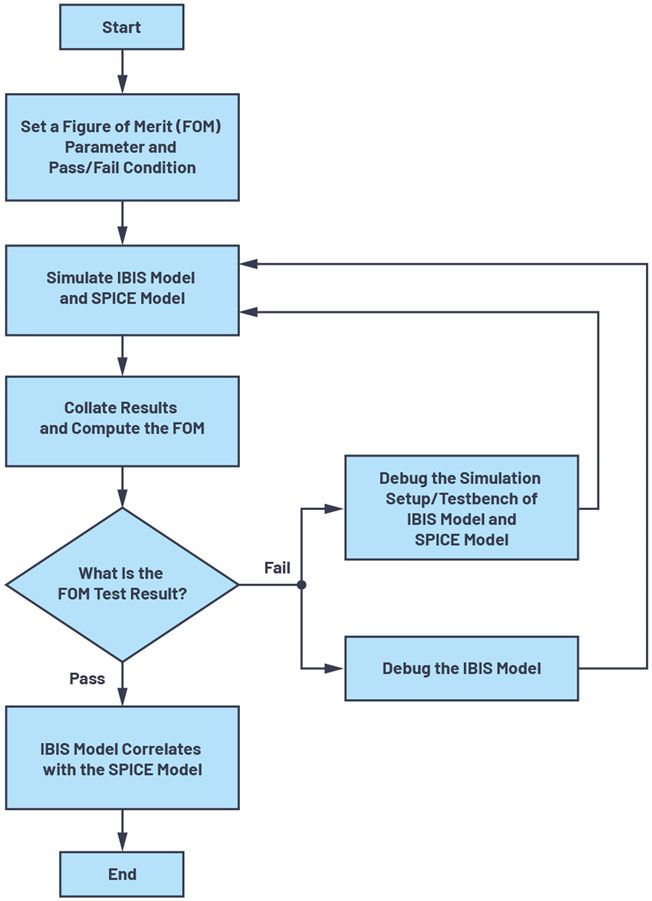

要將IBIS模型與參考SPICE模型關聯起來,可以按照一些常規步驟執行操作。圖30中的流程圖總結了這些步驟。

圖30.IBIS與SPICE模型的關聯流程圖

設置品質因數

關聯的基礎是在相同的加載條件和輸入刺激下,IBIS模型的行為應該與SPICE模型數字接口相同。這意味著從理論上,它們的輸出應該重疊在一起。一般來說,有兩種方法可以描述IBIS模型的輸出與SPICE參考模型的接近程度:定性方法和定量方法。用戶可以使用這兩種方法來確定IBIS模型與SPICE模型之間的關系。

定性FOM測試需要依靠用戶的觀察能力。它要求對兩個輸出進行目視檢查,以確定是否通過相關性檢查。這可以通過疊加IBIS和SPICE的輸出結果來實現,并使用工程判斷來確定圖形是否相關。在進行定量FOM測試之前,這可以作為相關性初步檢查。當接口以相對較低的頻率或比特率運行時,此測試就已足夠。

IBIS IO緩沖器精度手冊中提出了另一種定性FOM測試,即曲線包絡度。它使用過程電壓溫度極值定義的最小和最大曲線。最小和最大曲線作為相關性的邊界。要通過測試,IBIS結果中的所有點都應該在最小和最大曲線之內。這種方法在本文中不適用,因為它僅適用于典型條件。

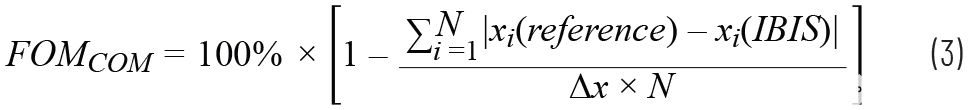

定量FOM測試使用數學運算來衡量IBIS與SPICE之間的相關性。在IBIS IO緩沖器精度手冊中也提出了曲線包絡度,它使用IBIS和SPICE輸出的數據點。它計算IBIS和參考數據點之間x軸或y軸差值的絕對值除以軸上使用的總范圍和點數的乘積的總和。具體如公式3所示,此方法適合作為檢測本文所示的應用案例的關聯方法。但是,還需要考慮其他因素。方程3中給出的FOM要求將IBIS和SPICE的結果映射到一個通用的x-y網格上,這將用到數值算法和插值方法。如果用戶想要執行快速定量FOM測試,本文提出了另一種方法,即使用曲線和x軸所限定的面積的曲線面積度量。

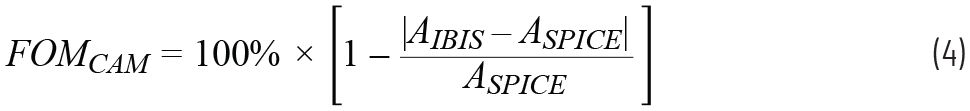

曲線面積度量以SPICE結果為參考,比較IBIS曲線下的計算面積。具體如公式4所示。但是,在進行曲線面積度量測試之前,所創建的模型必須通過定性測試。這確保了IBIS和SPICE曲線是同步的,并且相互疊加。在獲取曲線下的面積時,因為對IBIS和SPICE結果使用了相同的方法,所以用戶可以使用數值方法,例如梯形規則或中點規則。在使用這種方法時,建議使用盡可能多的點,以更接近該面積。

驗證ADxxxx IBIS模型

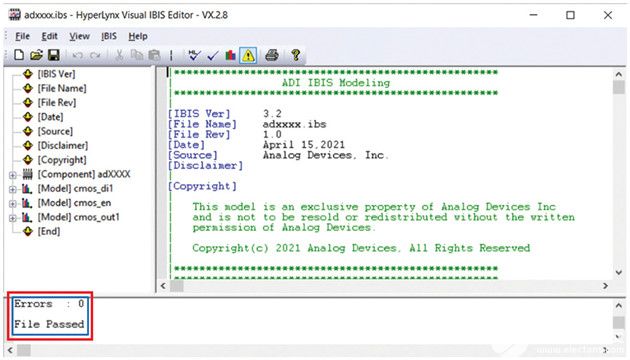

IBIS模型驗證的第一步是解析器測試。圖31顯示adxxxx.ibs IBIS模型文件的解析器測試結果,該文件是使用HyperLynx Visual IBIS Editor編寫的。用戶執行解析器測試時,目標是不會出現任何錯誤。如果出現任何錯誤或警告提示,模型構建人員需要加以解決。這樣可以保證IBIS模型在仿真工具之間的兼容性。

圖31.ADxxxx 解析器測試結果

下一步是設置FOM參數。本文僅使用定性FOM和曲線面積度量作為衡量相關性的方法。該測試可能會使用IBIS和SPICE在相同負載條件和輸入刺激下的瞬態響應曲線。曲線面積度量FOM≥95%才能通過相關性測試。DOUT1、DIN1和EN的相關性如下所示。

DOUT1

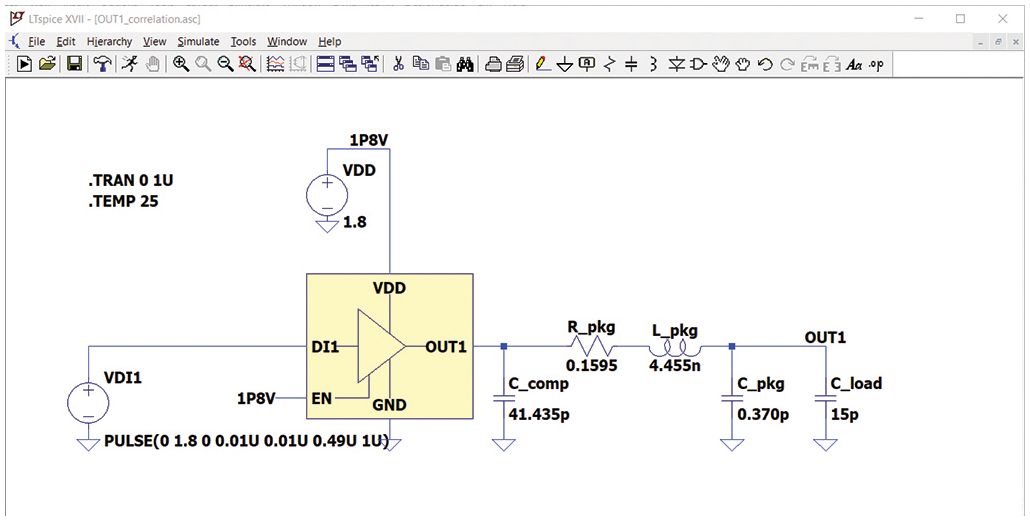

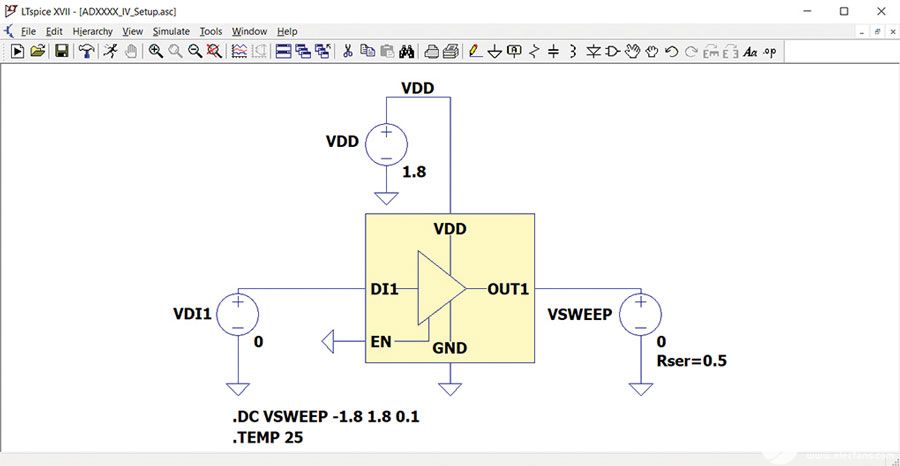

圖32顯示了LTspice上用于檢測DOUT1相關性的SPICE測試臺。在原理圖上提供適當的電壓電源以使能驅動器,并且為DIN1引腳提供脈沖信號源來驅動DOUT1。要在LTspice中完成DOUT1驅動器模型,還需要使用額外的組件。C_comp代表芯片電容。將C_comp和C_load添加到LTspice模型后,繼續加入RLC封裝寄生(R_pkg、L_pkg、C_pkg)和C_load。

圖32.LTspice DOUT1相關性測試臺

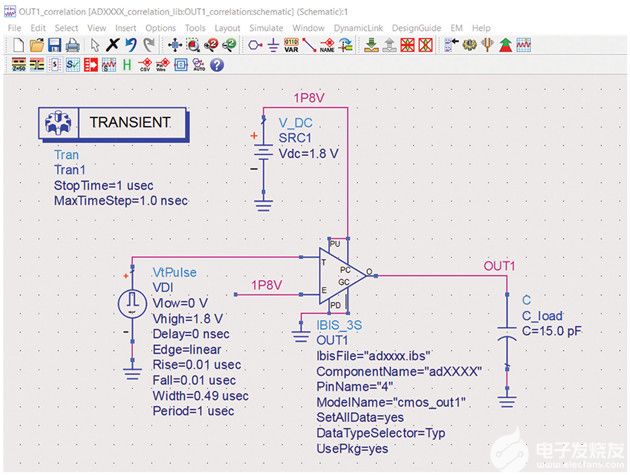

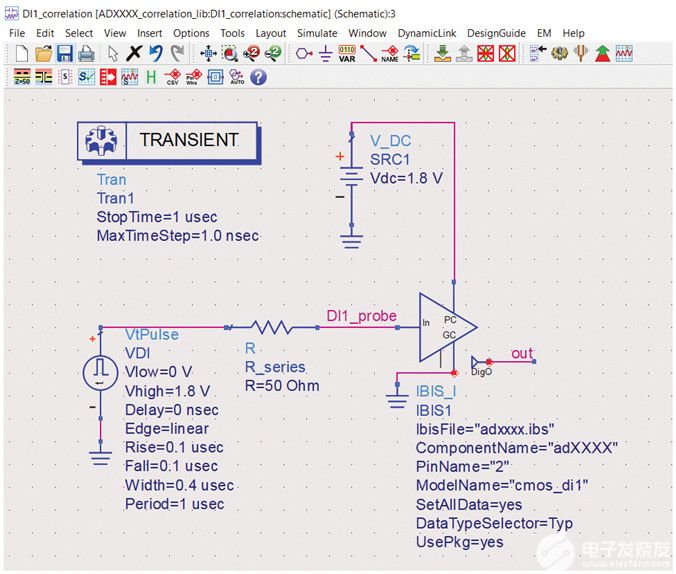

DOUT1 IBIS模型相關性測試臺建立在Keysight先進設計系統(ADS)上,如圖33所示。與LTspice測試臺一樣,使用相同的輸入激勵、C_load、電壓電源和瞬態分析。但是,未在原理圖中顯示C_comp和RLC封裝寄生,因為它們已經包含在3態IBIS模塊中。

圖33.ADS OUT1相關性測試臺

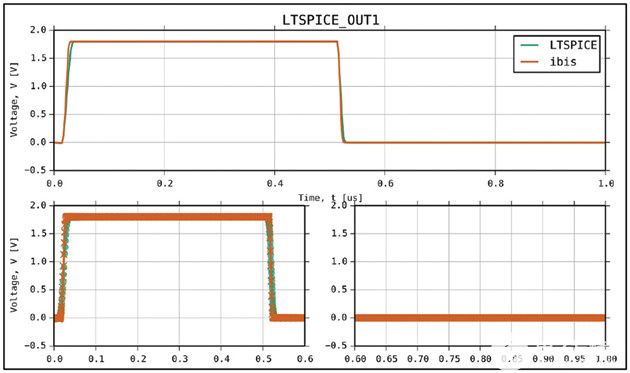

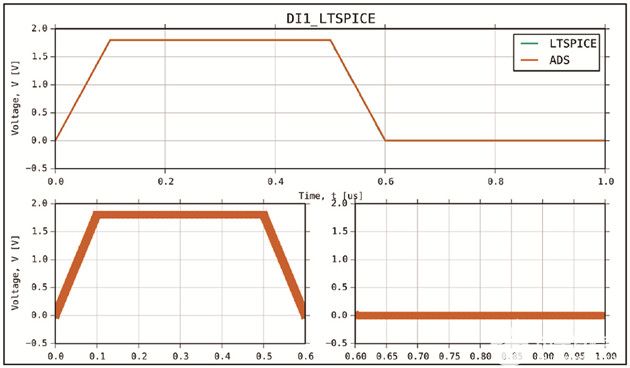

瞬態響應曲線根據C_load測量得出。我們比較LTspice和ADS結果,并將它們疊加在一起實施定性FOM分析。如圖34所示,LTspice和ADS DOUT1的響應非常相似。可以使用曲線和度量來量化它們之間的差異。計算1 μs瞬態時間內曲線下的面積。計算得出的曲線面積度量為99.79%,滿足設置的≥95%的通過測試條件。所以,DOUT1 IBIS模型與SPICE模型相關。

圖34.LTspice與IBIS模型OUT1響應

DIN1和EN

在驗證輸入端口時,通過定性FOM和曲線面積度量來關聯LTspice和ADS的瞬態響應曲線。LTspice中的測試臺如圖35所示。這適用于DIN1和EN引腳。與DOUT1一樣,將提取的C_comp置于DIN1端口位置,后接RLC封裝寄生效應。然后,連接50 Ω R_series電阻,該電阻后接輸入刺激脈沖電壓電源。測量響應的探頭點在DIN1_probe位置。

圖35.LTspice DI1相關性測試臺

用于驗證輸入端口的Keysight ADS測試臺如圖36所示。同樣,在輸入端口前放置一個R_series 50 Ω電阻,并使用相同的輸入脈沖刺激。此處未顯示C_comp和RLC寄生效應,因為它們已經包含在IBIS模塊中。用于測量瞬態響應的探頭位于DI1_probe位置。

圖36.ADS DI1相關性測試臺

將LTspice和ADS的瞬態響應曲線疊加在一起進行FOM定性測試。如圖37所示,曲線是相同的,LTspice曲線完全與ADS曲線重疊。計算得出的DI1的曲線面積度量為100%,滿足所設置的≥95%的通過測試條件。EN引腳相關性結果也給出了相同的圖形和曲線面積度量。

圖37.LTspice與IBIS模型的DI1響應

總結

本文介紹如何使用LTspice來提取數據和構建IBIS模型。還提出通過定性FOM和曲線面積度量的定量FOM將IBIS模型與參考SPICE模型關聯起來的方法。這樣就可以讓用戶確信IBIS模型的行為與SPICE模型類似。盡管還有本文未介紹其他類型的數字IO,但提取C_comp、I-V數據和V-T數據的程序可以作為創建其他類型IO模型的基礎。

您可以免費下載和安裝LTspice,并開始創建自己的IBIS模型。

審核編輯:湯梓紅

-

ADI

+關注

關注

148文章

46022瀏覽量

258556 -

IBIS

+關注

關注

1文章

55瀏覽量

20154 -

模型

+關注

關注

1文章

3483瀏覽量

49987

發布評論請先 登錄

請問如何獲得AD8000的IBIS模型?

IBIS 模型

請問有人知道IBIS模型怎么使用嗎?

高速互連IBIS仿真模型概述

生成IBIS模型錯誤

哪里可以找到IBIS模型?

為什么以及如何創建自己的IBIS模型

如何以及為何要在EtherCAT?應用中使用DP83826

評論