在 NAND 工藝開發(fā)中,2D NAND 在 10 nm 左右已達(dá)到極限。由于平面 NAND 技術(shù)的浮柵內(nèi)部的電子較少,因此 3D NAND 結(jié)構(gòu)正在成為大容量存儲(chǔ)系統(tǒng)的主流。

3D NAND 結(jié)構(gòu)將平面浮動(dòng)?xùn)艠O旋轉(zhuǎn) 90 度,并在彼此頂部堆疊許多層以增加容量。3D NAND 市場(chǎng)的大多數(shù)廠商——包括三星、東芝/WD、美光、海力士和英特爾——現(xiàn)在都在批量生產(chǎn) 256 Gb 芯片容量的 64 層三層單元 (TLC) NAND。96 層、512 Gb 選項(xiàng)應(yīng)該會(huì)在今年某個(gè)時(shí)候推出。

使用 ECC 克服 3D NAND 的復(fù)雜性

由于 3D 結(jié)構(gòu)的復(fù)雜性,可能會(huì)出現(xiàn)多種錯(cuò)誤。這些包括層間讀取干擾、寫入干擾和數(shù)據(jù)保留問題。尤其是在大容量系統(tǒng)中,所有這些問題至少需要 NAND 閃存控制器,更具體地說,需要高級(jí)糾錯(cuò)算法。

不幸的是,多級(jí)單元 (MLC) NAND 技術(shù)中使用的傳統(tǒng) Bose-Chaudhuri-Hocquenghem (BCH) 糾錯(cuò)碼 (ECC) 算法不足以用于 3D TLC NAND。需要更強(qiáng)大的低密度奇偶校驗(yàn) (LPDC) ECC 算法。

LPDC ECC 使用硬件和軟件機(jī)制來糾正位錯(cuò)誤。硬件機(jī)制每 1 KB 可以糾正超過 120 位錯(cuò)誤,而軟件機(jī)制使用更復(fù)雜的錯(cuò)誤糾正方法來解決幾乎兩倍的錯(cuò)誤。但是雖然它們更強(qiáng)大,但基于軟件的 ECC 操作需要更長的時(shí)間才能執(zhí)行。

除了硬件和軟件校正機(jī)制之外,3D NAND 還需要一種防止大量數(shù)據(jù)丟失的方法。這意味著必須在 NAND 控制器內(nèi)部實(shí)施 RAID 功能,以解決無法通過 LPDC ECC 算法糾正的錯(cuò)誤,例如整頁錯(cuò)誤或多個(gè)數(shù)據(jù)頁的損壞。這個(gè) RAID 功能當(dāng)然需要一些額外的內(nèi)存來進(jìn)行奇偶校驗(yàn)和額外的計(jì)算資源,但確保 SSD 上的數(shù)據(jù)安全是非常值得的。

3D TLC NAND 設(shè)備的安全數(shù)據(jù)序列

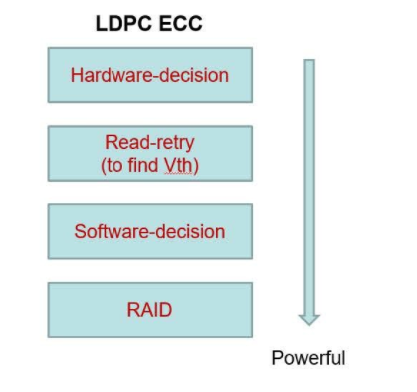

圖 1 顯示了 SSD 控制器的 LDPC ECC 序列,包括上述 RAID 功能。在步驟中,SSD控制器必須實(shí)現(xiàn)的ECC序列如下:

首先使用硬件機(jī)制(hardware-decision)

如果步驟 1 失敗,請(qǐng)嘗試實(shí)施不同的 Vth(NAND 狀態(tài)的電壓電平)以獲得最低的誤碼率,也稱為讀取移位或讀取重試

接下來,實(shí)現(xiàn)軟件機(jī)制(software-decision)來糾正錯(cuò)誤

如果一切都失敗了,請(qǐng)使用內(nèi)部 RAID 功能

圖 1. 在 3D TLC NAND 控制器上實(shí)施此 ECC 方案提供了一種糾正位錯(cuò)誤的過程,該過程從資源密集度最低變?yōu)樽顝?qiáng)大。

更可靠的 3D TLC NAND

3D TLC NAND 代表了存儲(chǔ)介質(zhì)的轉(zhuǎn)折點(diǎn),提供了更低的每比特成本和更小的占用空間。然而,為了使市場(chǎng)擴(kuò)展到嵌入式行業(yè),該技術(shù)需要提供一套可持續(xù)的、可擴(kuò)展的比特糾錯(cuò)解決方案。

通過實(shí)施上述 LPDC ECC 序列,在 NAND 控制器上終止強(qiáng)大的 RAID 功能,UDInfo相信,未來基于 3D TLC NAND 的設(shè)備可以保證 SSD 質(zhì)量和數(shù)據(jù)完整性。

審核編輯:郭婷

-

控制器

+關(guān)注

關(guān)注

112文章

16332瀏覽量

177813 -

NAND

+關(guān)注

關(guān)注

16文章

1681瀏覽量

136121 -

SSD

+關(guān)注

關(guān)注

21文章

2857瀏覽量

117371

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

預(yù)期提前,鎧俠再次加速,3D NAND準(zhǔn)備沖擊1000層

【半導(dǎo)體存儲(chǔ)】關(guān)于NAND Flash的一些小知識(shí)

一文理解2.5D和3D封裝技術(shù)

物聯(lián)網(wǎng)行業(yè)中的模具定制方案_3D打印材料選型分享

美光第九代3D TLC NAND閃存技術(shù)的SSD產(chǎn)品開始出貨

奧比中光3D相機(jī)打造高質(zhì)量、低成本的3D動(dòng)作捕捉與3D動(dòng)畫內(nèi)容生成方案

3D建模的重要內(nèi)容和應(yīng)用

3D NAND閃存來到290層,400層+不遠(yuǎn)了

請(qǐng)問3D NAND如何進(jìn)行臺(tái)階刻蝕呢?

包含具有多種類型信息的3D模型

有了2D NAND,為什么要升級(jí)到3D呢?

三星將推出GDDR7產(chǎn)品及280層堆疊的3D QLC NAND技術(shù)

Exaddon開發(fā)了一種低于20μm間距進(jìn)行細(xì)間距探測(cè)的3D微打印探針

介紹一種使用2D材料進(jìn)行3D集成的新方法

兩種應(yīng)用于3D對(duì)象檢測(cè)的點(diǎn)云深度學(xué)習(xí)方法

一種用于3D TLC NAND的彈性糾錯(cuò)方案

一種用于3D TLC NAND的彈性糾錯(cuò)方案

評(píng)論