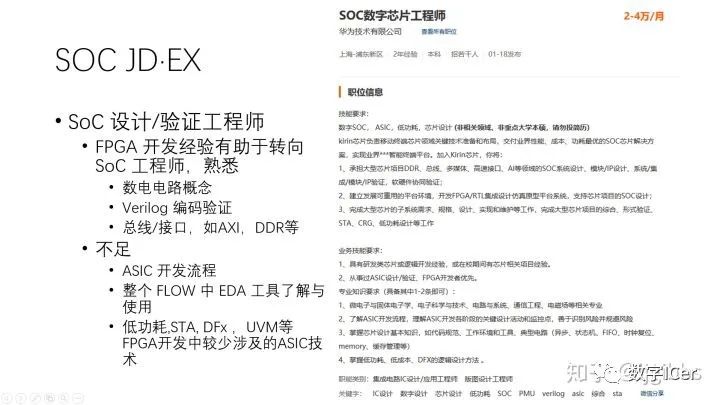

上圖:

FPGA 開發經驗也有助于求職 SoC 設計/驗證相關的工作,而不是僅限于 FPGA 相關的工作。

個人觀點:SoC /數字芯片類崗位需要兩類技能:

1)概念與方法論

2)工具使用。這里以 FPGAer 轉向 ICer 的思路分析。括號中的數字代表筆者認為的 FPGAer 普遍掌握的程度。

1)概念與方法論,包括:

數據芯片相關基礎知識,比如數電,Verilog 編碼,代碼與電路的映射,典型模塊與電路,模塊級設計思想,測試平臺搭建與邏輯功能驗證。這部分可以說和 FPGA 開發經驗是完全共通的(80%)

數字芯片進階知識,比如低功耗設計,可測試性設計,跨時鐘域、電壓域設計,靜態時序分析,形式驗證,UVM 驗證,綜合等,這部分在 FPGA 開發中是不涉及的,或因為工具代勞或者 FPGA 開發中不重要而被忽視的。(30%)

數字芯片周邊知識,比如內部與外部的總線原理或使用經歷(DDR,serdes,PCIE,以太網,多媒體接口等),應用領域的相關知識(如圖像處理,網絡通信等)。由于 FPGAer 從事開發的領域大多是在通信或者圖像處理,因此這部分有比較高的掌握程度。(60%)

團隊合作,如果說 FPGA 開發單打獨斗是有可能的,那么芯片的開發一定是團隊合作的。FPGAer 在芯片崗位可能要適應更大,專業領域跨越更廣的團隊以及密切的團隊合作需求。(50%)

2)工具,包括:

EDA,IC 開發會使用許多 EDA 工具,這些工具顯然是 FPGAer 沒接觸過的。但是工具的使用有一些共性,比如 Vivado 的約束語言 XDC 的語法來自 IC 業界通用的 SDC,據說 Vivado 的時序分析工具據說來自于 IC 業界常用的時序約束工具 PT 。盡管如此,工具還是需要去學習以及掌握(10%)

腳本語言,IC 過程中為了更高效地使用 EDA 工具,會使用和編寫很多腳本。盡管當前 FPGA 工具對于基于 TCL 命令行的開發流程也有不錯的支持,但大多數人包括筆者自己目前用的更多的還是 GUI 界面。腳本語言包括閱讀已有代碼和編寫新代碼兩部分,目前“祖傳腳本”大都是 Perl 編寫的,而 EDA 工具對 TCL 有很好的支持,此為 shell 腳本也較為常用,Python 則是后起之秀。建議 FPGAer 結合自己的基礎選擇一門腳本語言進行修仙(10-90%,取決個人情況)

操作系統,也需要操作系統技能?是的,但僅限于掌握 Linux 的使用。由于 FPGA 的 EDA 工具基于 Java 開發,他們都提供體驗一致的 Linux 版本。但筆者相信大家用的比較多的還是 Windows 版本,甚至有的朋友對 Linux 接觸很少。IC 設計公司的合作工作模式,使所有 IC 公司都會使用支持多用戶的 Linux 作為工作平臺,而不是單用戶的 Windows。所以有必要掌握 Linux 系統的基本使用(但不用你掌握如何安裝與卸載軟件,這一 Linux 上的困難工作^_^)。以及 Vim 等編輯器的使用,是的,因為后臺系統是不能聯網的,所以你不能安裝你自己喜歡的編輯器,比如 VSCode ...(10-90%,取決個人情況)

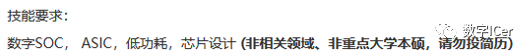

插曲:這里用的是知乎熱門公司的招聘啟事,放大看下有一條描述:

唔,我只能說半導體行業對于學歷和專業是有一些要求,但此時(2020)招聘市場相對比較緊俏,非科班或者名校出身的同學,如果有相關的項目經歷或者有很好的自學基礎,還是可以參與到這個在國內相對來說“火熱”的行業的。

審核編輯 :李倩

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603984 -

IC

+關注

關注

36文章

5957瀏覽量

175738 -

數字芯片

+關注

關注

1文章

110瀏覽量

18416

原文標題:FPGAer 轉戰 IC 需要學習哪些技能?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

soc芯片與傳統芯片的主要區別在哪

如何選擇合適的SOC芯片

SOC芯片與傳統芯片的區別

【「數字IC設計入門」閱讀體驗】+ 概觀

soc芯片和mcu芯片區別在哪

一文帶你了解半導體公司的各個崗位

SoC /數字芯片類崗位需要學習哪些技能?

SoC /數字芯片類崗位需要學習哪些技能?

評論