上一篇講到了Idelay,那么SERDES(Serialization/De-serialization)也可以順帶介紹一下。高速信號(hào)傳輸過程中,并行傳輸因?yàn)榫€路同步難,抗干擾性差等缺點(diǎn)逐漸被串行技術(shù)取代;通過提高傳輸速率的方法,串行傳輸也可以實(shí)現(xiàn)很高的傳輸速度。

但是,在內(nèi)部處理信號(hào)時(shí),數(shù)據(jù)信號(hào)往往是多bit信號(hào),而傳輸過程中需要用到單bit串行傳輸技術(shù),所以,中間需要有一個(gè)轉(zhuǎn)換器,實(shí)現(xiàn)并串轉(zhuǎn)換,這就需要用到SERDES技術(shù)。

從Virtes-4系列FPGA開始,Xilinx公司的FPGA支持LVDS電平和內(nèi)置的SERDES原語(yǔ),所以本文適用Virtes-4及后續(xù)系列FPGA。

本文將介紹ISERDES的IP核生成,ISERDES原語(yǔ)介紹,Bitslip使用以及最終的仿真結(jié)果。

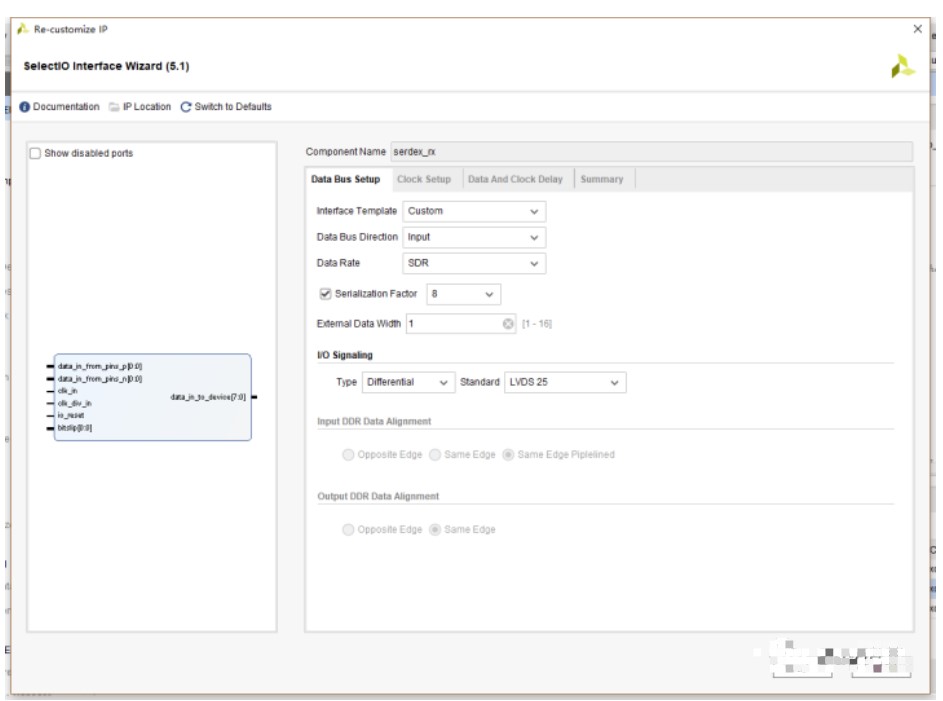

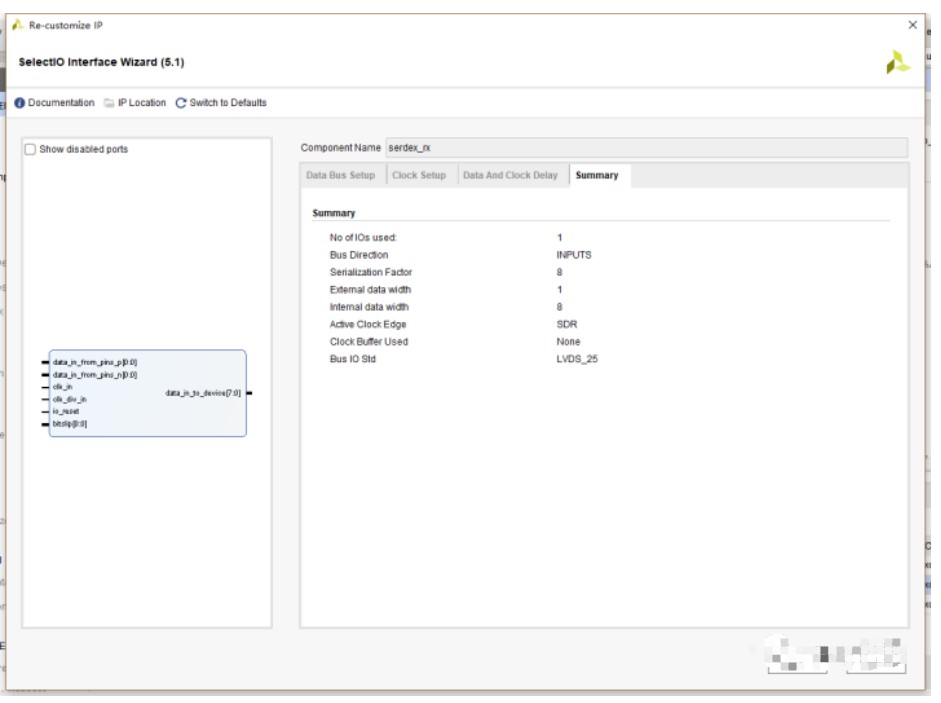

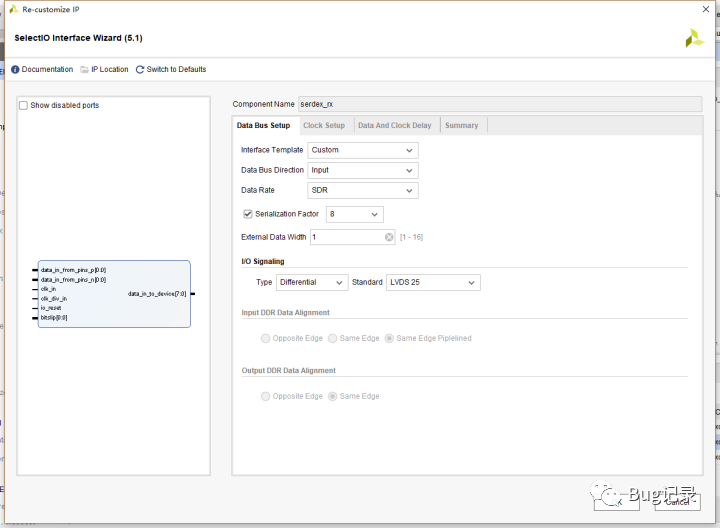

這次我們可以使用IP核簡(jiǎn)化ISERDES原語(yǔ)的配置,找到SelectIO IP核的配置,然后使用簡(jiǎn)化設(shè)置,如下:

數(shù)據(jù)總線設(shè)置

簡(jiǎn)單來說,

Interface Template:接口模板,本次數(shù)據(jù)傳輸并不符合預(yù)設(shè)的協(xié)議,所以選擇Custom

Data BUS Direction:接收數(shù)據(jù)-> input

Data Rate: 數(shù)據(jù)總線是SDR還是DDR,DDR內(nèi)容可以看(LVDS差分信號(hào)簡(jiǎn)單處理)2. DDR信號(hào)的處理

Serialization Factor: 串化因子,也就是需要把串行信號(hào)轉(zhuǎn)換成多少bit的并行數(shù)據(jù);

SDR Rate:可設(shè)為2,3,4,5,6,7,8; DDR Rate:可設(shè)為4,6,8,10,14;

External Data Width: 外部輸入數(shù)據(jù)的位寬,默認(rèn)設(shè)1

I/O signaling:設(shè)置差分還是單端以及IO電壓標(biāo)準(zhǔn)

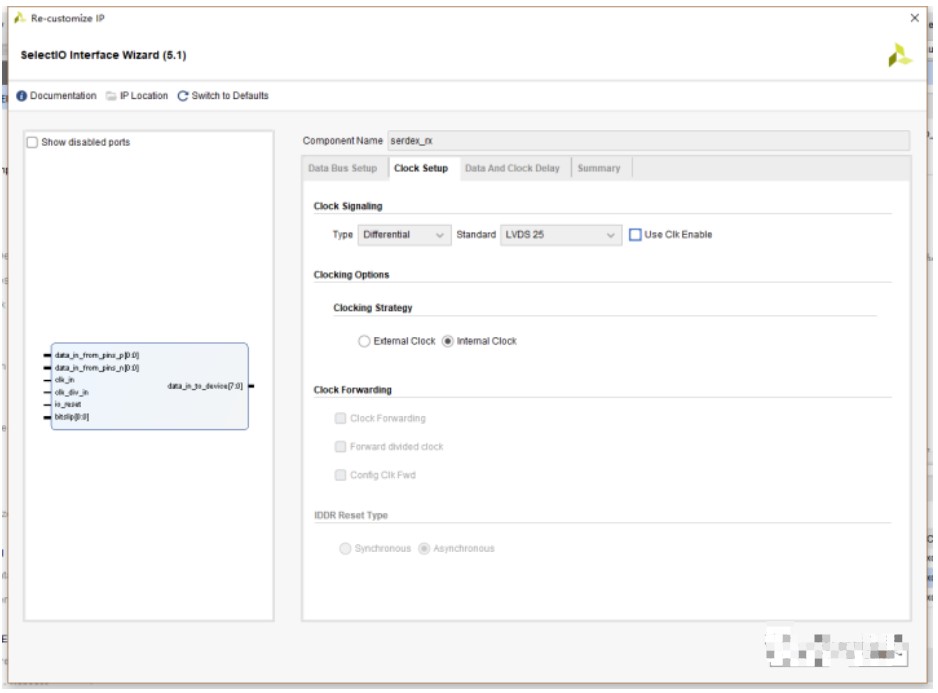

時(shí)鐘設(shè)置

簡(jiǎn)單來說,

Clock Signaling:

時(shí)鐘信號(hào)是差分還是單端以及IO電壓標(biāo)準(zhǔn)

Clock Strategy:

External Clock:

IP核內(nèi)部產(chǎn)生并行時(shí)鐘

Internal Clock:

IP核需要手動(dòng)輸入并行時(shí)鐘

在xilinx的UG471文檔的P152中,提到了ISERDES的時(shí)鐘要求,可以說是要求串行鐘和并行鐘要求相位對(duì)齊,需要注意

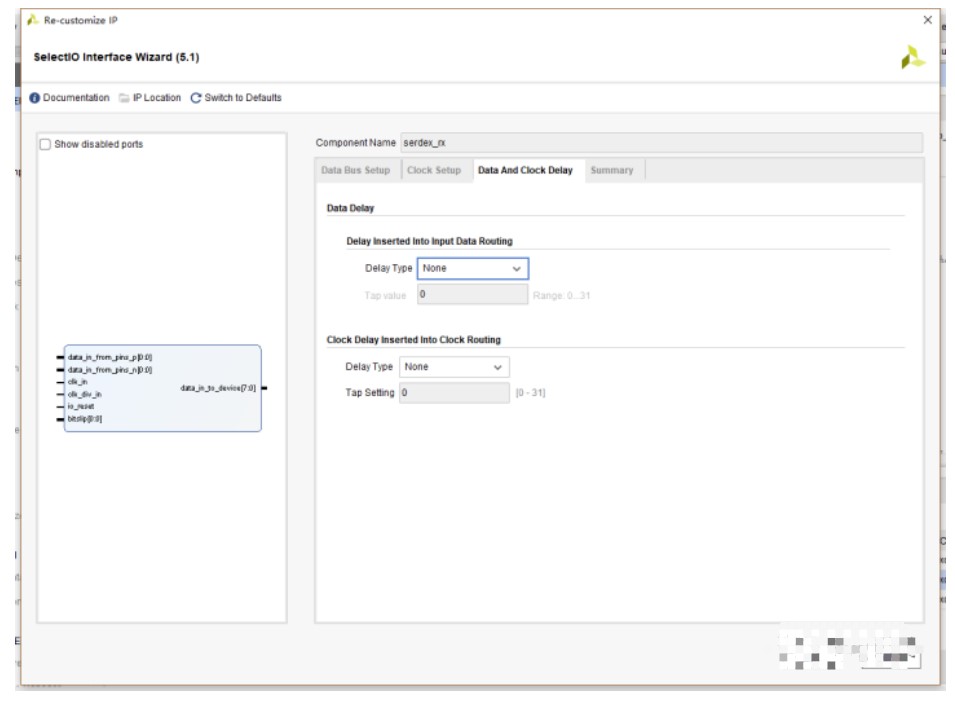

數(shù)據(jù)和延時(shí)設(shè)置

數(shù)據(jù)延時(shí)部分,這個(gè)地方先不做設(shè)置。

Summary

生成IP核之后,可以找到IP核最底層的verilog文件,它的內(nèi)部實(shí)現(xiàn)的核心部分是ISERDES2,為此我們需要知道ISERDES2的參數(shù)內(nèi)容;

ISERDES2的屬性中,重點(diǎn)關(guān)注的是以下幾個(gè):

DATA_RATE: 數(shù)據(jù)速率還是SDR還是DDR

DATA_WIDTH:參考上面數(shù)據(jù)總線設(shè)置的內(nèi)容

INTERFACE_TYPE:接口類型,默認(rèn)使用"NETWORKING"

NUM_CE: 時(shí)鐘使能數(shù)量,默認(rèn)使用2

SERDES_MODE:當(dāng)使用級(jí)聯(lián)ISERDES時(shí),數(shù)據(jù)從Master ISERDES輸入,使用一個(gè)ISERDES設(shè)為"MASTER",兩個(gè)ISERDES級(jí)聯(lián)使用,另一個(gè)為"SLAVE";詳細(xì)可見下面講到級(jí)聯(lián)時(shí)的內(nèi)容

其他的屬性可以保持默認(rèn)

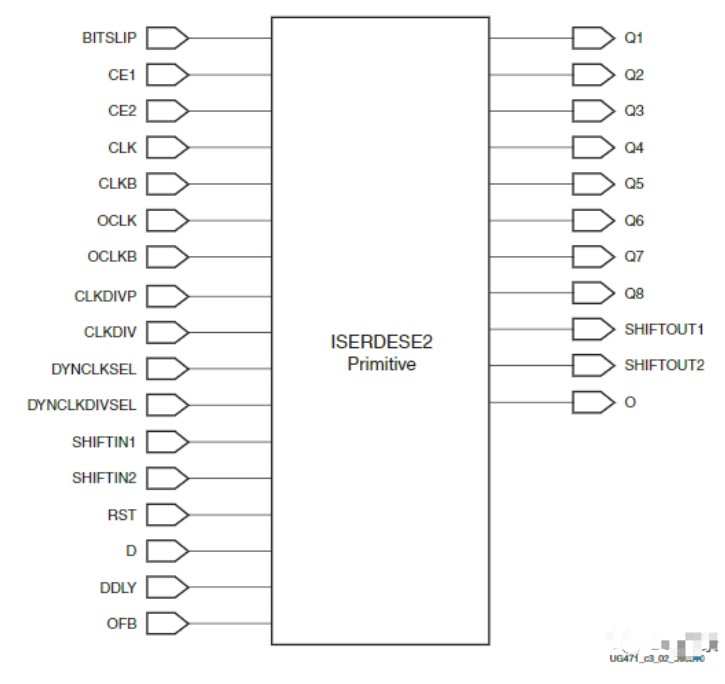

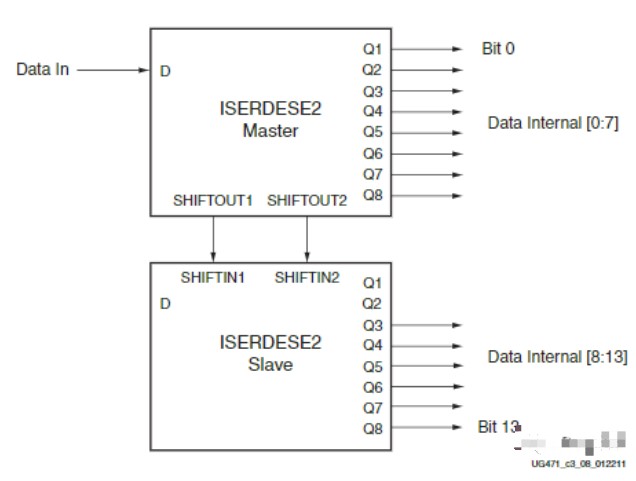

UG471 Figure 3-2

ISERDES2重要端口設(shè)置:

Q1-Q8: 數(shù)據(jù)輸出;注意當(dāng)級(jí)聯(lián)時(shí),"SLAVE" ISERDES的Q3-Q8為并行數(shù)據(jù)的第8-13位;

SHIFTOUT:級(jí)聯(lián)時(shí)使用,詳見下文

SHIFTIN:級(jí)聯(lián)時(shí)使用,詳見下文

D:從IOB來的數(shù)據(jù)

DDLY:從Idelay2來的數(shù)據(jù),D端口從輸入引腳接入后沒經(jīng)過處理,DDLY經(jīng)過Idelay2處理;Idelay詳見(LVDS差分信號(hào)簡(jiǎn)單處理)3. Idelay對(duì)時(shí)序的補(bǔ)救

CLK,CLKB:串行時(shí)鐘,快鐘,CLKB是CLK取反處理

CE1,CE2:快慢鐘的使能

RST:原語(yǔ)復(fù)位,高復(fù)位

CLKDIV:并行鐘,慢鐘

BITSLIP:bit移位功能,詳見下文

時(shí)鐘部分說明:

SDR下:假設(shè)接收的串行數(shù)據(jù)時(shí)鐘為256MHz,解串因子為8,則CLKDIV為32MHz;

CLKDIV = CLK/DATA_WIDTH

DDR: CLKDIV = 2 * CLK/DATA_WIDTH

注意CLK和CLKDIV要相位對(duì)齊;

在NETWORKING模式下,ISERDES輸出要晚于輸入2個(gè)CLKDIV周期;

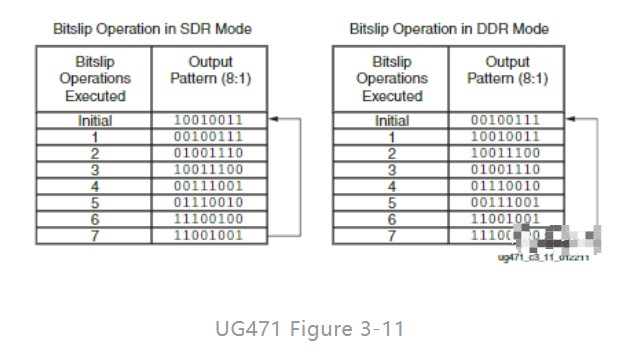

BITSLIP功能說明:

數(shù)據(jù)串轉(zhuǎn)并的過程中,如果沒有確定好數(shù)據(jù)邊界,解串的數(shù)據(jù)也不是正確的,這個(gè)時(shí)候就需要使用BITSLIP功能:

在SDR和DDR下,bitslip移位的位數(shù)并不一樣:

SDR下,一個(gè)bitslip脈沖使數(shù)據(jù)左移一位;DDR下,一個(gè)bitslip脈沖使數(shù)據(jù)右移一位或左移三位;

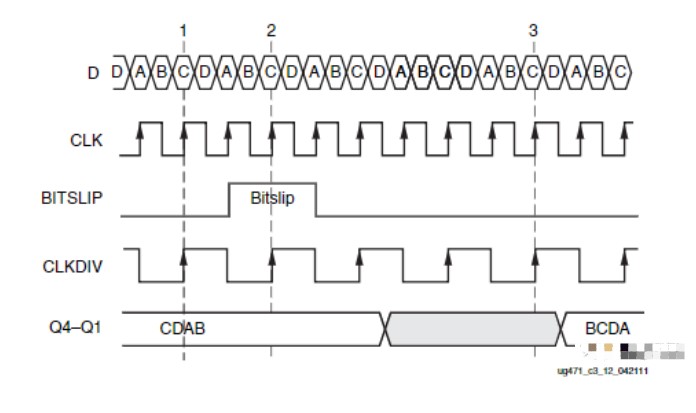

BITSLIP時(shí)序 UG471 Figure 3-12

可以從上圖看出,BITSLIP在CLKDIV時(shí)鐘下,一個(gè)完整的脈沖可以使輸出數(shù)據(jù)產(chǎn)生相應(yīng)的變化;

所以在某些傳輸過程中,可以先開始傳輸預(yù)設(shè)值,等待接收方調(diào)整Idelay和BITSLIP解出正確的預(yù)設(shè)值后,開始傳輸真正的數(shù)據(jù)。

ISERDES級(jí)聯(lián)使用:

SDR Rate下,一個(gè)ISERDES能夠解串的最大數(shù)據(jù)寬度為8;在某些ADC中,其并行數(shù)據(jù)寬度大于8位,這個(gè)時(shí)候可以使用上ISERDES的級(jí)聯(lián)功能:

級(jí)聯(lián)示意圖 UG471 Figure 3-8

首先 設(shè)置一個(gè)ISERDES的SERDES_MODE屬性為"MASTER",另一個(gè)為"SLAVE";

設(shè)置"MASTER"和"SLAVE" ISERDES2的DATA_WIDTH數(shù)據(jù)寬度為同一個(gè)數(shù)(10或14);

將"MASTER"的SHIFTOUT1,2連接至"SLAVE"的SHIFTIN1,2

DATA_WIDTH為10時(shí),"SLAVE"的Q3-4為第8-9位;DATA_WIDTH為14時(shí),"SLAVE"的Q3-8為第8-13位。

仿真結(jié)果:

找到預(yù)設(shè)值才開始傳輸真正的數(shù)據(jù)

注意,獨(dú)立使用VCS,VERDI仿真ISERDES時(shí),需要使用某些設(shè)置才能仿真成功,具體請(qǐng)參考VCS獨(dú)立仿真Vivado IP核的一些方法總結(jié)

總結(jié):

ISERDES2可以使用SelectIO IP核設(shè)置簡(jiǎn)化原語(yǔ)設(shè)置流程;但I(xiàn)SERDES2原語(yǔ)設(shè)置會(huì)更加精細(xì)

BITSLIP功能很有用,需要用它找到數(shù)據(jù)的正確邊界。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1636文章

21841瀏覽量

608495 -

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8784瀏覽量

148893 -

DDR

+關(guān)注

關(guān)注

11文章

717瀏覽量

65782 -

SerDes

+關(guān)注

關(guān)注

6文章

204瀏覽量

35257 -

數(shù)據(jù)總線

+關(guān)注

關(guān)注

2文章

59瀏覽量

17698

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

80SJNB Advanced 均衡和串行數(shù)據(jù)分析方法

多FPGA系統(tǒng)中自定義高速串行數(shù)據(jù)接口設(shè)計(jì)

多FPGA系統(tǒng)中自定義高速串行數(shù)據(jù)接口設(shè)計(jì)

Sync_Header Bits如何從串行數(shù)據(jù)中獲取正確的Header Bits?

怎么實(shí)現(xiàn)基于FPGA的具有流量控制機(jī)制的高速串行數(shù)據(jù)傳輸系統(tǒng)設(shè)計(jì)?

高速CAN通訊總線接收到無(wú)效串行數(shù)據(jù)是何原因?怎么解決呢?

【verilog每日一練】位拼接符的應(yīng)用:如何實(shí)現(xiàn)串行數(shù)據(jù)的接收與輸出

串行數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù)

并行數(shù)據(jù)轉(zhuǎn)換為串行數(shù)據(jù).hex

多FPGA系統(tǒng)中自定義高速串行數(shù)據(jù)接口設(shè)計(jì)

基于8051的Proteus仿真-串行數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù)

高速串行數(shù)據(jù)挑戰(zhàn)與TDR阻抗測(cè)試和高速串行鏈路的分析

使用ISERDES接收高速串行數(shù)據(jù)

使用OSERDES發(fā)送高速串行數(shù)據(jù)

測(cè)量串行數(shù)據(jù)信號(hào):選擇合適的示波器帶寬

使用ISERDES接收高速串行數(shù)據(jù)

使用ISERDES接收高速串行數(shù)據(jù)

評(píng)論