高速ADC一直是個特別火的課題,無論是科研還是實際項目。與此同時,高速動態comparator的設計也就隨之非常普遍。在這里,作者君想跟大家分享一下自己所采用的兩種對comparator input referred noise的仿真方法。大家有什么疑問或者經驗分享,請在評論區留言。

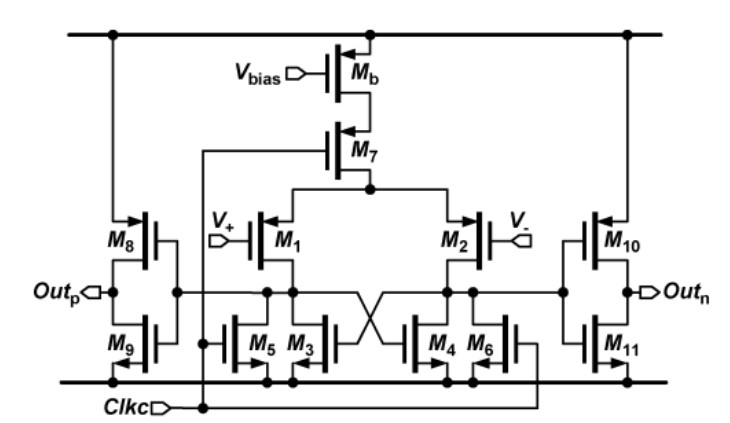

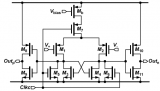

一個典型的dynamic comparator,如圖所示:

這篇來自CC.Liu的SAR ADC 設計,目前citations已經過千,想必很多讀者都看過了。沒看過的建議去看看,確實是經典。

對于一個這樣的comparator,沒有傳統的模擬pre-amp,整個電路都是dynamic的。因此,如何對input referred noise進行仿真呢?作者君有如下兩種方法:

Transient noise

大致的思路是這樣的:

加一個快于實際工作的時鐘頻率;

在輸入端加一個DC的差(比如一端是0.5VDD,另外一端加0.5VDD+0.2mV);

計算仿真時間內的counting number,和correct counting number(比如時鐘頻率是1GHz,仿真時間是1us,那么應該是1000個counts;用viva的calculator計算正確的counts);

掃描不同的輸入DC差之下,正確的counts的數量(比如輸入差是0.1mV,0.2mV,0.3mV,etc.);

當正確的counts數量大約是84%的時候,我們認為此時的input差就是一個sigma(50%+0.5*68%=84%);

當PVT改變的時候,可以不斷重復上面的步驟,來求得對應的sigma;

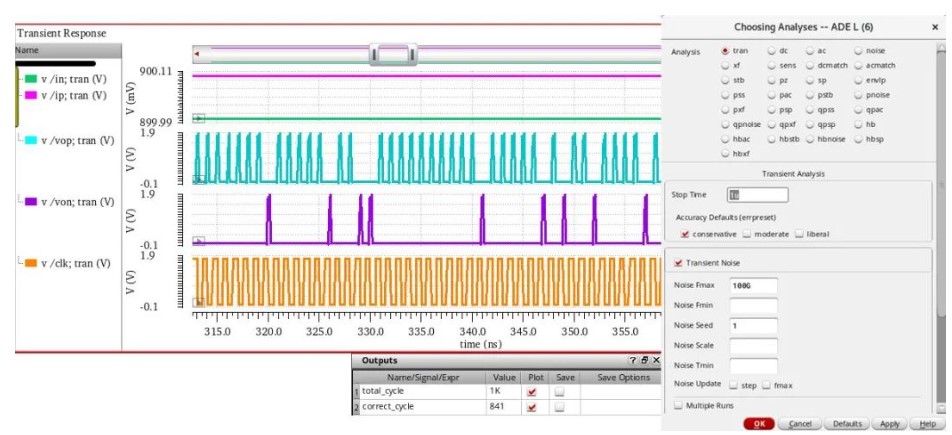

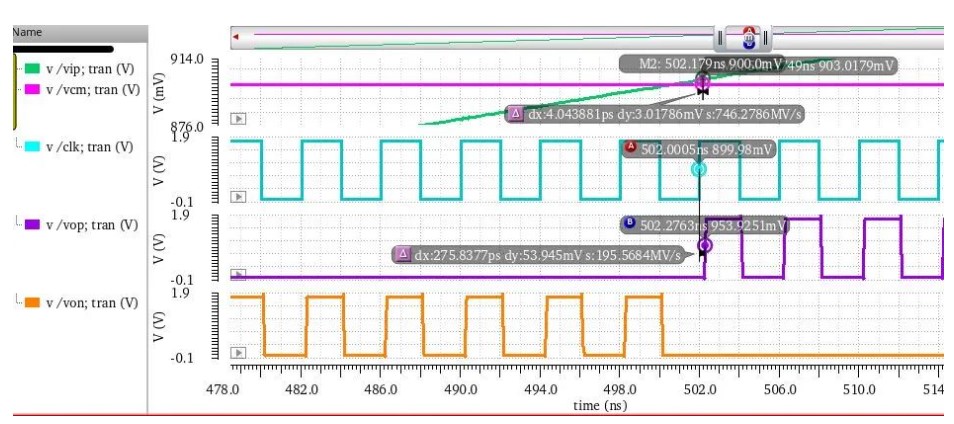

Transient Noise settings and simulation results (Input difference is 0.1mV)

作者君的transient noise設置和仿真結果如上圖。可以看到,當input的差別很小的時候(Vip大于Vin),本來應該是只有Vop出現pulse,Von全部應該是0。但是由于noise的存在,導致某些錯誤的輸出。

按照前面的方法,用calculator計算出全部和正確的counts數量。可以看到,目前的正確counts大概是84%,也就是對于一個input referred noise sigma.

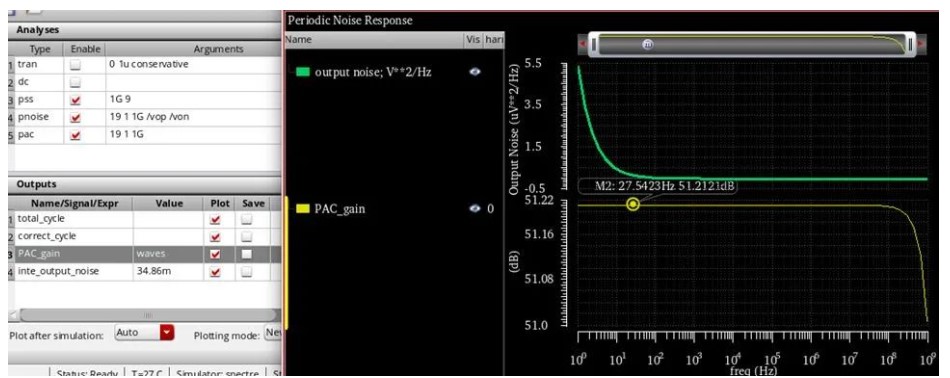

PSS+Pnoise

大致的思路是這樣的:

加一個快于實際工作的時鐘頻率;

在輸入端加一個DC的差;

采用PSS,PAC, Pnoise的仿真;

Pnoise計算出integrated output noise(用V^2/Hz作積分然后sqrt做開方);

PAC計算出comparator的gain;

第四步得到的noise除以第五步得到的gain,就是input referred noise;

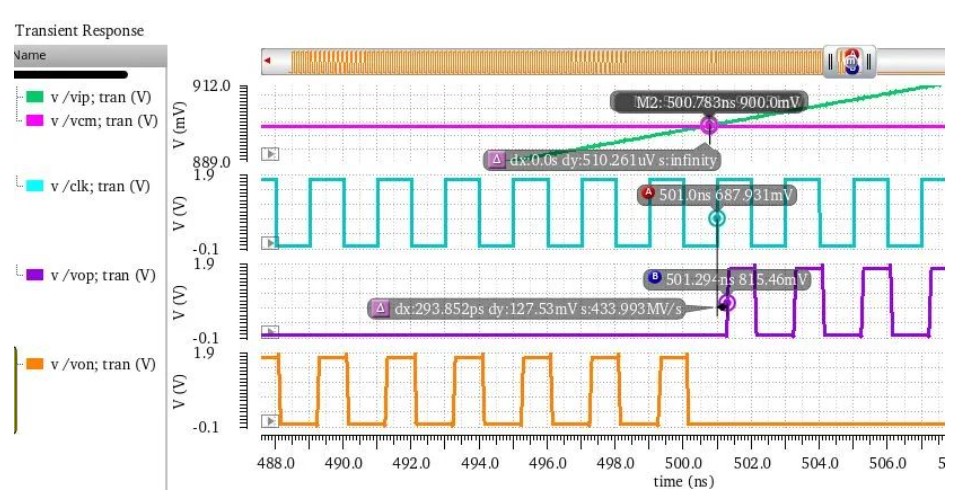

Input difference is 0.1mV.Pnoise integration is from 1Hz to 500MHz. The output noise is 34.86mV.With PAC gain of 51dB (363.584), the input referred noise is 0.096mV ~ 0.1mV.

相比于Transient noise,這種pnoise的方法一步就能得出input referred noise;所以也有paper專門對比過效率。

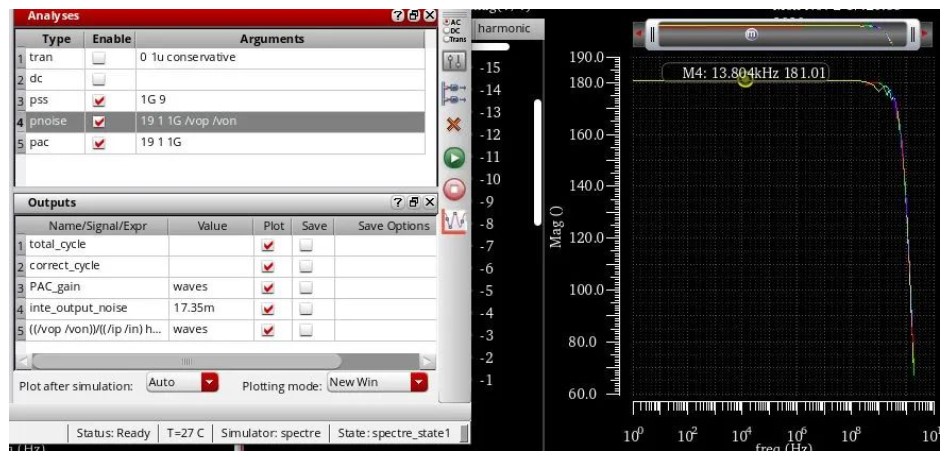

上面這張圖是input差為0.1mV時候的仿真結果。作者君又勤快了點,多跑了一個仿真:

Input difference is 0.2mV.Pnoise integration is from 1Hz to 500MHz. The output noise is 17.35mV.With PAC gain of 45dB (181), the input referred noise is 0.096mV ~ 0.1mV.

當input差別變成0.2mV的時候,相對應的輸出pnoise變小了差不多一半(34mV變成17mV),同樣的,PAC得到的增益gain也減小了一半。因此,最后得到的input referred noise也基本上沒變。

最后,對比一下transient noise 和Pnoise的結果,可以看到,我們拿到的input referred noise差不多都是0.1mV。哈哈哈,結果挺相符的,太棒了!(作者君這個comparator做得不錯吧?加大input pair的size真的是挺有用的……就是面積有點大……囧)

PS:關于加的時鐘頻率比實際工作頻率要高這點,作者君不是特別確定。希望讀者們可以給出評論。謝謝大家!

在正常的用vpwl sweep comparator一端,固定另外一端的transient仿真時,比如工作頻率是250MHz,可能出現因為時鐘上升沿剛好沒有對齊輸入過零點導致的誤差。這種情況下,加500MHz的時鐘,可能會避免出現這種誤差。

當clock是250MHz的時候,因為clock的rising edge沒有對上,所以此時input的差是3mV,comparator對這個3mV的差做出了相應的切換。所以這個3mV主要是clock的edge造成的,noise的原因非常小。

當clock是500MHz的時候,因為clock的rising edge跟過零點非常接近,所以此時input的差是0.5mV,comparator對這個0.5mV的差做出了相應的切換。

審核編輯:劉清

-

時鐘頻率

+關注

關注

0文章

49瀏覽量

20333 -

高速ADC

+關注

關注

0文章

47瀏覽量

28566 -

電路仿真

+關注

關注

36文章

208瀏覽量

95679 -

PAC

+關注

關注

0文章

72瀏覽量

27907

發布評論請先 登錄

相關推薦

電池電量的兩種測試方法

兩種LED驅動模式的功能及使用方法

差模與共模兩種噪聲介紹

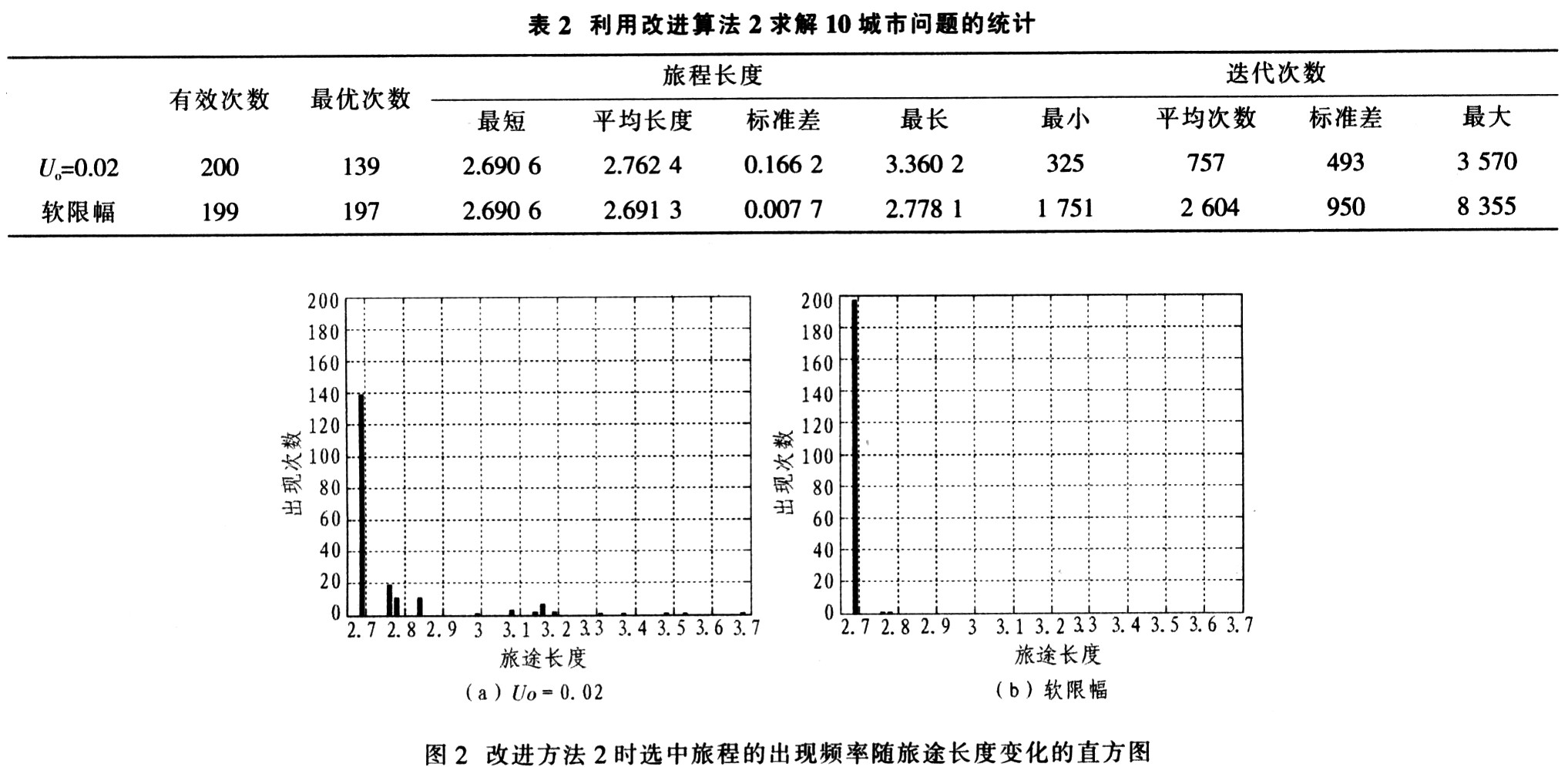

Hopfield網絡求解TSP兩種改進算法的仿真研究

匹配網絡兩種設計方法的對比研究

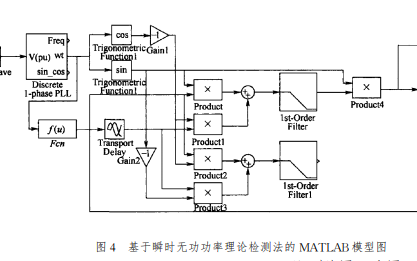

兩種單相電路諧波及無功電流檢測方法的詳細比較資料說明

PCI設備兩種底層訪問方法的實現及比較分析

Comparator動態噪聲的仿真

淺析Comparator動態噪聲的仿真

分享兩種Comparator動態噪聲的仿真方法

分享兩種Comparator動態噪聲的仿真方法

評論