2022年8月22日,數字實現EDA先進解決方案供應商芯行紀科技有限公司(以下簡稱“芯行紀”)宣布推出首款自主研發的數字實現EDA產品——AmazeFP智能布局規劃工具。

AmazeFP將機器學習技術與布局規劃引擎結合,在兼顧性能、功耗和面積(PPA)的同時,提供了高度智能的擁塞感知、便捷的數據流分析和宏單元自動整理對齊功能,有效解決當前數字芯片在后端設計階段布局規劃節點面臨的經驗值需求高、手工耗時長、數據流結構分析手段單一、設計問題后期定位收斂性差等難題,助力用戶在后端設計初期快速有效地獲取優化布局方案,減少迭代次數,從而節約大規模設計的研發成本,提速產品上市時間。

AmazeFP:高度智能化的布局規劃工具

芯片設計進入后端設計流程后,依次會進入布局規劃、標準單元擺放、時鐘樹生成、布線、優化等階段。伴隨先進工藝制程的不斷進步,設計的規模日益擴大,隨之每一個設計環節需要的時間也愈長,例如一個GPU模塊布局規劃方案可能要經歷數十輪次迭代和花費數周才能初步定型,模塊開發人員在應對優化PPA的要求時也承受著巨大的時間目標壓力,而芯片布局規劃作為芯片后端設計流程中的第一步,起著萬丈高樓始于基石的重要作用。表現優異的布局規劃不僅能實現更好的PPA,也為設計流程的后續步驟提前掃除障礙,加速設計收斂,保證項目高質量地順利流片。

融合機器學習技術,擁有智能擁塞感知模型,內嵌數據流導向引擎,自動整理對齊宏單元等新一代數字實現EDA軟件特征,使得AmazeFP在布局規劃過程中表現優越。

//

AmazeFP采用的機器學習技術在考慮了時序、面積、功耗因素的基礎上快速獲取高質量的宏單元布局思路,提供初步布局規劃;

智能擁塞感知模型可以大幅提升擁塞預測的精確度,并據此調整宏單元位置,確保芯片整體的可繞通性;

內置的數據流導向引擎,可自動規劃分組宏單元擺放,減少各模塊之間總體布線長度,加速宏單元關鍵路徑的時序收斂;

自動整理對齊功能可以根據用戶所選的宏單元自動生成網格化歸準窗口,極大節省用戶手動規整對齊宏單元的時間。

AmazeFP實際使用案例

1

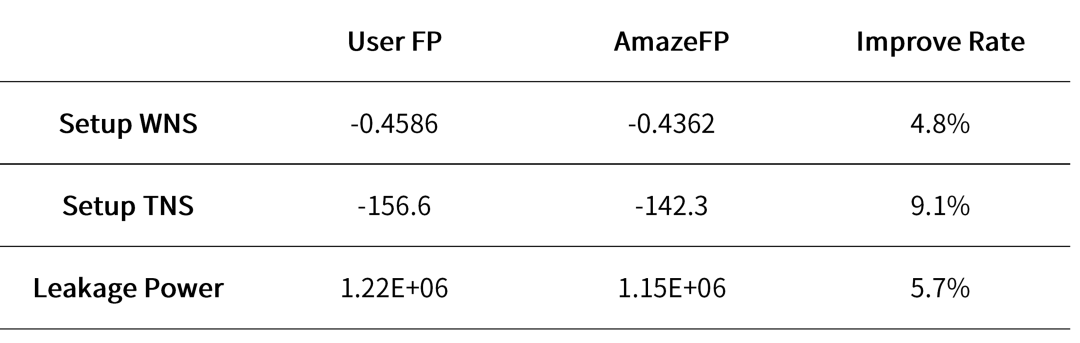

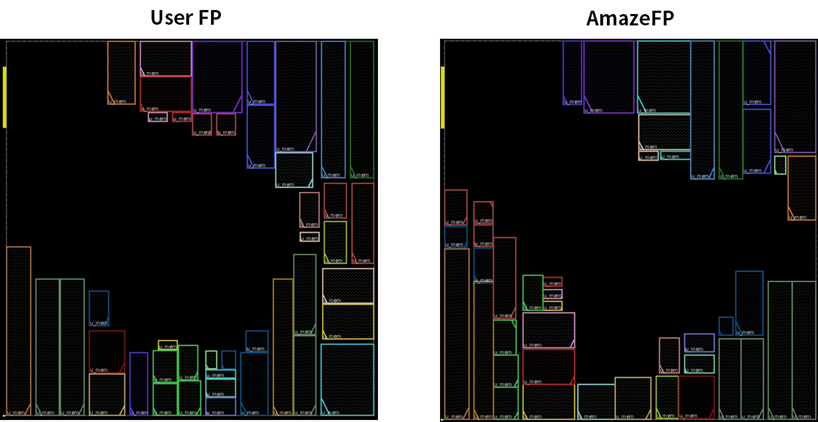

案例一為視頻編解碼設計模塊,該設計共包含44個宏單元,工作頻率為1.5GHz。如圖一所示,左圖為工程師經過數次調整和迭代之后確定的手動擺放的宏單元布局,整體耗時約為三天,右圖為AmazeFP依據設計數據流結構以及布線擁塞感知之后自動擺放的宏單元布局,整體運行時間為30分鐘。根據這兩種布局規劃,在全部完成布局布線工作后,對比時序的結果,AmazeFP的全局Setup WNS和Setup TNS相較于手動布局規劃分別有4.8%和9.1%的提升,其中Reg2Reg Setup WNS改善54.6%,Reg2Reg Setup TNS改善86.1%。與此同時,AmazeFP提供的布局方案節省了5.7%的靜態功耗。

表一:案例一手動布局規劃與AmazeFP自動處理結果對比

圖一:視頻編解碼設計模塊的宏單元布局對比

2

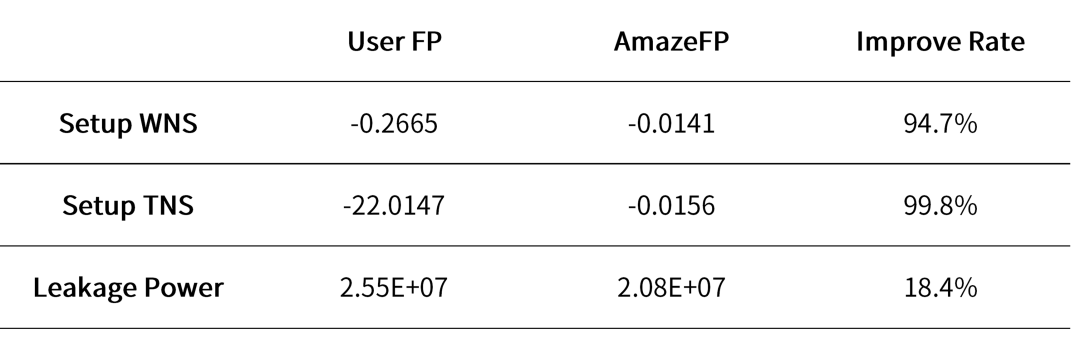

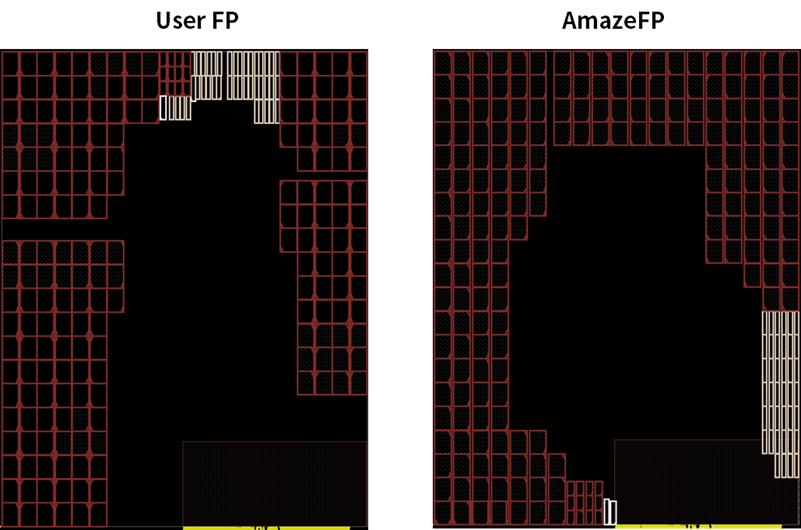

案例二為GPGPU設計模塊,該設計中共包含246個宏單元,工作頻率為1GHz。如圖二所示,左圖為工程師耗時5天經過多次迭代調整之后手動擺放的宏單元布局,右圖為AmazeFP 2小時內自動擺放的宏單元布局。經過相同設置的布局布線流程后,時序結果分析顯示,AmazeFP的全局Setup WNS和Setup TNS分別有94.7%和99.8%的提升,其中Reg2Reg Setup WNS 和 Setup TNS為0。在功耗優化方面,AmazeFP相較于手動布局規劃減少12.6%的繞線長度(Wirelength)和18.4%的靜態功耗。

表二:案例二手動布局規劃與AmazeFP自動處理結果對比

圖二:GPGPU設計模塊的宏單元布局對比

AmazeFP優客計劃

芯行紀堅持用創新來引領數字實現EDA產品的自主研發,在解決產品功能實現的基礎上,追求Smart、Speedy、Simple的“3S”產品理念,把機器學習等技術真正貫穿于基礎軟件架構和具體功能實現,從豐富的設計經驗中提煉關鍵需求,著力于解決設計過程的真正痛點。基于強大的研發團隊實力,芯行紀期待聆聽合作伙伴的創意需求,“AmazeFP優客計劃”致力于及時地將任何能夠提升設計效率的優秀創意展現于產品的更新版本。

審核編輯 :李倩

-

智能化

+關注

關注

15文章

4897瀏覽量

55440 -

機器學習

+關注

關注

66文章

8422瀏覽量

132712

原文標題:芯行紀推出首款自主研發的智能布局規劃工具AmazeFP

文章出處:【微信號:gh_2894c3fc5359,微信公眾號:芯行紀】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

艾偉達發布數字芯片EDA工具adsDesigner

聯合電子首款800V高壓平臺逆變磚產品實現量產交付

國內首款自主研發28nm顯示芯片量產

國數集聯研發出首款CXL多級網絡交換機

國芯新材料研發并推出全球首款可商用的鉀離子電池產品

本源超導量子計算機自主制造鏈11類產品系列之一:國產首個量子芯片設計工業軟件Q-EDA

首款自主研發的數字實現EDA產品——AmazeFP

首款自主研發的數字實現EDA產品——AmazeFP

評論