可測性設計工具針對集成電路生產測試需要,通過人工插入或工具自動綜合生成測試邏輯電路,自動產生測試向量。可測性設計工具可以顯著提升測試覆蓋率,有效降低芯片在自動測試設備(Automatic Test Equipment,ATE)上測試的困難度及成本。

1.測試電路的自動生成

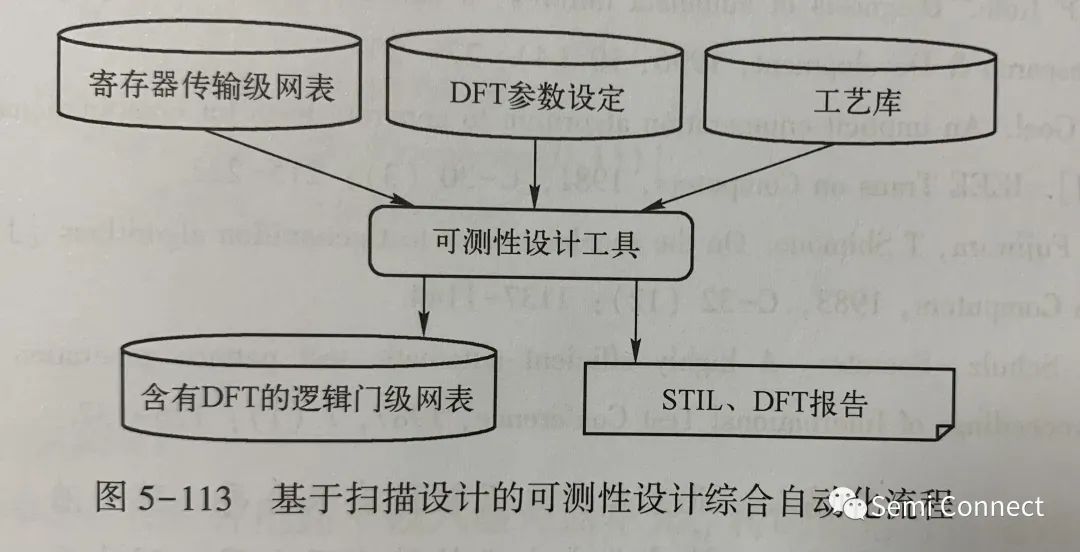

基于掃描設計(Scan-Based Design)方法是一種最常用的可測性設計方法。它把被測電路的寄存器轉換成掃描寄存器,再將掃描寄存器連接成一條或多條的掃描鏈以傳遞測試信號。可測性設計的測試電路生成涉及一系列復雜的操作,通常需依靠自動化工具輔助完成。一個典型的基于掃描設計的可測性設計綜合自動化流程如圖5-113所示。

該流程包括下列幾個主要步驟:

(1)將普通寄存器時序單元轉換成掃描寄存器;

(2)檢測被測電路是否符合一系列的DFT規則;

(3)對任何違反DFT規則的電路部分,進行自動修復或人工修復;

(4)根據DFT約束及目標設定,進行掃描鏈的鏈接并合成所需添加的邏輯。

測試電路的自動生成結果包括含DFT的邏輯門級電路網表、使用STIL(Standard Test Interface Language,標準測試接口語言)描述的DFT 工作情況以及DFT分析報告。

2.測量向量的自動生成及優化

基于DFT網表和STIL結果,自動測試向量生成工具可以自動產生芯片測試所需的測試向量信號。測試向量經過編碼壓縮、廣播式壓縮、邏輯變換壓縮等方法優化后,在保證測試覆蓋率的前提下可以減少測試數據數量、測試時間和必需的測試通道數。

D算法(又稱多維通路敏化法)是第一個完備的ATPC算法,其基本思想是利用電路簡化表和D向量傳遞,使故障沿著所有敏化通路傳播至輸出,通過兼容性檢查得到最終的測試向量。針對大型組合電路中敏化通路選擇的有效性,PODEM算法和FAN算法又對D算法進行了改進。后來的SOCRATES利用功能學習的方法提升了邏輯蘊含、通路敏化以及多路回退的效率。業界ATPG工具多采用基于類似SOCRATES的方法,并做了更進一步的改進。

除了上述的基于掃描設計DFT方法,業界還有幾種不同的DFT解決方案。例如,LBIST(Logic Built -In Self-Test)將特殊的硬件或軟件加入電路中,在不需要外在測試設備的條件下進行電路自測試。相對于LBIST,MBIST(Memory Built-In Self-Test)可用于存儲器的自測試。

審核編輯:劉清

-

邏輯電路

+關注

關注

13文章

502瀏覽量

43145 -

寄存器

+關注

關注

31文章

5412瀏覽量

123180 -

測試電路

+關注

關注

2文章

46瀏覽量

32541

原文標題:可編程邏輯電路設計—可測性設計工具

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

可編程交流負載標準

可編程混合信號技術彌補邏輯IC的成本與密度空白

德州儀器 (TI) 全新可編程邏輯產品系列助力工程師在數分鐘內完成從概念到原型設計的整個過程

邏輯電路芯片-組合邏輯電路芯片-時序邏輯電路芯片

用TMAG5328電阻器和電壓可編程霍爾效應開關實現可編程性和診斷

評論