電路設計中,滿足MCU的上電時序,是系統設計最基本最重要的要求之一,因此設計中我們會格外關注系統電源的上下電時間。

如果上下電時間過長,可能會導致MCU啟動失敗或系統運行邏輯混亂,因此縮短MCU電源的上電和放電時間就顯得尤為重要。

如何加快系統上電時間?

以LDO或Buck類電源為例,之前項目中遇到一個問題,因為使能引腳EN輸入電壓范圍跟輸入引腳VIN一樣,因此設計時直接將使能引腳接電源,后面板子回來做硬件測試時發現電源上電期間有抖動現象,且上電時間比較長。

后來通過分壓電阻將使能引腳用起來,上電抖動消失,并且上電時間明顯減小。那么,為什么會有這種情況?

原因如下:

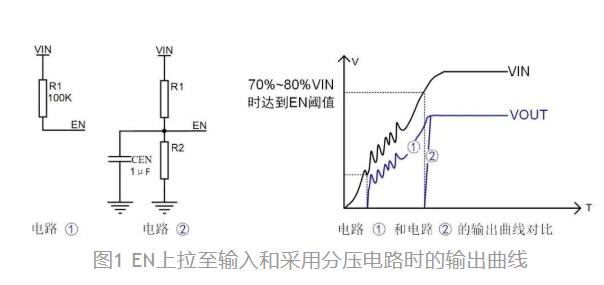

使能引腳通過外部上拉來默認使能,會過早地讓電源芯片達到使能閾值,輸出就會跟隨輸入,即輸入有多慢輸出就有多慢,且上電時輸入端的抖動也會傳送給輸出,并且這種接法在輸入電壓不高的情況下打開芯片可能會導致芯片輸出又跌落的情況發生。如下圖1所示為設置EN直接上拉和采用分壓電路時的輸出曲線示意圖。

曲線①,使能上拉至輸入,此時輸出上升時間長且會受到輸入波動的影響。曲線②,合理采用分壓電阻,當VIN上升到70%~80%的時候,再使EN的電壓到達使能閾值,此時輸出上升邊沿陡峭,輸出平穩,摒除了輸入電源的不穩定階段,減小了輸入電壓波動的影響。同時預留了20%~30%的余量,避免電源波動導致輸出關閉。此時的上電對于MCU來說才是干凈利落的。

系統快速下電的必要性

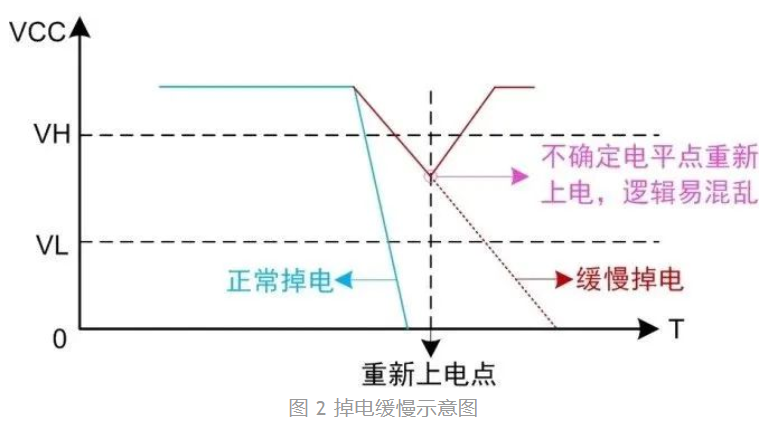

系統在做快速上下電測試時,經常會遇到由于下電緩慢,導致系統下電不完全導致的重新開機邏輯混亂問題,如下圖2所示。

如上圖2所示,當電源掉電,負載不能及時泄放能量時,就會出現MCU等數字器件掉電緩慢的情況。若此時重新上電,由于芯片內部無法及時“歸零”,對MCU等數字器件來說,這是一種不確定的狀態,此時再對系統進行重新上電的操作,就容易造成MCU邏輯混亂,系統不能啟動的情況。因此電源關閉后使MCU的電源快速下降至近0V,使系統在短時間內到達一種確定的狀態,也是快速重新上電時系統能正常啟動的關鍵因素。

f方法如下:

以LDO為例,有的LDO芯片內部是帶有快速泄放電路的,如下圖3規格書中描述。這是一款帶有快速放電功能的電源芯片。其內部功能框圖如下圖4所示,基本原理是使能引腳EN拉低后,通過反相器變為高電平到達內部NMOS,此時NMOS的Vgs>0,因此導通將輸出VOUT拉低到GND泄放能量。

搭建分立電路做快速泄放電路

開關SW閉合時:

5V電源通過二極管D1成為電壓4.7V-Out。因為二極管D1是一個肖特基二極管,其正向壓降比較小,約為0.3V。

此時三極管Q1的b極電壓為5V,e極電壓為4.7V,Q1不導通

開關SW斷開時:

三極管Q1的e極電壓從4.7V開始下降,b極電壓從4V開始下降,Vbe = -0.7V,將Q1打開,大電容C1的電壓4.7V-Out通過三極管Q1、電阻R2快速泄放到地。

審核編輯 黃昊宇

-

電源

+關注

關注

184文章

17718瀏覽量

250147 -

mcu

+關注

關注

146文章

17148瀏覽量

351186 -

電路設計

+關注

關注

6673文章

2453瀏覽量

204350

發布評論請先 登錄

相關推薦

CDN輸出端口電快速瞬變脈沖群波形的校準方法

解決MCU應用系統中上電暫態時輸出失控的方法

快速的學習方法?

Linux下組態,快速實現監控系統

IGBT快速損耗計算方法

一種基于Flash的VxWorks操作系統快速引導方法設計

系統快速下電的方法

系統快速下電的方法

評論