上一篇講到了vref,這篇接著說(shuō)。

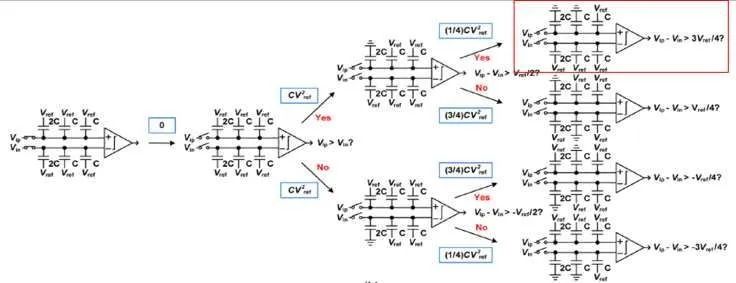

已知如果vip大于vin,那么一端連到vip的電容,另外一端連到vss的自然比較多,連到vref就少一些。對(duì)于vin,則是相反的,連到vref的比連到vss的多。于是,作者君畫(huà)了下面這張圖:

symbol畫(huà)的比較大的電容,表示這個(gè)電容比較大。

跟上一篇的電路圖相比,作者君多畫(huà)了四個(gè)電容。

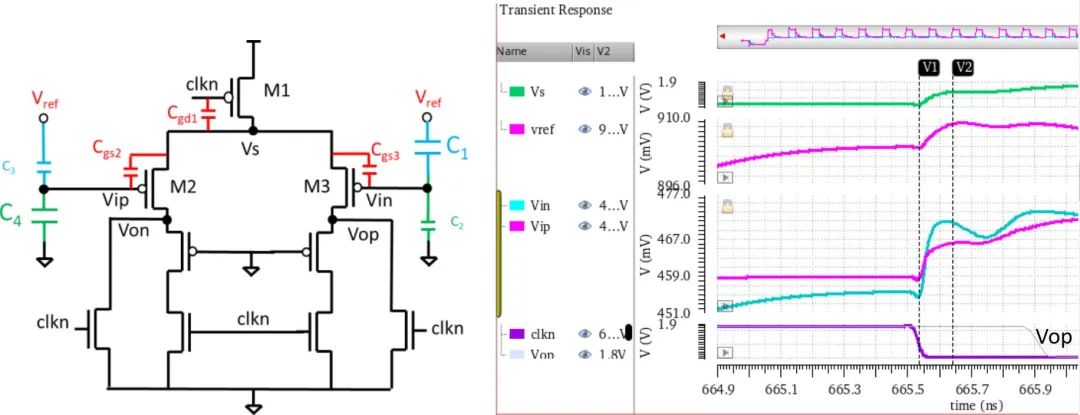

前面說(shuō)到因?yàn)閏lkn導(dǎo)致的Cgs1把M2和M3的gate都往下拉了一點(diǎn)點(diǎn),因此,通過(guò)較大的C1(vin和vref之間的電容)和較小的C3(vip和vref之間的電容),這個(gè)電容之間拉扯的動(dòng)作影響到了vref。所以我們看到的右邊第二行vref,也被拉下來(lái)了一點(diǎn)點(diǎn)。

vref自然是有個(gè)LDO來(lái)提供精準(zhǔn)的0.9V的。現(xiàn)在vref被拉下來(lái)一點(diǎn)點(diǎn),LDO(或者是buffer)必然會(huì)相應(yīng)這個(gè)變化,于是,我們?cè)趘1和v2之間看到第二行的vref有個(gè)上升的動(dòng)作。于是,通過(guò)C1和C3,vin和vip也跟著往上走。但是,為什么藍(lán)色的vin上升得比較快呢?想到高頻情況下,電容的等效阻抗1/cs跟電容的值成反比。于是vin連到vref的C1等效阻抗比較小,而vip連到vref的C3等效阻抗比較大。所以,可以解釋vin的快速上升過(guò)程。

寫到這里,大家自然可以想到,如果讓嘗試vref的LDO(或者是buffer)的負(fù)載電容大一些,是不是可以減小這個(gè)過(guò)沖的幅度呢?當(dāng)然是可以的,作者君把負(fù)載電容從10pF增大到50pF,也可以跟前文講的減小M1一樣,得到正確的波形,而且不犧牲反應(yīng)速度。(犧牲的自然是電容的面積了……)

或者不那么極端,稍微減小一點(diǎn)M1,然后同時(shí)增大負(fù)載電容,搭配起來(lái)使用,其實(shí)也不錯(cuò)。

講到這里其實(shí)差不多可以完結(jié)撒花,不過(guò)作者君還想再說(shuō)完。有興趣的讀者可以接著看下去。

說(shuō)一個(gè)跟vref和capacitor array有關(guān)的東西:

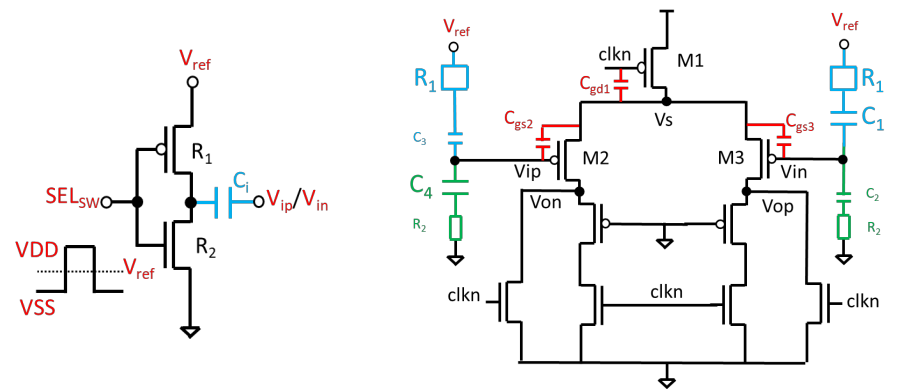

左圖是每個(gè)電容的開(kāi)關(guān),右圖是加上了開(kāi)關(guān)的等效電阻

Capacitor array每個(gè)電容的開(kāi)關(guān)如左圖,輸入在vdd和vss之間,所以對(duì)于上面的pmos來(lái)說(shuō),最大的vgs是vref-0也就是vref,下面的nmos的最大vgs是vdd-0也就是vdd。所以等效電阻,上面的pmos的R1大于下面的nmos的R2.于是作者君就在comparator的第一級(jí)畫(huà)上了這兩個(gè)R。

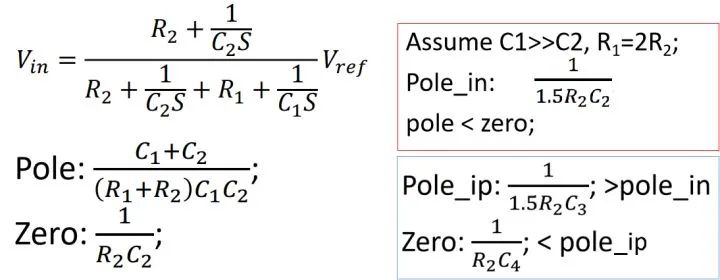

簡(jiǎn)單算一下從vref到vin或者vip的傳輸函數(shù):

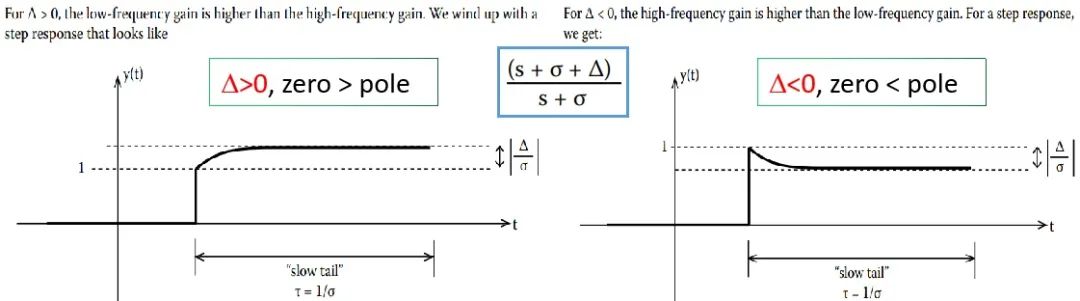

所以vin和vip兩邊,一個(gè)是pole小于zero,一個(gè)是pole大于zero。對(duì)于比較接近的doublet來(lái)說(shuō),用step response解釋就是:

到這里也就解釋了為什么過(guò)了圖2的v2那條線之后,vin和vip的差距一度很大。

審核編輯:湯梓紅

-

電容

+關(guān)注

關(guān)注

100文章

6038瀏覽量

150272 -

ldo

+關(guān)注

關(guān)注

35文章

1940瀏覽量

153311 -

Doubler

+關(guān)注

關(guān)注

0文章

7瀏覽量

7185 -

DEBUG

+關(guān)注

關(guān)注

3文章

93瀏覽量

19907

原文標(biāo)題:一個(gè)傳統(tǒng)double tail comparator的debug過(guò)程(二)

文章出處:【微信號(hào):analogIC_gossip,微信公眾號(hào):通向模擬集成電路設(shè)計(jì)師之路】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

tail實(shí)時(shí)滾動(dòng)顯示log文件內(nèi)容

Implementing Double Data Rate

DEBUG程序的使用

Dual Comparator Forms Temperat

Comparator/DAC Combinations So

LTC1540-Nanopower Comparator w

基于Tail Fit算法的抖動(dòng)分離

Linux中tail與cat的區(qū)別

結(jié)合搜索與Double DQN的非完備信息博弈算法

AD45048:Rail-Tail在ADSL線驅(qū)動(dòng)數(shù)據(jù)Sheet上運(yùn)行.

配置VScode編譯、調(diào)試STM32(二)Cortex-Debug插件

HT8 MCU Comparator應(yīng)用須知

double tail comparator的debug過(guò)程(二)

double tail comparator的debug過(guò)程(二)

評(píng)論