鎖存器是具有兩個穩定狀態的時序邏輯電路,即它是雙穩態多諧振蕩器。鎖存器有一個反饋路徑來保留信息。因此,鎖存器可以是存儲設備。只要設備處于開機狀態,鎖存器就可以存儲一位信息。當使能啟用時,鎖存器會在輸入更改時立即更改存儲的信息,即它們是電平觸發設備。當使能信號打開時,它會持續對輸入進行采樣。

取決于觸發信號的高電平或低電平,鎖存電路可以在兩種狀態下工作:有效 - 高電平或者有效 - 低電平。

在Active – High鎖存電路的情況下,通常兩個輸入都是低電平,該電路由任一輸入上的瞬時高電平觸發。

在Active – Low鎖存電路的情況下,通常兩個輸入都為高電平,該電路由任一輸入上的瞬時低電平觸發。

鎖存器主要特性

鎖存器是時序電路中的基本構建元素。鎖存器沒有任何時鐘信號,即它們是異步時序電路。

鎖存器由靜態門組成。

鎖存器是一種雙穩態多諧振蕩器,即它有兩個穩定狀態并且可以在這些狀態之間切換。

鎖存器將具有來自輸出的反饋路徑。因此,它們使用輸入信號的先前和當前狀態隨時改變其輸出。

使能后,鎖存器的輸出會持續受到其輸入的影響,即當輸入改變時輸出會立即改變。禁用時,鎖存器的狀態保持不變,即它會記住以前的值。時鐘或使能信號用作控制信號。

鎖存器不斷檢查所有輸入,并在啟用時相應地更改其輸出。

SR鎖存器

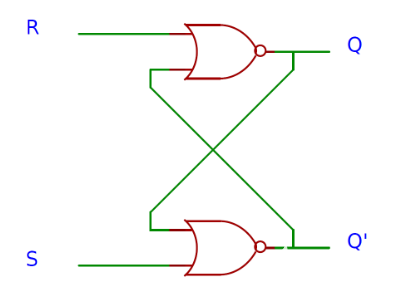

其實,可以使用靜態門作為基本構建塊來構建一個簡單的鎖存器,并且可以通過向NOR門電路引入反饋來構建具有兩個NOR門。

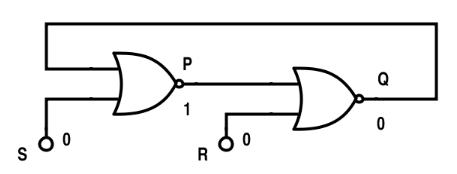

帶反饋的簡單NOR門邏輯電路如下圖所示:

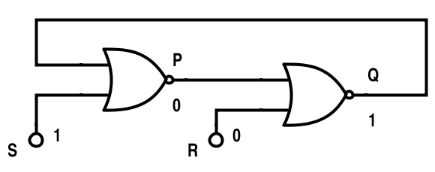

這里,輸入S和R都是0 (S = R = 0)。第一個或非門的輸出是P = 1。這與R = 0一起被饋送到第二個或非門,因此第二個門的輸出是Q = 0。由于電路處于穩定狀態,P = 1,Q = 0,如果使 S = 1,則 P = 0,Q = 1,如下圖所示:

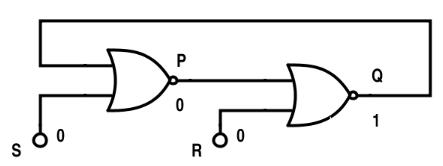

這也是一種穩定的狀態,如果S為0,則沒有變化,因為Q = 1被反饋給第一個NOR,P仍然保持為0,如下圖所示。

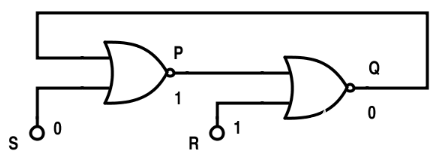

如果R變為1,則Q變為0,這將使P變回1,如下圖所示:

如果R為0,那么就沒有變化,這樣就到達了最開始的地方。

由于輸出不僅取決于當前的輸入,還取決于過去的輸入序列,因此該電路被稱為具有記憶性。如果不允許輸入條件S = R = 1,則穩定狀態輸出始終是互補的。當S和R都等于1時,P = 0和Q = 0,這與互補條件相矛盾。因此,輸入條件 S = R = 1被認為是不允許的。鎖存電路總是畫成交叉耦合形式,以強調柵極之間的對稱性。

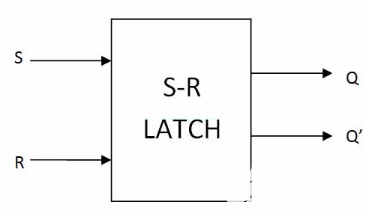

在該電路中,當S=1時,它將輸出Q'設置'為 1,當輸入R=1時,它將輸出Q '重置'為 0。在 S = R = 1的限制下,該電路稱為設置 – 復位鎖存器(SR鎖存器)。

關于競態條件

在邏輯電路中,競態條件是指“邏輯電路的兩個輸入同時變化并使輸出暫定的情況”。輸入相互競爭以改變輸出,它通常發生在將輸出作為電路反饋輸入的設備中。當設備嘗試同時執行兩個操作(即同時更改兩個輸入的狀態)時,會出現這種情況。有幾種方法可以避免條件競爭,例如使用邊沿觸發或使用主從觸發器。

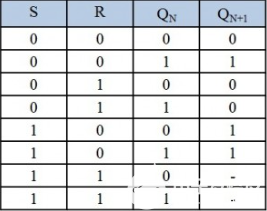

SR鎖存器狀態表

SR鎖存器狀態表(真值表)提供有關電路狀態的信息,由于時序電路的輸出取決于當前和先前的狀態,因此這些以稱為狀態表的表格形式表示,并根據當前狀態和其他輸入顯示下一個狀態。

SR鎖存器的狀態表如下所示:

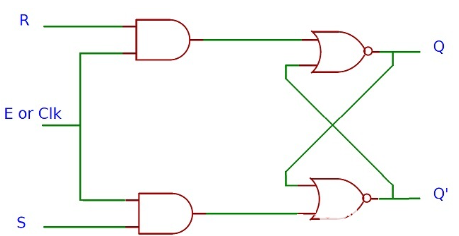

門控SR鎖存器

通常情況下,鎖存器都是即時的,即當輸入發生變化時,輸出會立即發生變化。但對于許多應用來說,最好有一個隔離期,即使輸入發生變化,輸出也不會發生變化。在此期間,輸出被稱為真正“鎖定”。這可以通過使用額外的輸入(使能或時鐘或門)來實現。如果使能(或時鐘或門)信號未置位,則忽略輸入并將輸出鎖存到先前的值。為了使用這個額外的信號,應該添加額外的邏輯,這些電路稱為門控SR鎖存器。

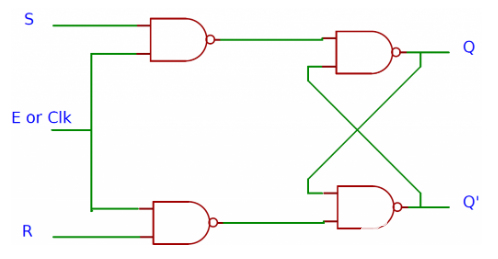

門控SR鎖存器可以通過兩種方式制成:通過將第二級與門添加到SR鎖存器或通過將第二級與非門添加到反向SR鎖存器。

由NOR門構成的門控SR鎖存器的電路圖如下所示:

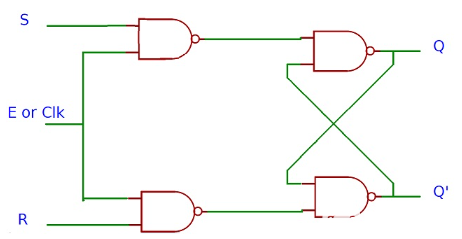

由NAND門構成的門控SR鎖存器的電路圖如下所示:

當NAND門將輸入反相時,反向SR鎖存器變為門控SR鎖存器。當使能(或時鐘)為高時,鎖存器被稱為啟用狀態,即輸出響應輸入。當使能(或時鐘)為低電平時,鎖存器被禁用并保持在該狀態,直到使能啟用。

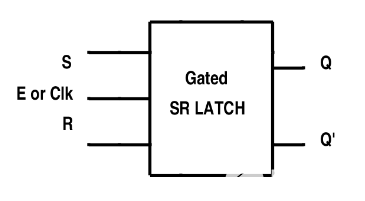

門控SR鎖存器的符號如下圖所示:

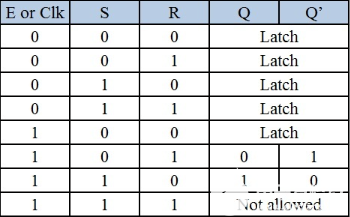

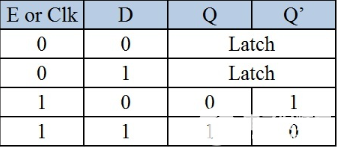

門控SR鎖存器的真值表如下圖所示:

D鎖存器

數據鎖存器或延遲鎖存器(D鎖存器)是存儲數據的簡單鎖存器之一,它也被稱為透明鎖存器。一個簡單的D鎖存器可以由兩個NAND門構成。

當S = R = 1時發生的SR鎖存器中的競態條件可以在D鎖存器中避免,因為R輸入被重命名為D的反轉S替換。因此沒有非法或禁止的輸入。在 D鎖存器中,Q始終為D。

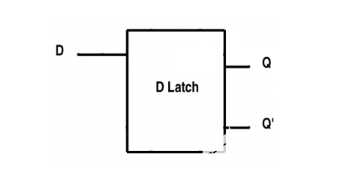

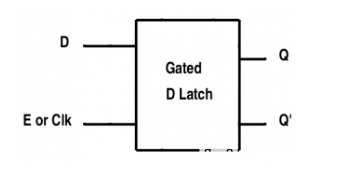

D鎖存器的符號如下所示:

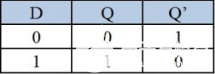

這些簡單的D鎖存器不常用,但門控D鎖存器很常見。簡單D鎖存器的真值表如下所示。

門控D鎖存器

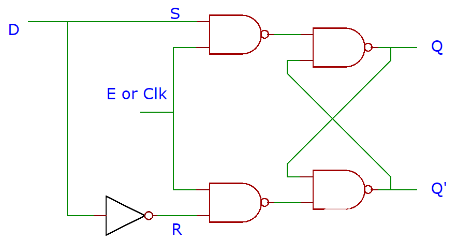

通過修改門控SR鎖存器可以輕松構建門控D鎖存器。對門控SR鎖存器的唯一修改是必須將R輸入更改為反相S。由NOR SR鎖存器形成的門控鎖存器如下所示。

當時鐘或使能為高電平(邏輯 1)時,輸出會鎖存D輸入上的任何內容。當使能或時鐘為低電平(邏輯 0)時,最后一個使能高電平的D輸入將是輸出。

這個鎖存電路永遠不會遇到“競爭”情況,因為單個D輸入被反轉以提供給兩個輸入。因此,沒有機會獲得相同的輸入條件。所以D鎖存電路可以安全地用于任何電路。

門控D鎖存器的符號如下所示:

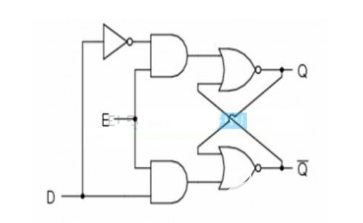

與門控NOR SR鎖存器類似,門控D鎖存器也可以由門控NAND SR鎖存器構成。門控NAND SR鎖存器的門控D鎖存器電路如下所示。

當然,可以避免使用反相器,因為可以使用與非門來獲得反相值。上述電路需要進行一些修改,得到的電路如下所示:

門控D鎖存器的真值表(或狀態表)如下所示:

鎖存器的應用

鎖存器的應用主要包括以下幾個方面:

它們是基本的1位存儲設備。

D鎖存器通常用作異步系統中的I/O端口。

數據鎖存器有時用于同步兩相系統中以減少晶體管數量。

鎖存器的優點

鎖存器的優點包括以下幾方面內容:

速度更快,因為它不需要等待時鐘信號,最常用于高速設計。

需要更少的電力。

基于鎖存器的設計具有小芯片尺寸。

主要優點是“借時”。其中,如果某項操作未在規定時間內完成,則從其他操作時間借用執行該操作所需的時間。

鎖存器的缺點

鎖存器的缺點包括以下幾方面內容:

鎖存器不太可預測,因為有更多機會影響競爭條件。

電平敏感設備,因此亞穩態的機會更大。

由于鎖存器電路的電平敏感特性,所以分析鎖存器電路很困難。

總結

簡單來說,鎖存器,就是數字電路中的一種具有記憶功能的邏輯元件,可以在特定輸入脈沖電平作用下改變狀態。

需要注意的是,鎖存器輸出端的狀態不會隨輸入端的狀態變化而變化,僅在有鎖存信號時輸入的狀態才被保存到輸出,直到下一個鎖存信號到來時才改變。

-

鎖存器

+關注

關注

8文章

923瀏覽量

42205 -

時序邏輯電路

+關注

關注

2文章

94瀏覽量

16801 -

SR

+關注

關注

1文章

38瀏覽量

23626

發布評論請先 登錄

評論