負(fù)載電容的計(jì)算方法:

在做電路設(shè)計(jì)的時(shí)候,很多工程師不知道晶振的負(fù)載電容改如何計(jì)算,在設(shè)計(jì)的時(shí)候,很多人都憑借的經(jīng)驗(yàn)加個(gè)20PF,或者22PF,18PF。

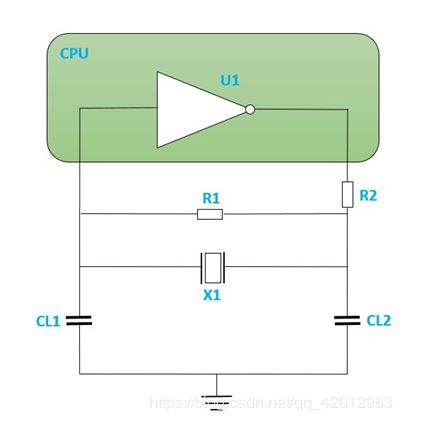

晶振的兩個(gè)引腳與芯片(如單片機(jī))內(nèi)部的反相器相連接,再結(jié)合外部的匹配電容CL1、CL2、R1、R2,組成一個(gè)皮爾斯振蕩器(Pierce oscillator)。如下圖所示:

上圖中,U1為增益很大的反相放大器,CL1、CL2為匹配電容,是電容三點(diǎn)式電路的分壓電容,接地點(diǎn)就是分壓點(diǎn)。以接地點(diǎn)即分壓點(diǎn)為參考點(diǎn),輸入和輸出是反相的,但從并聯(lián)諧振回路即石英晶體兩端來(lái)看,形成一個(gè)正反饋以保證電路持續(xù)振蕩,它們會(huì)稍微影響振蕩頻率,主要用與微調(diào)頻率和波形,并影響幅度。 X1是晶體,相當(dāng)于三點(diǎn)式里面的電感,R1是反饋電阻(一般≥1MΩ),它使反相器在振蕩初始時(shí)處于線性工作區(qū),R2與匹配電容組成網(wǎng)絡(luò),提供180度相移,同時(shí)起到限制振蕩幅度,防止反向器輸出對(duì)晶振過(guò)驅(qū)動(dòng)將其損壞。

這里涉及到晶振的一個(gè)非常重要的參數(shù),即負(fù)載電容CL(Load capacitance),它是電路中跨接晶體兩端的總的有效電容(不是晶振外接的匹配電容),主要影響負(fù)載諧振頻率和等效負(fù)載諧振電阻,與晶體一起決定振蕩器電路的工作頻率,通過(guò)調(diào)整負(fù)載電容,就可以將振蕩器的工作頻率微調(diào)到標(biāo)稱值。

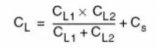

負(fù)載電容的公式如下所示:

C_L=C_S+(C_D×C_G)/(C_D+C_G )

其中,CS為晶體兩個(gè)管腳間的寄生電容(Shunt Capacitance)

CD表示晶體振蕩電路輸出管腳到地的總電容,包括PCB走線電容CPCB、芯片管腳寄生電容CO、外加匹配電容CL2,即CD=CPCB+CO+CL2

CG表示晶體振蕩電路輸入管腳到地的總電容,包括PCB走線電容CPCB、芯片管腳寄生電容CI、外加匹配電容CL1,即CG=CPCB+CI+CL1

一般CS為1pF左右,CI與CO一般為幾個(gè)皮法,具體可參考芯片或晶振的數(shù)據(jù)手冊(cè)

(這里假設(shè)CS=0.8pF,CI=CO=5pF,CPCB=4pF)。

比如規(guī)格書(shū)上的負(fù)載電容值為18pF,則有

則CD=CG=34.4pF,計(jì)算出來(lái)的匹配電容值CL1=CL2=25pF

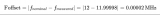

頻偏的計(jì)算方法

我們描述頻偏的時(shí)候一般是以ppm作為單位來(lái)描述的,ppm是百萬(wàn)分之一的意思也就是10^-6。假如我們有一個(gè)晶振,它的頻率標(biāo)值是12MHZ,但是我們測(cè)試到的是11.99998MHZ。那么Foffset=12-11.99998=0.00002MHZ。

ppm=(0.00002/12)*10^6=1.67。

一般在選中晶振的時(shí)候選中精度相對(duì)好點(diǎn)的。類似STM32這樣的芯片其實(shí)ppm<30的時(shí)候 基本可以接受。

審核編輯:湯梓紅

-

單片機(jī)

+關(guān)注

關(guān)注

6035文章

44554瀏覽量

634708 -

晶振

+關(guān)注

關(guān)注

34文章

2859瀏覽量

68007 -

負(fù)載電容

+關(guān)注

關(guān)注

0文章

138瀏覽量

10438

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何正確計(jì)算并使用晶振的外接負(fù)載電容

一點(diǎn)一點(diǎn)的了解晶振負(fù)載電容

晶振負(fù)載諧振頻率測(cè)量方法

晶振負(fù)載電容的重要性

請(qǐng)問(wèn)如何選擇AM4378晶振的負(fù)載電容和頻偏?選擇多少比較合適?

晶振負(fù)載電容外匹配電容計(jì)算與晶振振蕩電路設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

無(wú)源晶振(Crystal)的負(fù)載電容

MCU晶振匹配電容的計(jì)算

聊一聊頻偏和負(fù)載電容的計(jì)算方法

晶振的負(fù)載電容和頻偏的計(jì)算方法總結(jié)

晶振的負(fù)載電容和頻偏的計(jì)算方法總結(jié)

評(píng)論