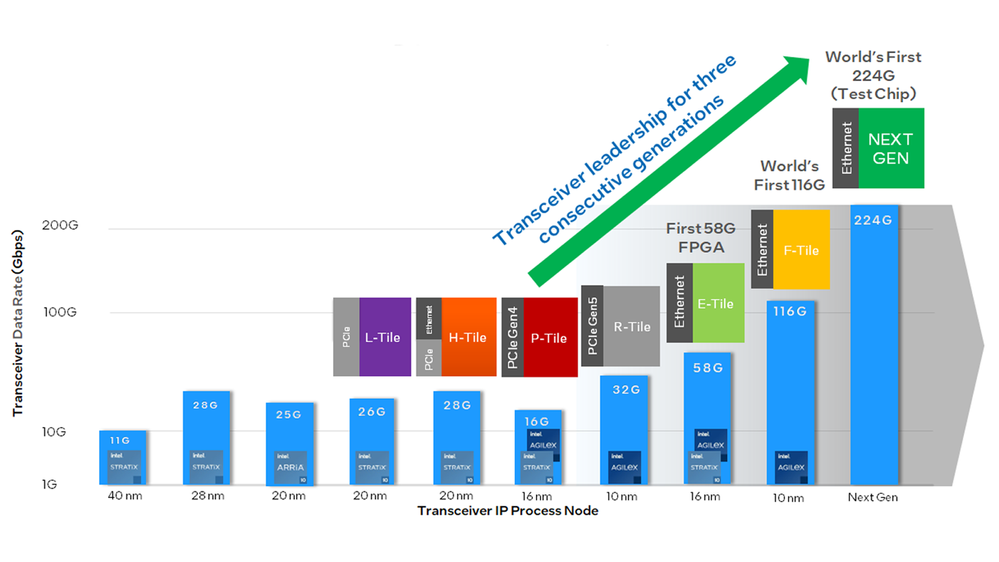

高速串行收發器在 20 多年前出現時便迅速成為一種基礎 FPGA 組件。隨著帶寬的爆發式增長,它們變得越來越重要。這些高速收發器設計足夠靈活、可配置性強,能夠直接實現多種標準數字串行通信協議,包括以太網、PCI Express (PCIe)、Compute Express Link (CXL)、串行數字接口 (SDI) 等。長期以來,英特爾在高速串行收發器的開發方面一直保持其先進性 (如圖 1 所示)。

圖1:英特爾 FPGA 收發器技術保持先進性

圖 1 顯示,由于采用了十分先進的英特爾 FPGA 制程工藝,高速收發器數據速率已從 40 nm 制程節點的 10 Gbps 提升到了 116 Gbps;同時,英特爾已展示了一款 224 Gbps 高速收發器測試芯片,這預示著 FPGA 收發器技術的發展方向。

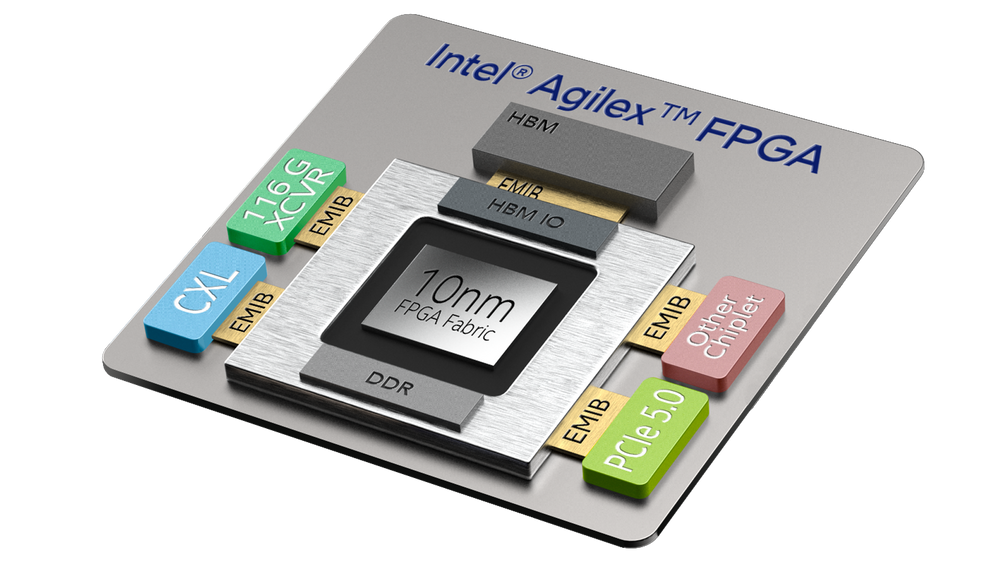

新近英特爾 FPGA 家族,包括英特爾 Agilex FPGA、英特爾 Stratix 10 FPGA 和 SoC FPGA 在內,都集成了單獨的、英特爾稱之為“Tile”的小芯片,用來實現高速收發器。這種基于 Tile 的 FPGA 構建方法為快速且經濟高效地開發具有許多功能的廣泛器件系列提供了極大的靈活性。

圖 2 顯示的是英特爾 Agilex FPGA 的內部結構。圖中五個小芯片圍繞著一個中央半導體芯片,芯片內含英特爾 Agilex FPGA 的可編程邏輯結構及其他邏輯電路,包括 DDR 和高帶寬內存 (HBM) 控制器。五個小芯片中有四個標記了“116G XCVR”、“CXL”、“PCIe 5.0”和“Other Chiplet”字樣,第五個標記為“HBM”的小芯片實際上是一個包含了數 GB HBM DRAM 的小芯片堆棧。

圖 2:英特爾 Agilex FPGA

盡管根據高速串行協議標記了不同的名稱,但“116G XCVR”、“CXL”和“PCIe 5.0”的要表達的意思相似。英特爾開發了這些小芯片,以提供高速串行收發器功能。每個 F-tile 收發器小芯片為 FPGA 增加了 20 條高速收發器通道。在每個 F-tile 上的 20 個高速收發器中,有四個 FHT 收發器 (每個收發器都能夠使用 PAM4 調制技術以快達 116 Gbps 的速度運行),有 12 個 FGT 收發器 (每個收發器都能夠使用 PAM4 調制技術以 58.125 Gbps的速度運行)。總的來說,這 20 個高速收發器可提供超過 700 Gbps 的數據帶寬。對于最多有四個 F-tile 的英特爾 Agilex I 系列和 M 系列 FPGA,高速串行總帶寬超過了 2.4 Tbps。

英特爾剛剛發布了一個 5 分鐘的視頻,展示了英特爾 Agilex FPGA 家族的高速數據傳輸功能,這些功能由 F-tile 的高速收發器提供支持。演示中使用的是英特爾 SuperLite IV IP,一種低開銷的串行流協議。SuperLite IV IP 利用了 F-tile 的 PHY 直連功能,該功能具有 PMA 直連模式,可繞過 F-tile 媒體訪問控制 (MAC) 和物理編碼子層 (PCS) 硬核 IP 模塊。在高速收發器中繞過這些元件可大大降低時延,因而使 SuperLite IV 協議成為芯片到芯片、板對板和背板應用的理想選擇。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603013 -

收發器

+關注

關注

10文章

3424瀏覽量

105961 -

英特爾

+關注

關注

61文章

9949瀏覽量

171694 -

通信協議

+關注

關注

28文章

879瀏覽量

40299

原文標題:解析丨傳輸速率可達 2.4 Tbps!英特爾? Agilex? FPGA 支持高效數據傳輸

文章出處:【微信號:英特爾FPGA,微信公眾號:英特爾FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

英特爾展示互連微縮技術突破性進展

英特爾推出全新英特爾銳炫B系列顯卡

英特爾是如何實現玻璃基板的?

英特爾攜手日企加碼先進封裝技術

英特爾CEO:AI時代英特爾動力不減

英特爾加大玻璃基板技術布局力度

BittWare提供基于英特爾Agilex? 7 FPGA最新加速板

英特爾旗下FPGA公司Altera正式亮相

英特爾成立全新獨立運營的FPGA公司Altera

新思科技與英特爾深化合作加速先進芯片設計

英特爾旗下Altera正式獨立運作,FPGA市場將迎來怎樣的巨變?

英特爾FPGA收發器技術保持先進性

英特爾FPGA收發器技術保持先進性

評論