數(shù)字硬件建模SystemVerilog-邏輯運(yùn)算符

經(jīng)過幾周的更新,SV核心部分用戶自定義類型和包內(nèi)容已更新完畢,接下來就是RTL表達(dá)式和運(yùn)算符。

邏輯運(yùn)算符

邏輯運(yùn)算符對(duì)其操作數(shù)求值,并返回一個(gè)值,該值指示求值結(jié)果是真還是假(true or false)。例如,運(yùn)算a && b測(cè)試a和b是否都為真,如果兩個(gè)操作數(shù)都為真,則運(yùn)算符返回真。否則,運(yùn)算符返回false。

邏輯運(yùn)算符返回值。SystemVerilog沒有內(nèi)置的true或false布爾值。相反,邏輯運(yùn)算符的返回使用邏輯值1’b1(一個(gè)一位寬的邏輯l)表示真,1’b0表示假。邏輯運(yùn)算符還可以返回1’bx,指示仿真無法確定實(shí)際邏輯門的評(píng)估結(jié)果是否為真或假的模糊條件。

判斷一個(gè)表達(dá)式是真是假。要確定操作數(shù)是真是假,SystemVerilog使用以下規(guī)則:

如果所有位均為0,則操作數(shù)為假

如果所有位均為1,則操作數(shù)為真

如果所有位均為X或Z,且沒有位為1,則操作數(shù)未知X

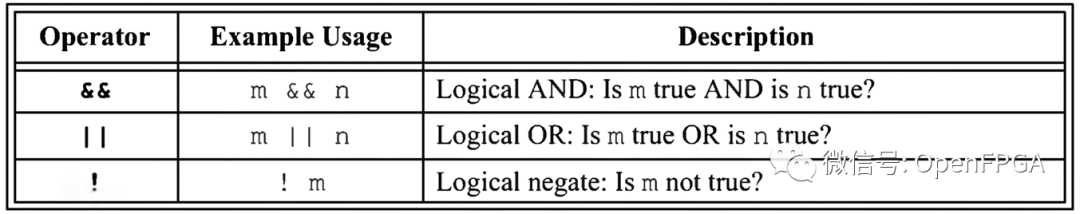

表5-1列出了RTL綜合編譯器普遍支持的邏輯運(yùn)算符。

表5-11:RTL建模的邏輯運(yùn)算符

邏輯求反運(yùn)算符通常被稱為“not運(yùn)算符”,它是“not true”的縮寫。

邏輯運(yùn)算符通過對(duì)每個(gè)操作數(shù)進(jìn)行歸約OR來執(zhí)行其運(yùn)算,從而產(chǎn)生一個(gè)1位結(jié)果。然后對(duì)該結(jié)果進(jìn)行求值,以確定其為真還是假。對(duì)于not運(yùn)算符,1位的結(jié)果首先被反轉(zhuǎn),然后求值為真或假。

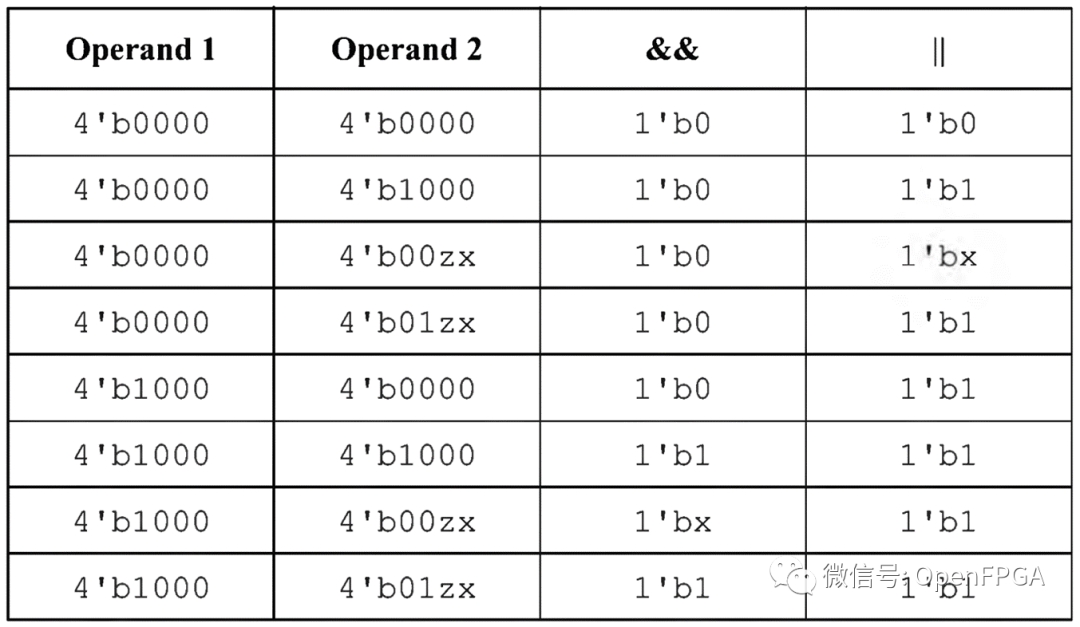

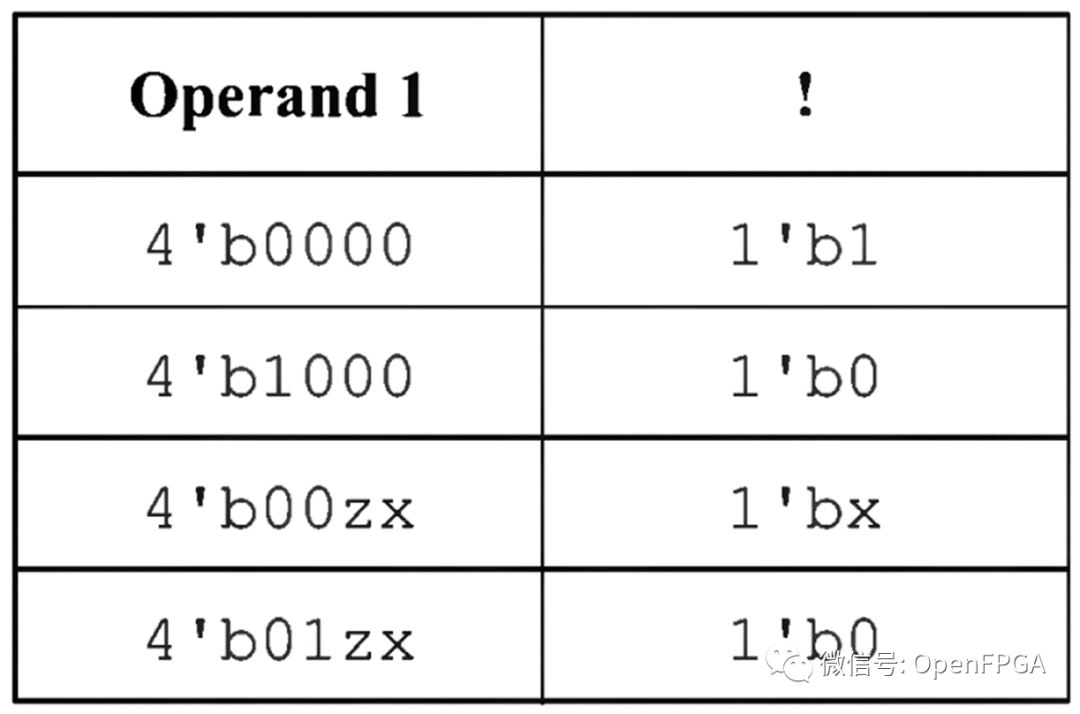

表5-12和5-13顯示了這些邏輯運(yùn)算符對(duì)幾個(gè)示例值的結(jié)果。

表5-12:邏輯AND and OR運(yùn)算的示例結(jié)果  表5-13:邏輯求反運(yùn)算的示例結(jié)果

表5-13:邏輯求反運(yùn)算的示例結(jié)果

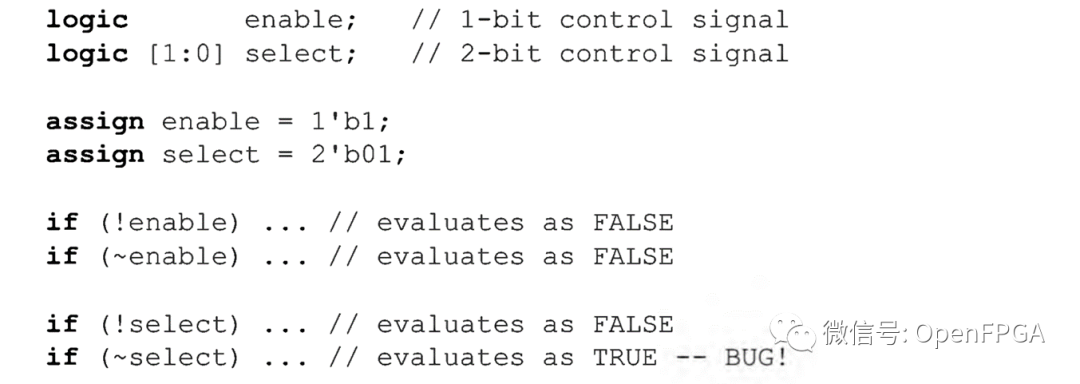

邏輯求反運(yùn)算符(!)和按位反轉(zhuǎn)運(yùn)算符(~)之間的區(qū)別

練習(xí)題目《HDLBits: 在線學(xué)習(xí) SystemVerilog(一)-Problem 2-6》Problem 4

應(yīng)注意不要混淆邏輯求反運(yùn)算符(!)以及按位反轉(zhuǎn)運(yùn)算符(~)。求反運(yùn)算符對(duì)其操作數(shù)執(zhí)行真/假求值,并返回表示真、假或未知結(jié)果的1位值。按位反轉(zhuǎn)運(yùn)算符對(duì)操作數(shù)的每一位(補(bǔ)碼)執(zhí)行邏輯反轉(zhuǎn),并返回與操作數(shù)相同位寬的值。

在某些操作中,這些操作的結(jié)果恰好相同,但在其他操作中,它們返回的值非常不同。當(dāng)運(yùn)算符與決策語(yǔ)句一起被錯(cuò)誤使用時(shí),這種差異可能導(dǎo)致錯(cuò)誤代碼。考慮下面的例子:

前面代碼片段的最后兩行之所以不同,是因?yàn)檫@兩個(gè)運(yùn)算符的工作方式不同——邏輯求反運(yùn)算符(!)通過將兩位相加或相減,對(duì)2位選擇執(zhí)行真/假計(jì)算,然后反轉(zhuǎn)1位結(jié)果,按位反轉(zhuǎn)運(yùn)算符(~)只反轉(zhuǎn)2位選擇向量的每一位的值,并返回2位結(jié)果。if語(yǔ)句然后對(duì)2位向量進(jìn)行真/假測(cè)試,該向量的計(jì)算結(jié)果為真,因?yàn)榉崔D(zhuǎn)后的值仍有一位設(shè)置為1。

| 最佳實(shí)踐指南5-1 |

|---|

| 使用按位反轉(zhuǎn)運(yùn)算符反轉(zhuǎn)值的位,不要使用按位反轉(zhuǎn)運(yùn)算符對(duì)邏輯求反運(yùn)算符求反。相反,使用邏輯求反運(yùn)算符來否定真/假測(cè)試的結(jié)果。不要使用邏輯求反運(yùn)算符反轉(zhuǎn)值。 |

| 最佳實(shí)踐指南5-2 |

|---|

| 僅使用邏輯求反運(yùn)算符求反來測(cè)試標(biāo)量(1位)值,而不是 對(duì)向量執(zhí)行真/假測(cè)試。 |

如果向量的任何位為1,邏輯運(yùn)算將返回true,這可能會(huì)導(dǎo)致在測(cè)試特定位時(shí)出現(xiàn)設(shè)計(jì)錯(cuò)誤。計(jì)算向量值時(shí),使用等式或關(guān)系運(yùn)算符測(cè)試可接受的值。

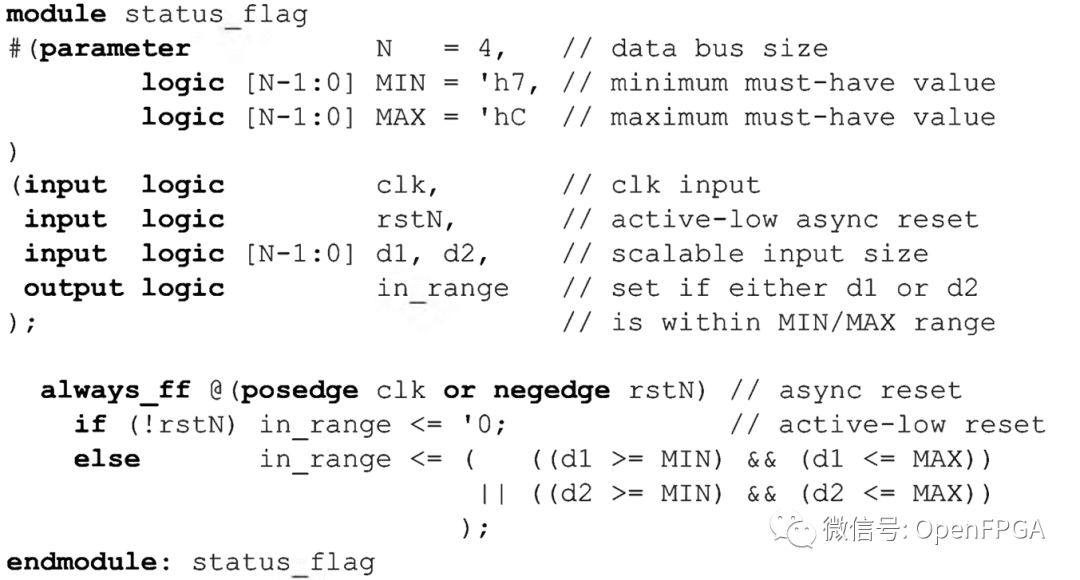

示例5-7說明了一個(gè)小型RTL模型,該模型使用邏輯NOT、邏輯AND和邏輯OR運(yùn)算符。該設(shè)計(jì)是一個(gè)邏輯比較器,如果兩個(gè)數(shù)據(jù)值中的任何一個(gè)在可配置的值范圍內(nèi),則設(shè)置一個(gè)flag。

示例5-7:使用邏輯運(yùn)算符:當(dāng)值在某個(gè)范圍內(nèi)時(shí)設(shè)置flag

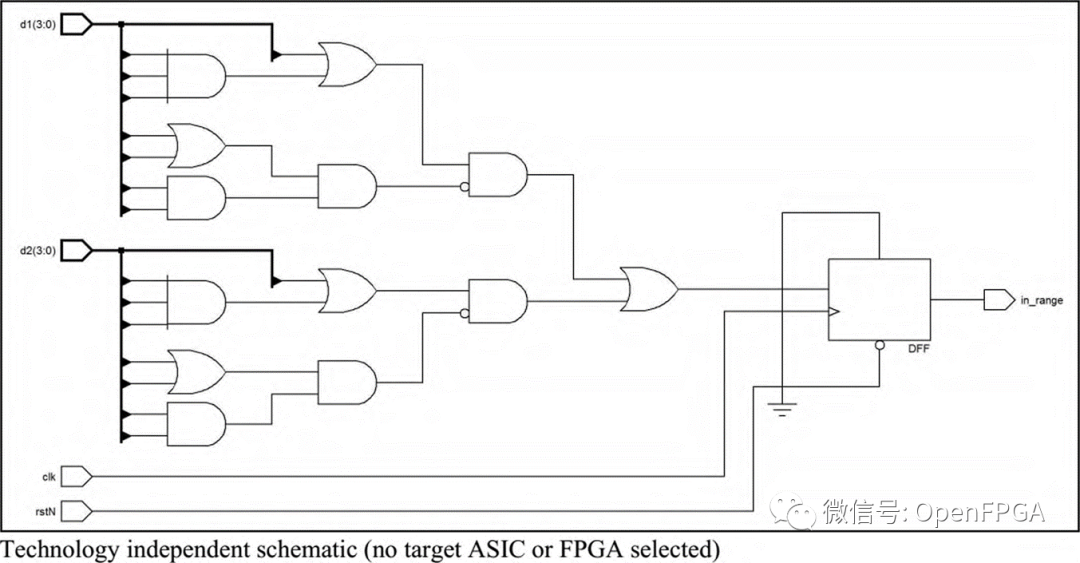

圖5-7顯示了示例5-7中的RTL模型綜合結(jié)果

圖5-7:示例5-7的綜合結(jié)果:邏輯運(yùn)算符(范圍內(nèi)比較)

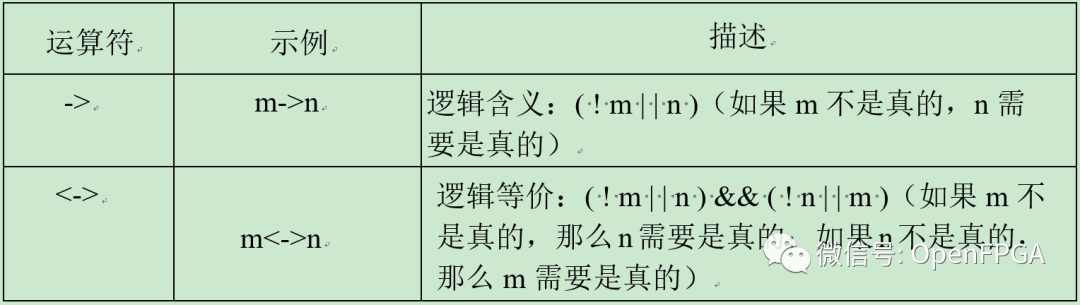

不可綜合的邏輯運(yùn)算符

SV-2009增加了兩個(gè)額外的邏輯運(yùn)算符,它們是蘊(yùn)涵和等價(jià)運(yùn)算符,在本文編寫時(shí)RTL綜合編譯器通常不支持這些運(yùn)算符。表5-14列出了這兩個(gè)運(yùn)算符的標(biāo)記和描述。

表5-14:不可綜合邏輯運(yùn)算符

-

硬件

+關(guān)注

關(guān)注

11文章

3417瀏覽量

66694 -

RTL

+關(guān)注

關(guān)注

1文章

386瀏覽量

60172 -

編譯器

+關(guān)注

關(guān)注

1文章

1645瀏覽量

49465

原文標(biāo)題:SystemVerilog-邏輯運(yùn)算符

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何在SystemVerilog中為狀態(tài)機(jī)的命令序列的生成建模

數(shù)字硬件建模SystemVerilog-歸約運(yùn)算符

SystemVerilog對(duì)硬件功能如何進(jìn)行建模

數(shù)字硬件建模SystemVerilog-網(wǎng)絡(luò)

數(shù)字硬件建模SystemVerilog-結(jié)構(gòu)體

關(guān)于數(shù)字硬件建模SystemVerilog聯(lián)合體

IEEE SystemVerilog標(biāo)準(zhǔn):統(tǒng)一的硬件設(shè)計(jì)規(guī)范和驗(yàn)證語(yǔ)言

使用Verilog/SystemVerilog硬件描述語(yǔ)言練習(xí)數(shù)字硬件設(shè)計(jì)

數(shù)字硬件建模SystemVerilog-組合邏輯建模(1)連續(xù)賦值語(yǔ)句

FPGA學(xué)習(xí)-SystemVerilog語(yǔ)言簡(jiǎn)介

RTL和門級(jí)建模

數(shù)字硬件建模SystemVerilog之Interface方法概述

數(shù)字硬件建模SystemVerilog之Interface和modport介紹

SystemVerilog的覆蓋率建模方式

SystemVerilog在硬件設(shè)計(jì)部分有哪些優(yōu)勢(shì)

關(guān)于數(shù)字硬件建模SystemVerilog

關(guān)于數(shù)字硬件建模SystemVerilog

評(píng)論