復位概述

復位作為電子系統中最常見的信號同時也是最重要的信號,它對工程師整體的設計表現有著極大的影響。復位信號可能深刻影響設計的性能表現,功耗,面積等等。對于一個優秀的系統設計,很難不把復位信號當成一個關鍵信號來設計。

同步的代碼可能會綜合出LUTs,Registers,SRLs,Block or LUT memory,DSP48 registers。對復位方式的不同選擇以及對復位的使用不同會影響基本元件的選擇。可能會引入更多或者更少的資源,影響整體設計的表現,功耗,甚至會導致系統運行異常。

什么時候什么地方使用復位?

對于很多新入門工程師來講,很少會評估是否需要復位信號,絕大所數都是使用提供的模板,對所有的信號進行復位,盡管可能不是那么必要,如果是這樣會增加資源,對復位時序也會產生影響,所以評估是否需要復位是很有必要的。

對賽靈思器件而言,廠家對FPGA提供了專用的全局復位(GSR)。這個信號在配置結束會把所有的時序元件都設置為一個初始的值。如果這個初始值沒有被指定,大多數情況下都會被設置為0。每個器件都會在配置結束設置為一個定值,因此,有些上電時單一目的復位必要性不是很大。下面代碼初始化registers和latches的指定初始值。

// Verilog代碼

reg register1 = 1’b0; // specifying regsiter1 to start as a zero

reg register2 = 1’b1; // specifying register2 to start as a one

reg [3:0] register3 = 4’b1011; //specifying INIT value for 4-bit register

-- VHDL代碼

signal reg1 : std_logic := '0'; -- specifying register1 to start as a zero

signal reg2 : std_logic := ‘1’; -- specifying register2 to start as a one

signal reg3 : std_logic_vector(3 downto 0):="1011"; -- specifying INIT value for 4-bit register

所以像之前所訴述,工程師應該仔細考慮和評估什么時候,什么地方需要復位。因為不必要的復位可能會導致諸多的問題。限制復位的使用可能具備的優勢:

-

限制全局復位網絡的扇出

-

減少復位路徑的互聯

-

簡化復位路徑的時序分析

-

提升整體設計的性能表現,面積,功耗等

功能性的仿真是可以容易區分復位是否需要,所以建議去評估每一個同步模塊是否需要復位,盡量減少在未評估真實需要復位的情況下就引入復位。

同步復位異步復位

同步復位就是復位信號在時鐘觸發邊沿才有效,簡單講敏感列表中沒有復位信號,異步復位在復位信號被置位后即有效,簡單說敏感列表中存在復位信號。如下面兩段Verilog代碼:

// 同步復位

module sync_resetFFstyle (

output reg q,

input d, clk, rst_n);

always @(posedge clk)

if (!rst_n)

q <= 1'b0;

else

q <= d;

endmodule

// 異步復位

module async_resetFFstyle (

output reg q,

input d, clk, rst_n);

always @(posedge clk or negedge rst_n)

if (!rst_n)

q <= 1'b0;

else

q <= d;

endmodule

同步復位相比較異步復位有以下的特點:

-

同步復位可以映射更多種類的資源單元

-

全局的異步復位會增加設計元件的布線復雜度(每個register都要連接復位信號)

-

如果需要提高電路的集成密度或者對電路進行調優布局,同步復位更加靈活

-

有些資源僅提供提供同步復位,如DSP48和RAM模塊,如果使用異步復位,很難在不影響模塊功能的前提下將異步信號正確施加在這些模塊。(Xilinx)

同步復位特點:

-

電路是百分之百同步化的

-

時鐘可以充當同步復位信號的一個毛刺濾波,但如果毛刺發生在時鐘觸發邊沿,flip-flop仍然可能出現亞穩態。

-

同步復位可能需要一個計數器來保障復位信號的寬度足夠寬來實現有效的復位。

-

因為同步復位需要時鐘來復位,有些極少數的情況下,如某些低功耗設計,時鐘可能在復位前就被無效,那么同步復位也無效,這里可能只有異步復位有效。

異步復位優點

只要具有可復位的觸發器,那么異步復位就可以生效

異步復位不會在數據路徑引入其他邏輯

異步復位缺點

反斷言階段,即復位移除階段,復位信號沿如果距離時鐘觸發沿很近,則可能發生亞穩態,那么復位狀態可能會丟失,也就是常說的符合Recovery Time以及Removal Time(類似Setup Time和Hold Time)

板子的毛刺和噪聲可能引起虛假復位。

其他的一些缺點已經在(同步復位相比較異步復位有以下特點)上面小節闡述。

注意:異步復位都應該同步釋放,以處理可能出現的亞穩態和異常情況,如下面所示代碼:

// 異步復位同步釋放

module sync_reset #

(

// depth of synchronizer

parameter N = 2

)

(

input wire clk,

input wire rst,

output wire out

);

(* srl_style = "register" *)

reg [N-1:0] sync_reg = {N{1'b1}};

assign out = sync_reg[N-1];

always @(posedge clk or posedge rst) begin

if (rst) begin

sync_reg <= {N{1'b1}};

end else begin

sync_reg <= {sync_reg[N-2:0], 1'b0};

end

end

endmodule

// 代碼來自開源項目AlexForencich

如何去除不必要復位信號?

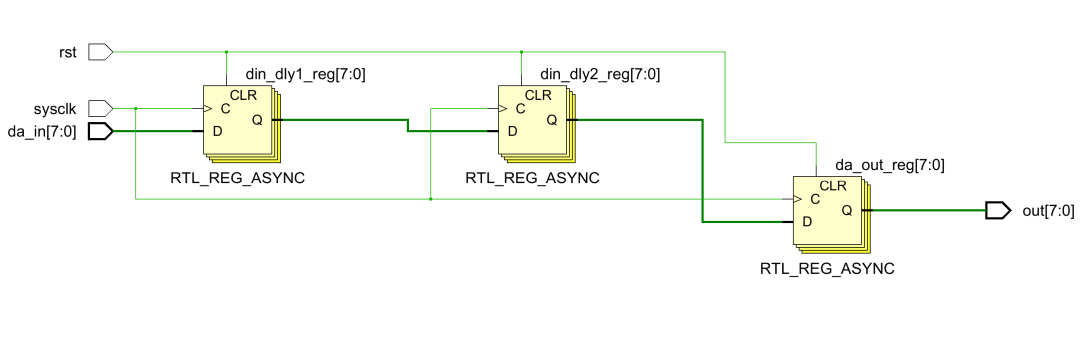

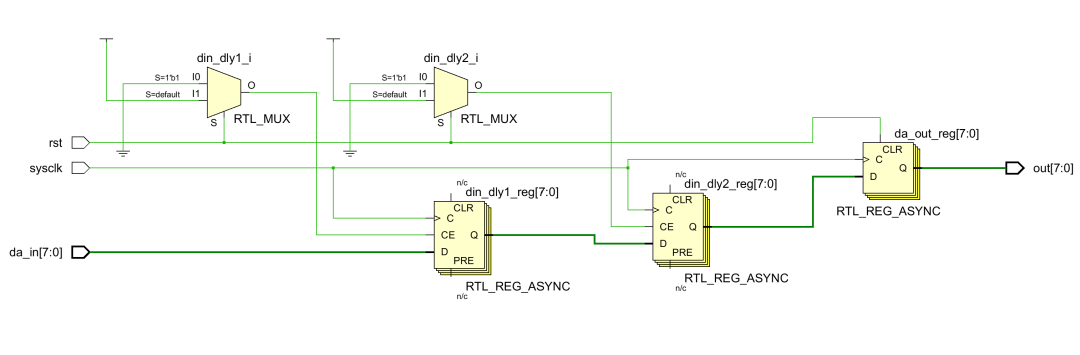

當需要去除一些復位信號時,直接注釋掉相關的代碼是不合適并且會引入非預期的結構以及會導致異常問題。如下面的代碼,注釋掉復位代碼塊里的din_dly1和din_dly2會讓復位信號成為寄存器的使能信號,顯然屬于引入無關邏輯,可能會引起設計的問題。如圖一為未注釋代碼前綜合出的異步復位電路,圖二為直接注釋掉復位區域信號的代碼。產生這種問題也很容易理解,代碼邏輯就是非復位狀態din_dly1和din_dly2才能工作。

always@(posedge sysclk or posedge rst)

begin

if(rst)

begin

// din_dly1 <= 8'b0;

// din_dly2 <= 8'b0;

da_out <= 8'b0;

end

else

begin

din_dly1 <= da_in;

din_dly2 <= din_dly1;

da_out <= din_dly2;

end

end

圖一:未注釋掉復位信號的代碼

圖二:注釋掉復位信號的代碼(引入非期望的電路)

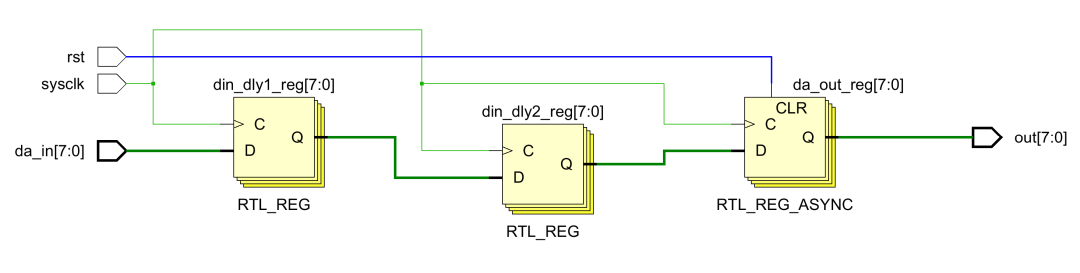

當遇到需要去除一些寄存器的復位信號時,記住一個基本原則:一個時序模塊不可以混合不同復位類型的寄存器,簡單講就是不能出現不復位的寄存器和復位的寄存器,只要使用復位信號,那么時序模塊的寄存器都應該復位。那么需要去除一些寄存器的復位信號應該怎么辦?同樣功能的代碼如下,將復位的寄存器放入一個always塊中,不需要復位的寄存器放入另一個always塊中。圖三是實際綜合出的電路也是實際期望的電路,沒有引入其他邏輯。

always @(posedge sysclk) begin

din_dly1 <= da_in;

din_dly2 <= din_dly1;

end

always @(posedge sysclk or posedge rst) begin

if(rst)

da_out <= 8'b0;

else

da_out <= din_dly2;

end

圖三:不同復位類型區分綜合出的電路

總結:本篇文章主要總結復位類型和其優缺點,在不同的情形下對復位類型選擇進行權衡,尤其要評估一些不需要復位的情況,以實現設計的更優性能表現。具體的內容還可以查閱參考文獻所列內容。

審核編輯 :李倩

-

FPGA

+關注

關注

1646文章

22073瀏覽量

619923 -

復位

+關注

關注

0文章

179瀏覽量

24722 -

異步復位

+關注

關注

0文章

47瀏覽量

13523

原文標題:FPGA復位信號設計討論

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DLPC6401什么時候可以只用Nand Flash或者EEPROM單獨對DLP進行配置?

ADS1204 CLKSEL置1時,如何采集數據?怎么知道什么時候是最高位?什么時候是最低位?

ADS1115的Config Register在什么時候配置比較好?

請問AFE4400讀取的數據什么時候才會出現0?

FPGA復位的8種技巧

復位電路的設計問題

評論