編者注:前段時間在和一個客戶交流時,硬件工程師現場拿出來一個案例,說他們做的一個項目使用的PCB材料比友商的還好,但是誤碼率卻比友商的產品高。拿他們的產品看了之后,去他們實驗室測試了下,大概知道了他們的問題點是什么。本文就把一個當天類似的案例分享給大家。

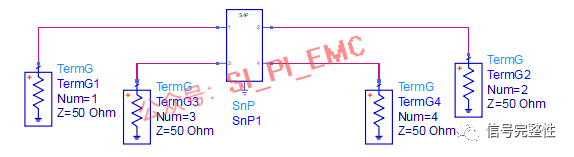

首先,我們在ADS用兩個不同的S參數建立原理圖進行仿真其S參數,如下圖所示:

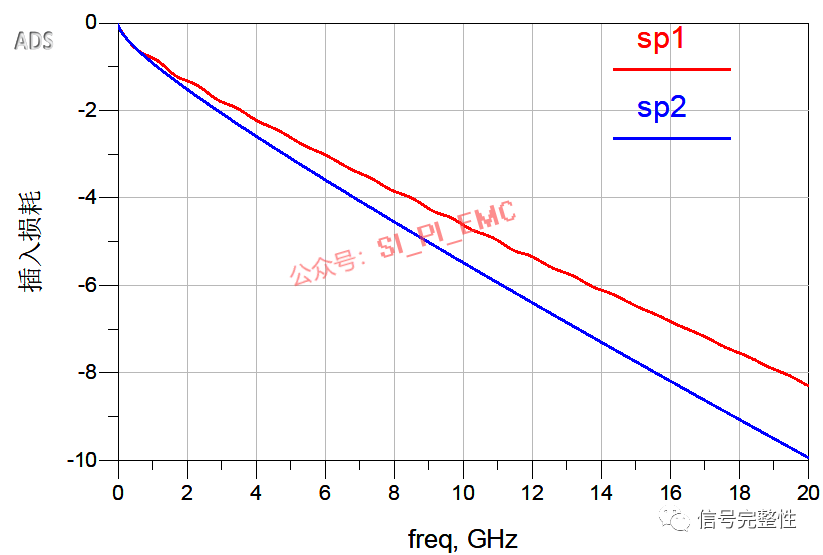

運行仿真后,查看其插入損耗如下圖所示(紅色為sp1,藍色為sp2):

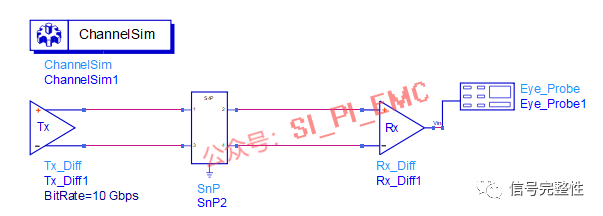

從仿真的結果可以看出sp2的損耗比sp1的損耗大(絕對值)。其次,我們在ADS中再建立一個時域仿真電路,如下圖所示:

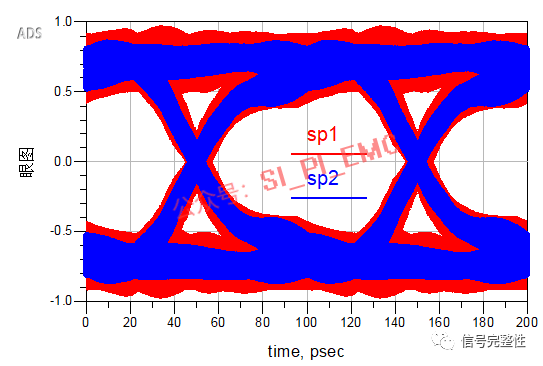

獲得的仿真結果-眼圖如下圖所示:

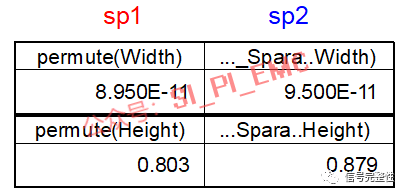

我們把眼圖的眼高和眼寬分別列舉出來,如下圖所示:

我們從上面的結果可以看到,雖然在頻域上的插入損耗sp1小于sp2,但是在時域上的眼圖卻得到了相反的結果,這與我們傳統的觀點并不一樣。

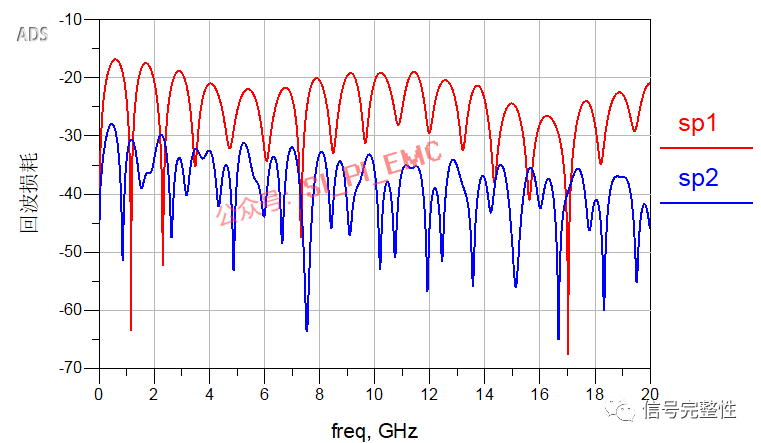

其實,往回想想,我們在這時只看到了插入損耗,這只是頻域上一個參數,我們再看看其回波損耗,如下圖所示:

顯然,sp1的回波損耗更差,與sp2相差大概10dB。這樣就會導致信號傳輸的時候發生一定程度的反射。最后,我們發現其阻抗確實差別比較大。

至此,可以看到了,插入損耗大,眼圖不一定小。通過本文的案例,我們可以看到,在設計高速產品的時候,不要把所有的精力都放在如何減小損耗上,還需要考慮如何優化產品的互連通道。

審核編輯:湯梓紅

-

pcb

+關注

關注

4319文章

23111瀏覽量

398243 -

眼圖

+關注

關注

1文章

67瀏覽量

21152 -

S參數

+關注

關注

2文章

141瀏覽量

46554

原文標題:【案例】插入損耗大,眼圖就一定小嗎?

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB材料測試案例

PCB材料測試案例

評論