·亞穩態問題是數字電路中很重要的問題,因為現實世界是一個異步的世界,所以亞穩態是無法避免的,并且亞穩態應該也是面試常考的考點。

·時序電路將觸發器和鎖存器當作存儲元件,但是這兩種器件都受制于一個稱為亞穩定性的狀態。

亞穩態的原因:

如果鎖存器的一個輸入脈沖太窄,或兩個輸入同時有效,或兩個輸入間隔過小,那么鎖存器可能進入亞穩態。

而如果數據在使能輸入沿的周圍不穩定,DFF也會進入亞穩態。(這個不穩定就是在Tsu和Th內信號不穩定,或者是復位)

何時會發生亞穩態:

因為存儲器件很容易進入亞穩態,所以設計時應該考慮使由于亞穩態導致的系統混亂的信號影響最小。

許多想要以同步方式執行的物理系統都具有異步輸入信號,而異步信號時間不可控,所以極易出現亞穩態的情況。

·那么何為異步信號?

·異步信號就是不能由時鐘控制,或者如果它是由不同域中的時鐘同步的。

亞穩態危害:

因為亞穩態時不確定是0還是1,所以信號會在0,1之間震蕩,就會邏輯混亂。而在復位電路中產生亞穩態會使復位失敗。

一般同步信號下不會出現亞穩態,亞穩態一般出現在異步信號和跨時鐘域的情況下。

1) 在跨時鐘域的情況下,由于兩端的時鐘相移未知,所以在源寄存器發出的信號可能在任何情況下到目標寄存器,無法確定滿足Tsu和Th的要求。

2) 異步信號的輸入也是同理,不確定信號在什么時候到達。

異步復位的亞穩態

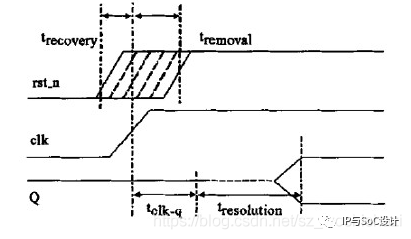

恢復時間(T recovery):

指的的異步信號發生時離下一個clk之間的最短時間,如果異步信號的有效沿在恢復時間內就沒有留給寄存器足夠的時間去恢復正常,就會出現亞穩態。

去除時間(T removal):

指的是當前clk過去變無效的時間,如果異步信號發生在去除時間內,就會無法屏蔽這個clk,可能這個時鐘仍會起作用,沒有達到復位的效果,這也是亞穩態。

·這些情況都指的是異步信號能夠直接改變寄存器的情況。

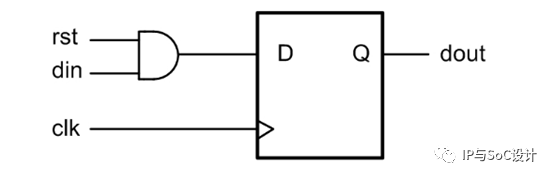

同步復位的亞穩態

大部分資料表明同步復位電路不會發生亞穩態,其實同步電路也會發生,只是幾率小于異步電路。

例如這個電路,din為1時,如果rst無效沿在Tsu和Th內,依舊會產生亞穩態的情況。

所以說有異步信號的電路都有亞穩態發生的機率。

亞穩態發生概率

·亞穩態發生情況都是同步信號不滿足set-time,hold-time或者異步信號不滿足恢復和移除時間。

·概率=(set-time + hold-time)/周期

可以看出隨著頻率變高,亞穩態的概率會隨之變大。

所以可以通過減小頻率,或者使用更好工藝的FPGA來減小Ts和Th。

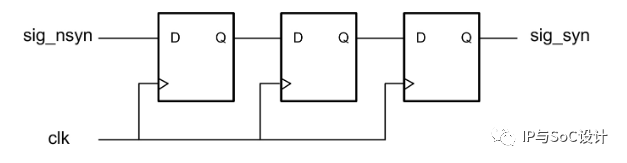

因為實驗表明帶異步輸入的電路故障修復的平均時間與退出亞穩態條件所用的時間成指數關系,所以依靠同步裝置創建一個用于從亞穩態條件恢復到正常的緩沖器,可以大大減少電路故障可能性。

一直看到資料說一級寄存器產生亞穩態后,兩級就90%沒有亞穩態,三級就99%沒有,一直沒搞懂為什么,現在仔細梳理一下。

因為第一級產生亞穩態后,通過Tmet(決斷時間)后會穩定成一個值,但是也有可能Tmet過長,產生第二級的亞穩態。

亞穩態振蕩時間Tmet

亞穩態震蕩時間Tmet關系到后級寄存器的采集穩定問題,Tmet影響因素包括:器件的生產工藝、溫度、環境以及寄存器采集到亞穩態離穩定態的時刻等。甚至某些特定條件,如干擾、輻射等都會造成Tmet增長。

常用的消除亞穩態的三種辦法

1) 對異步信號進行同步處理

2) 采用FIFO對跨時鐘域數據通信進行緩沖處理

3) 對復位電路采用異步復位,同步釋放處理

-

存儲器

+關注

關注

38文章

7643瀏覽量

166806 -

數字電路

+關注

關注

193文章

1638瀏覽量

81733 -

亞穩態

+關注

關注

0文章

47瀏覽量

13500

原文標題:數字電路的亞穩態問題

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA中亞穩態——讓你無處可逃

FPGA中亞穩態——讓你無處可逃

FPGA觸發器的亞穩態認識

亞穩態問題解析

FPGA--中復位電路產生亞穩態的原因

今日說“法”:讓FPGA設計中的亞穩態“無處可逃”

亞穩態的原理、起因、危害、解決辦法及影響和消除仿真詳解

簡述FPGA中亞穩態的產生機理及其消除方法

評論