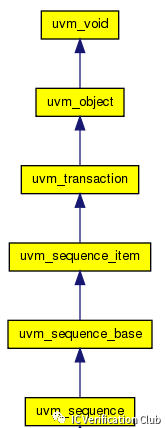

Q:激勵最初產(chǎn)生在driver中,后來產(chǎn)生在sequence中。為什么會有這個過程呢?

Q:當(dāng)一個激勵在driver中產(chǎn)生,當(dāng)要對DUT施加不同的激勵時,那應(yīng)該怎么辦呢?

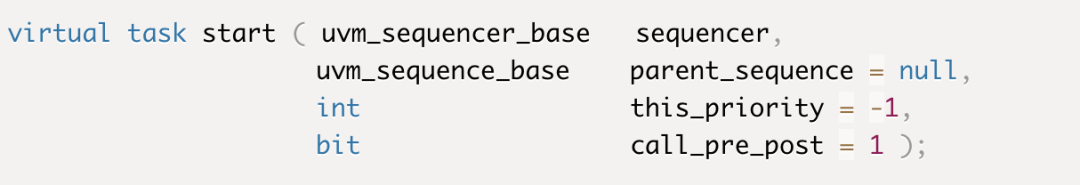

Q:如何在定義后啟動一個sequence

//當(dāng)完成一個sequence的定義后,可以使用start任務(wù)將其啟動my_sequence my_seq;my_seq = my_sequence::create("my_seq");my_seq.start(sequencer);//除了直接啟動之外,還可以使用default_sequence啟動uvm_config_db#(uvm_object_wrapper)::set(this,"env.i_agt.sqr.main_phase","default_sequence",case0_sequence::get());

A:使用sequence機制之后,在不同的測試用例中,將不同的sequence設(shè)置成sequencer的main_phase的default_sequence。當(dāng)sequencer執(zhí)行到main_phase時,發(fā)現(xiàn)有default_sequence,那么它就啟動sequence。

A:當(dāng)一個sequence啟動后會自動執(zhí)行sequence的body任務(wù)。其實,除了body外,還會自動調(diào)用sequence的pre_body與post_body

文件:src/my_case0.sv3class case0_sequence extends uvm_sequence #(my_transaction);…virtual task pre_body();`uvm_info("sequence0", "pre_body is called!!!", UVM_LOW)endtaskvirtual task post_body();`uvm_info("sequence0", "post_body is called!!!", UVM_LOW)endtaskvirtual task body();…#100;`uvm_info("sequence0", "body is called!!!", UVM_LOW)…endtask`uvm_object_utils(case0_sequence)endclass

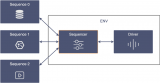

Q:UVM支持同一時刻在同一sequencer上啟動多個sequence,那同時啟動多個sequence時,哪個先執(zhí)行呢?

Q:sequencer根據(jù)什么選擇使用哪個sequence的transaction呢?這是UVM的sequence機制中的仲裁問題

//例如如下啟動了seq0和seq1文件:src/no_pri/my_case0.svtask my_case0::main_phase(uvm_phase phase);sequence0 seq0;sequence1 seq1;seq0 = new("seq0");seq0.starting_phase = phase;seq1 = new("seq1");seq1.starting_phase = phase;forkseq0.start(env.i_agt.sqr);seq1.start(env.i_agt.sqr);joinendtask

A:對于transaction來說,存在優(yōu)先級的概念,通常來說,優(yōu)先級越高越容易被選中。當(dāng)使用uvm_do或者uvm_do_with宏時,產(chǎn)生的transaction的優(yōu)先級是默認(rèn)的優(yōu)先級,即-1。可以通過uvm_do_pri及uvm_do_pri_with改變所產(chǎn)生的transaction的優(yōu)先級

文件:src/item_pri/my_case0.sv3class sequence0 extends uvm_sequence #(my_transaction);…virtual task body();…repeat (5) begin`uvm_do_pri(m_trans, 100)`uvm_info("sequence0", "send one transaction", UVM_MEDIUM)end#100;…endtask…endclassclass sequence1 extends uvm_sequence #(my_transaction);…virtual task body();…repeat (5) begin`uvm_do_pri_with(m_trans, 200, {m_trans.pload.size < 500;})`uvm_info("sequence1", "send one transaction", UVM_MEDIUM)end…endtask…endclass

uvm_do_pri與uvm_do_pri_with的第二個參數(shù)是優(yōu)先級,這個數(shù)值必須是一個大于等于-1的整數(shù)。數(shù)字越大,優(yōu)先級越高。

A:除transaction有優(yōu)先級外,sequence也有優(yōu)先級的概念

文件:src/sequence_pri/my_case0.svtask my_case0::main_phase(uvm_phase phase);…env.i_agt.sqr.set_arbitration(SEQ_ARB_STRICT_FIFO);forkseq0.start(env.i_agt.sqr, null, 100);seq1.start(env.i_agt.sqr, null, 200);joinendtask

-

driver

+關(guān)注

關(guān)注

0文章

526瀏覽量

66605 -

UVM

+關(guān)注

關(guān)注

0文章

182瀏覽量

19167 -

sequence

+關(guān)注

關(guān)注

0文章

23瀏覽量

2840

原文標(biāo)題:UVM之sequence機制

文章出處:【微信號:FPGA學(xué)姐,微信公眾號:FPGA學(xué)姐】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何在主從設(shè)備之間創(chuàng)建一個自定義的API調(diào)用?

UVM sequence分層有哪幾種方式呢

UVM sequence分層的幾種體現(xiàn)

如何在SpinalHDL里啟動一個仿真

如何配置sequence的仲裁算法和優(yōu)先級及中斷sequence的執(zhí)行

sequence item實際應(yīng)用中應(yīng)該包含哪些東西

如何在啟動文件中調(diào)用定義為uint32_t getValue(void)的C函數(shù)呢?

UVM中seq.start()和default_sequence執(zhí)行順序

淺談UVM之sequence/item見解(上)

start()如何執(zhí)行uvm_sequence

如何配置sequence的仲裁算法和優(yōu)先級?

在Sequencer上啟動一個Sequence

UVM設(shè)計中的sequence啟動方式有哪幾種呢?

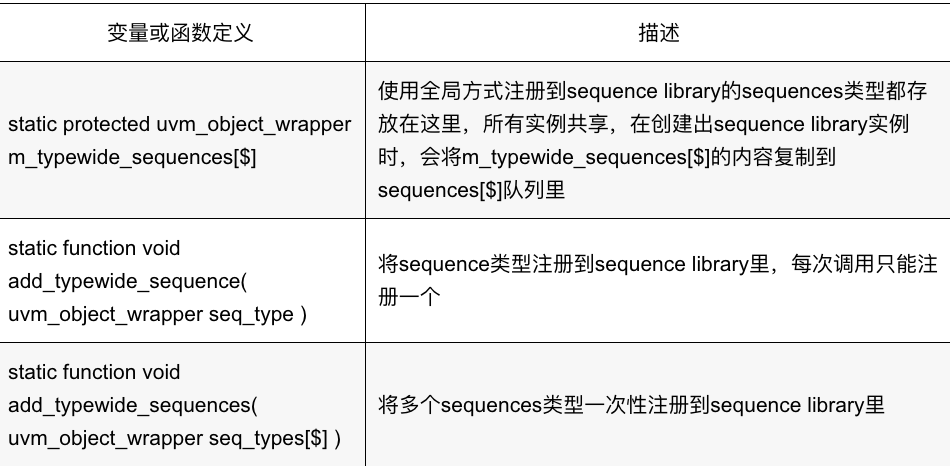

如何將sequences類型添加或注冊到sequence library里呢?

如何在定義后啟動一個sequence

如何在定義后啟動一個sequence

評論