4.CCIX傳輸層

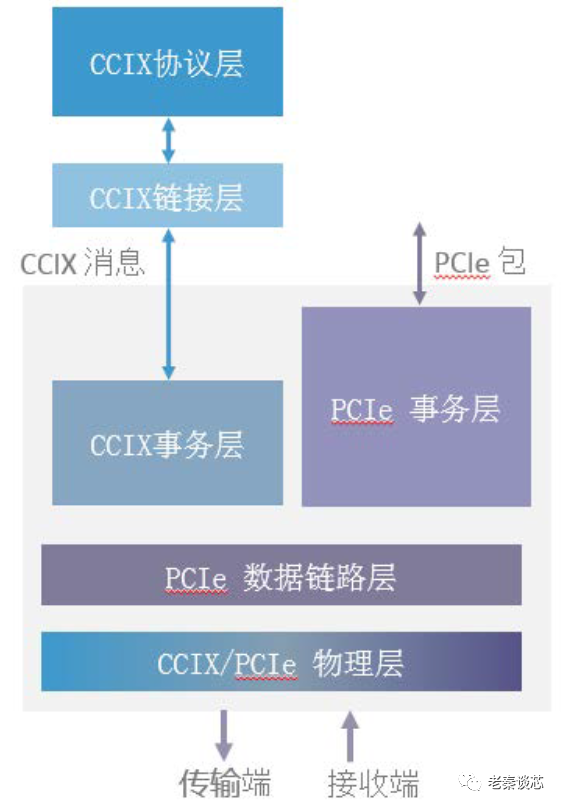

開篇中提過,CCIX可以看作兩個(gè)主要規(guī)范,分別是CCIX協(xié)議規(guī)范和CCIX傳輸規(guī)范。

CCIX 協(xié)議規(guī)范包含CCIX 協(xié)議層和CCIX鏈接層。這些層規(guī)定緩存一致性協(xié)議、報(bào)文發(fā)送、流控和CCIX 傳輸部分的協(xié)議。這正是第三章中的內(nèi)容。

CCIX 傳輸規(guī)范包含CCIX 和PCIe事務(wù)層,PCIe 數(shù)據(jù)鏈路層,和CCIX 物理層。這些層負(fù)責(zé)器件間的物理連接,包括速率和帶寬協(xié)商,傳輸包錯(cuò)誤檢測(cè)和重試,和初始包編碼協(xié)議。這是第四章的主要內(nèi)容。

開始學(xué)習(xí)這章之前,再來復(fù)習(xí)一下CCIX的分層架構(gòu)。

從圖中可以看出,在CCIX傳輸規(guī)范中,除了添加了CCIX事務(wù)層,作為對(duì)PCIe事務(wù)層的擴(kuò)展或者替換,而其它各層均遵循復(fù)用PCIe標(biāo)準(zhǔn)。按慣例,我們重點(diǎn)看看CCIX事務(wù)層,其它部分略過。

4.1 介紹

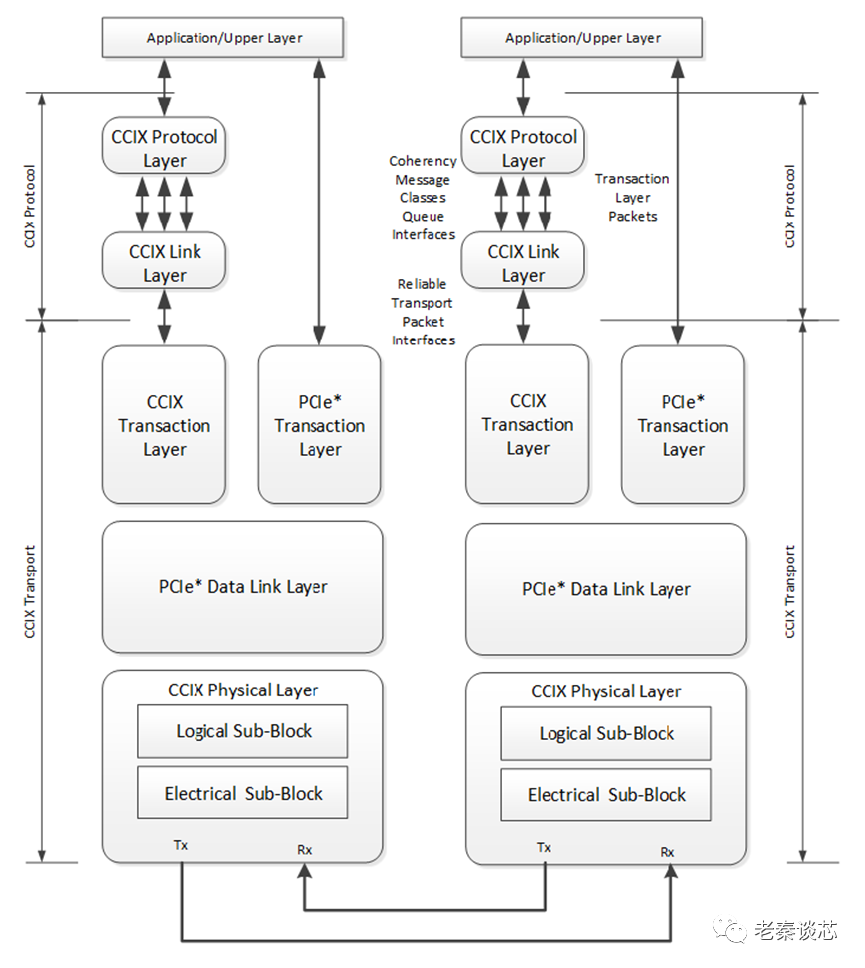

CCIX規(guī)范中使用數(shù)據(jù)包在CCIX鏈路層(CCIX Link Layer)和CCIX事務(wù)層(CCIX Transaction Layer)之間傳遞信息。

CCIX傳輸層(Transport Layer)分為兩個(gè)部分:一個(gè)處理出站(Outbound)信息,另一個(gè)處理入站(Inbound)信息。

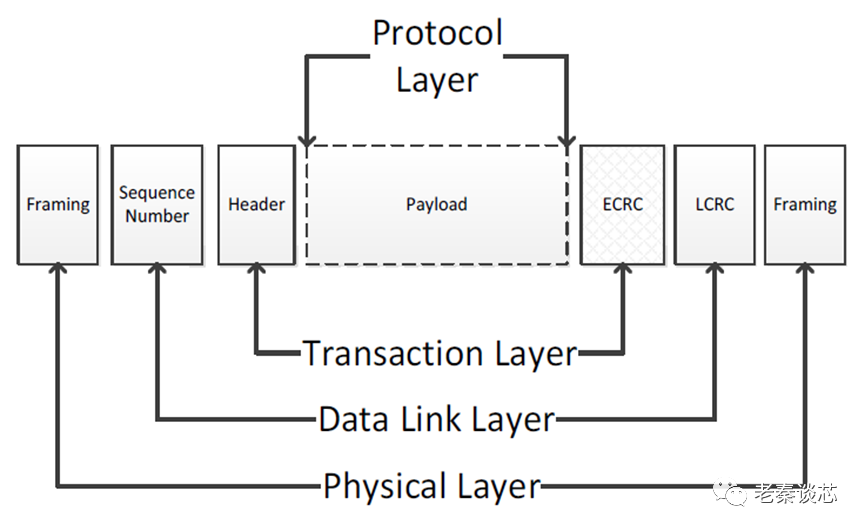

CCIX使用數(shù)據(jù)包在CCIX鏈路層和CCIX事務(wù)層之間傳遞信息。在發(fā)送端,當(dāng)傳輸?shù)臄?shù)據(jù)包在事務(wù)層(Transaction Layer)、數(shù)據(jù)鏈路層(Link Layer)和物理層(Physical Layer)中向下游流動(dòng)時(shí),它們被擴(kuò)展,需要加上在這些層處理數(shù)據(jù)包所需的附加信息。在接收端,發(fā)生相反的過程,包從其物理層傳輸?shù)綌?shù)據(jù)鏈路層,最后轉(zhuǎn)換為可由接收設(shè)備的事務(wù)層處理的形式。

這也是分層架構(gòu)的基本理念,每一層各司其職,只負(fù)責(zé)處理本層的任務(wù)。在傳輸端,各層把上一層的數(shù)據(jù)做為本層的負(fù)載,加上本層所需的信息,傳輸給下一層;在接收端,各層把本層所需要的信息剝離出來,并進(jìn)行處理,然后把其余的數(shù)據(jù)傳輸給上一層。通過分層架構(gòu),可以很好的對(duì)規(guī)范進(jìn)行劃分,從而簡(jiǎn)化設(shè)計(jì)。

4.1.1 CCIX事務(wù)層

CCIX規(guī)范定義了自己的事務(wù)層,替換了PCIe的事務(wù)層,或者說CCIX事務(wù)層是一個(gè)簡(jiǎn)化的PCIe事務(wù)層,其中僅支持以下的事務(wù)層數(shù)據(jù)包(Transaction Layer Packets,后面簡(jiǎn)稱TLPs):

優(yōu)化的TLP

PCIe兼容的TLP

CCIX事務(wù)層的主要職責(zé)是組裝和拆分TLP。

在接收路徑上,CCIX事務(wù)層在將TLP轉(zhuǎn)發(fā)到CCIX鏈路層之前,檢查TLP的完整性。

對(duì)于PCIe兼容的TLP,PCIe基本規(guī)范中規(guī)定的PCIe事務(wù)層檢查適用。

對(duì)于優(yōu)化的TLP,指定了一組新的CCIX事務(wù)層檢查。

CCIX事務(wù)層還負(fù)責(zé)用基于信用的流量控制方式去管理CCIX TLP。在接收路徑上,為通過數(shù)據(jù)完整性檢查,并轉(zhuǎn)發(fā)到協(xié)議層的CCIX TLP返回已發(fā)布的流控制信用。在發(fā)送路徑上,實(shí)現(xiàn)了一個(gè)信用門(credit gate),以基于可用的發(fā)布信用控制CCIX TLP的流量。

4.1.2 PCIe事務(wù)層

CCIX規(guī)范不修改PCIe事務(wù)層。

4.1.3 PCIe數(shù)據(jù)鏈路層

CCIX規(guī)范不修改PCIe數(shù)據(jù)鏈路層,而是按原樣使用它。PCIe數(shù)據(jù)鏈路層充當(dāng)PCIe和CCIX事務(wù)以及CCIX物理層之間的中間層。數(shù)據(jù)鏈路層的主要職責(zé)包括鏈路管理和數(shù)據(jù)完整性,包括錯(cuò)誤檢測(cè)和錯(cuò)誤糾正。

4.1.4 CCIX物理層

CCIX物理層以特定于實(shí)現(xiàn)的格式與PCIe數(shù)據(jù)鏈路層交換數(shù)據(jù)包信息。該層負(fù)責(zé)將從PCIe數(shù)據(jù)鏈路層接收的數(shù)據(jù)包信息轉(zhuǎn)換為適當(dāng)?shù)男蛄谢袷剑⒁耘c連接到鏈路另一側(cè)的設(shè)備兼容的數(shù)據(jù)速率和PCIe寬度在CCIX鏈路上傳輸。

CCIX物理層定義了兩種物理層類型。CCIX組件只需要支持其中一種:

PCIe PHY:這種PHY類型符合PCIe基本規(guī)范

擴(kuò)展數(shù)據(jù)速率(Extended Data Rate,EDR):這種PHY類型支持PCIe基本規(guī)范的所有要求,具有16.0 GT/s的能力,并將支持的數(shù)據(jù)速率擴(kuò)展到20.0 GT/s和25.0 GT/s。

4.2 事務(wù)層

4.2.1 CCIX事務(wù)層架構(gòu)

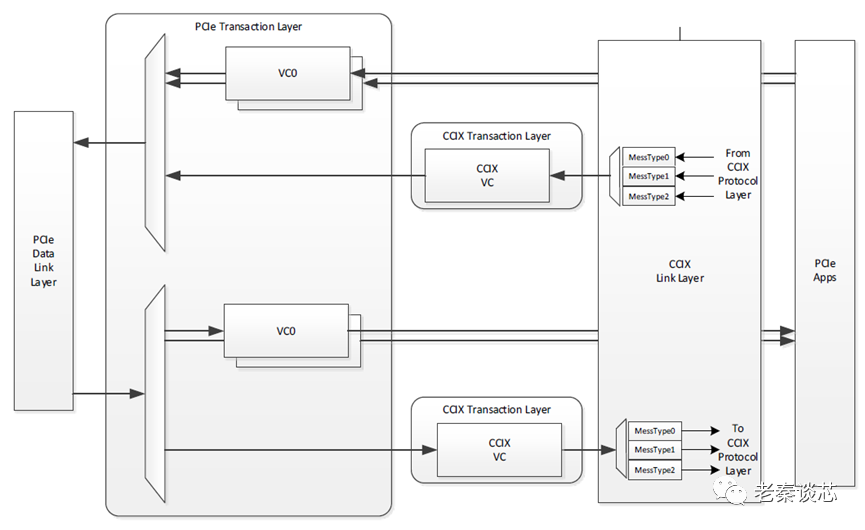

CCIX事務(wù)層中至少要有一個(gè)PCIe虛擬通道(Virtual Channel,VC),也就是VC0,用來交換PCIe TLP。

CCIX事務(wù)層還應(yīng)該有一個(gè)CCIX虛擬通道(CCIX VC),用來交換CCIX TLP,但不能是VC0。

4.2.2 事務(wù)層協(xié)議 – 數(shù)據(jù)包定義

CCIX事務(wù)層必須支持PCIe兼容的TLP,可以選擇支持優(yōu)化的TLP。

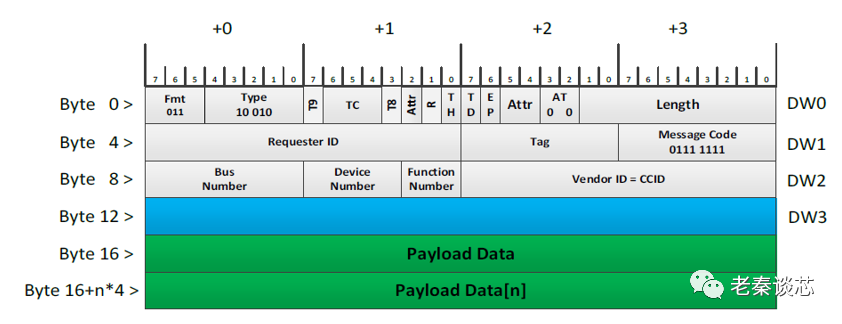

PCIe兼容TLP的格式如下:

消息路由字段必須設(shè)置為010b–按ID路由。

所有CCIX TLP的供應(yīng)商ID字段等于CCID。

PCIe兼容TLP的總長度大于4 DW。因此,TLP Fmt字段為011b。Length[9:0]是供應(yīng)商定義消息的負(fù)載中DW總數(shù)

上圖TLP頭中DW3和數(shù)據(jù)負(fù)載格式在第三章中定義

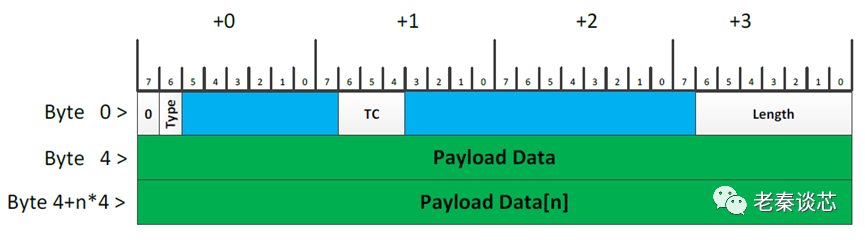

優(yōu)化的TLP格式,且須遵循的規(guī)則:

優(yōu)化的TLP要求是4-byte對(duì)齊,且4-byte增量

優(yōu)化的TLP由1 DW TLP頭部分和最多可包含127 DW的TLP有效載荷部分組成。

字節(jié)0的第7位始終為0b

Type[0]字段指示CCIX硬件規(guī)范版本,目前只有1.0版本

TC [2:0]字段,Traffic Class,流量分類

Length[6:0]是負(fù)載包含的DW數(shù)目

CCIX允許在一個(gè)TLP中打包兩個(gè)或多個(gè)協(xié)議消息,從而使協(xié)議消息傳輸?shù)拈_銷最小化。只有當(dāng)所有協(xié)議消息都具有公共CCIX鏈路時(shí),才支持打包協(xié)議消息。對(duì)于CCIX事務(wù)層來說,打包的消息看起來仍然像一個(gè)帶負(fù)載的TLP。多協(xié)議消息的信息在CCIX鏈路層內(nèi)編碼/解碼,對(duì)事務(wù)層透明。

所有CCIX設(shè)備都需要支持CCIXVC的PCIe兼容TLP格式。只有當(dāng)鏈路兩端都支持優(yōu)化TLP格式功能時(shí),才可以在CCIX VC上交換優(yōu)化的TLP。

在PCIe設(shè)備發(fā)現(xiàn)(discovery)過程中,可以通過讀取DVSEC寄存器來判斷是否支持CCIX。

4.2.3 CCIX虛擬通道

在正常工作條件下,CCIX VC將僅發(fā)送和接收CCIX TLP。CCIX VC為CCIXTLP實(shí)現(xiàn)了一個(gè)先進(jìn)先出(FIFO)隊(duì)列。CCIX VC應(yīng)當(dāng)規(guī)定一個(gè)posted流量控制信用值。這樣,設(shè)計(jì)時(shí)FIFO隊(duì)列的大小就可以確定了。

CCIX VC還應(yīng)當(dāng)規(guī)定一個(gè)non-posted流量控制信用值。CCIX VC上一般預(yù)計(jì)不會(huì)有non-posted TLPs,但是一旦接收到這些TLP,就需要一些資源處理他們。

插播一段,Non-posted(非轉(zhuǎn)發(fā))事務(wù)和Posted(轉(zhuǎn)發(fā))事務(wù)都是PCIe TLP(事務(wù)層包)類型。Non-posted事務(wù)分為兩個(gè)部分,首先是發(fā)送端向接收端發(fā)送TLP請(qǐng)求,接收端接收到請(qǐng)求完成后向發(fā)送端發(fā)送完成TLP。Non-posted事務(wù)必須等待接收到完成TLP,PCIe總線才能結(jié)束當(dāng)前的TLP。PostedTLP不需要完成TLP返回,此種方式中,TLP還沒達(dá)到最終目的地之前,PCIe總線就可以結(jié)束當(dāng)前的事務(wù)。

4.2.4 接收到的TLP的處理

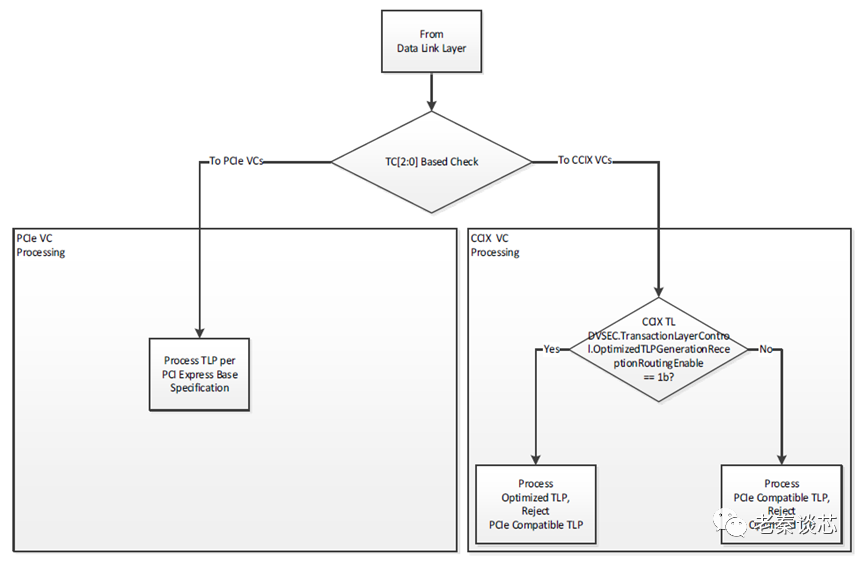

CCIX事務(wù)層接收到的TLP處理流程如下圖:

從數(shù)據(jù)鏈路層接收到TLP后,先通過TC[2:0]判斷是分發(fā)給PCIe虛擬通道還是CCIX虛擬通道。

補(bǔ)充一點(diǎn),TC 是數(shù)據(jù)包的頭內(nèi)的一個(gè)3-bit的字段。用來將流量分成8種(TC0-TC7)不同的類別,本地應(yīng)用軟件和系統(tǒng)軟件根據(jù)性能要求確定某個(gè)TLP使用什么樣的TC標(biāo)志。虛擬通道是物理緩沖區(qū),它通過使用發(fā)送和接收虛擬信道緩沖區(qū),提供一種在鏈路上實(shí)現(xiàn)多個(gè)獨(dú)立數(shù)據(jù)流的方法。PCIe設(shè)備可以實(shí)現(xiàn)最多8個(gè)VC緩沖區(qū)(VC0-VC7)。并且必須要實(shí)現(xiàn) VC0,即最通用的服務(wù)類別。設(shè)備或交換器需要實(shí)現(xiàn)TC/VC映射邏輯,通過該邏輯形成對(duì)應(yīng)關(guān)系,把給定的TC號(hào)的TLP使用特定的VC號(hào)的緩沖區(qū)通過鏈路發(fā)送出去。多個(gè)TC可以對(duì)應(yīng)一個(gè)VC,因而可以使用有限數(shù)目的VC緩沖區(qū)來降低設(shè)備成本。系統(tǒng)軟件通過配置寄存器設(shè)置 TC/VC 的映射。應(yīng)用軟件確定TLP的TC標(biāo)志以及設(shè)置滿足性能要求的TC/VC的映射關(guān)系。最簡(jiǎn)單的情況可以將 TC/VC 映射寄存器設(shè)置為TC到VC的一對(duì)一關(guān)系。

CCIX事務(wù)層的行為由寄存器TransactionLayerControl(這個(gè)寄存器在第六章DVSEC中描述)的比特位OptimizedTLPGenerationReceptionRoutingEnable來控制。如果這個(gè)比特位被設(shè)定(set),發(fā)送方以優(yōu)化的TLP格式生成CCIXTLP,傳輸路徑中的交換機(jī)和接收方接受優(yōu)化的TLP,所有接收方都將拒絕PCIe兼容的TLP。如果這個(gè)比特位被清除(clear),發(fā)送方以PCIe兼容TLP格式生成CCIX TLP,傳輸路徑中的交換機(jī)和接收方接受PCIe兼容TLP,所有接收方都將拒絕優(yōu)化的TLP。

4.2.5 事務(wù)排序規(guī)則

CCIX事務(wù)層應(yīng)遵循PCIe基本規(guī)范中對(duì)事務(wù)排序的所有要求。在正常工作條件下,CCIX VC將僅發(fā)送和接收PCIe兼容的TLP或優(yōu)化的TLP。

4.2.6 虛擬通道機(jī)制

CCIX事務(wù)層應(yīng)遵循PCIe基本規(guī)范中對(duì)虛擬通道機(jī)制的所有要求。VC機(jī)制不區(qū)分PCIe VC和CCIXVC。后面有時(shí)間再分析PCIe的VC機(jī)制。

4.2.7 事務(wù)層流量控制

CCIX事務(wù)層應(yīng)遵循PCIe基本規(guī)范中對(duì)流量控制的所有要求,除去那些僅適用于CCIX VC行為的異常。

4.2.8 數(shù)據(jù)完整性

CCIX事務(wù)層應(yīng)遵循PCIe基本規(guī)范中對(duì)數(shù)據(jù)中毒(Data Poisoning)機(jī)制的所有要求。優(yōu)化的TLP格式不支持PCIe數(shù)據(jù)中毒機(jī)制。

CCIX事務(wù)層應(yīng)遵循PCIe基本規(guī)范中關(guān)于基于端到端CRC(End-to-End CRC)的數(shù)據(jù)完整性機(jī)制的所有要求。優(yōu)化的TLP格式不支持ECRC機(jī)制。

4.2.9 完成超時(shí)機(jī)制

CCIX事務(wù)層應(yīng)遵循PCIe基本規(guī)范中對(duì)完成超時(shí)(Completion Timeout)機(jī)制的所有要求。

4.2.10 鏈接狀態(tài)依賴

CCIX事務(wù)層應(yīng)遵循PCIe基本規(guī)范中對(duì)鏈接狀態(tài)依賴(Link Status Dependencies)機(jī)制的所有要求。

4.3 CCIX數(shù)據(jù)鏈路層

是不是叫PCIe數(shù)據(jù)鏈路層更為合適?

4.4 CCIX物理層邏輯塊

4.4.1 介紹

物理層分為邏輯子塊和電氣子塊。CCIX傳輸規(guī)范擴(kuò)展了PCIe基本規(guī)范中規(guī)定的邏輯和電氣子塊。

4.4.2 CCIX邏輯子模塊

CCIX物理層支持16.0 GT/s,20.0 GT/s和25.0 GT/s的傳輸速率。

支持?jǐn)U展數(shù)據(jù)速率的CCIX設(shè)備可以通過控制ESMControl.ESMEnable比特位(從0變成1),來進(jìn)入擴(kuò)展速率模式(Extended Speed Mode,ESM)。

4.4.3 重定時(shí)器

關(guān)于PCIe Retimer,隨著PCIe協(xié)議的不斷升級(jí),頻率越來越高,對(duì)數(shù)據(jù)在線路中的傳輸長度提出了強(qiáng)烈挑戰(zhàn)。為了解決這一問題,PCIe協(xié)議在4.0版本種提出了Retimer。Retimer實(shí)際上是一種協(xié)議感知設(shè)備,能更好地將信號(hào)傳輸?shù)礁h(yuǎn)。

總結(jié):CCIX 傳輸規(guī)范包含CCIX事務(wù)層和PCIe 事務(wù)層,PCIe 數(shù)據(jù)鏈路層,和CCIX 物理層。這些層負(fù)責(zé)器件間的物理連接,包括速率和帶寬協(xié)商,傳輸包錯(cuò)誤檢測(cè)和重試,和初始包編碼協(xié)議。除去CCIX事務(wù)層,其它層均遵循PCIe標(biāo)準(zhǔn)。

-

PCIe

+關(guān)注

關(guān)注

15文章

1234瀏覽量

82590 -

傳輸層

+關(guān)注

關(guān)注

0文章

29瀏覽量

10889

原文標(biāo)題:老秦帶你探索CCIX(七)

文章出處:【微信號(hào):Rocker-IC,微信公眾號(hào):路科驗(yàn)證】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

詳解太赫茲通信頻段和MAC層工作原理

一文弄懂CCIX協(xié)議層

CCIX 1.1設(shè)備必須支持PCIe 5.0 PHY或CCIX EDR PHY這兩種物理層嗎

CCIX協(xié)議對(duì)于一些高性能應(yīng)用詳解

數(shù)據(jù)鏈路層和傳輸層的區(qū)別是什么

CCIX傳輸層詳解

CCIX傳輸層詳解

評(píng)論