VCO,是一個頻率隨電壓變化的部件,而變容管則是產生該頻率變化的核心。在VCO的各項性能中,有兩個性能,分別為頻率的調諧范圍和輸出信號的相噪。這兩項性能,則對應變容管的兩個特性:(1) 電容的調諧范圍,即變容管能提供的最大電容和最小電容;(2)變容管的品質因數(qulity factor),這個通常受變容管的寄生級聯電阻限制。這兩個參數,在某些情況下,是一個矛盾的關系。

在以前的RFIC設計中,變容管是用反偏的PN結實現。但在現在RFIC設計中,MOS變容管已經取代了PN結,成為主流。

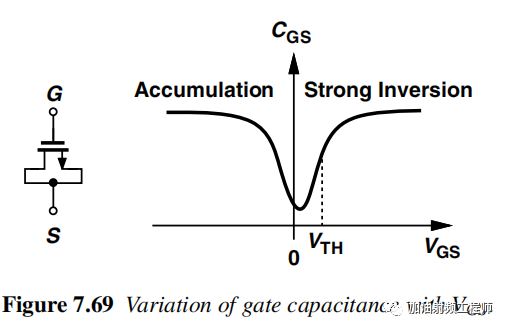

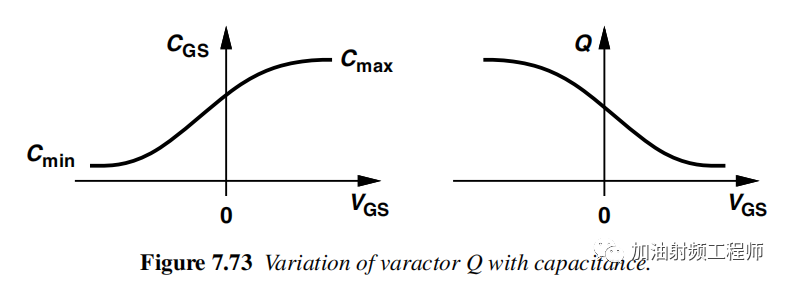

常規的MOSFET在將D極和S極連接時,Cgs與Vgs的關系如下圖所示,Cgs會隨著Vgs變化,但是變化曲線呈現非線性。這個非線性,會產生這樣一個結果。比如說,你設計了一個VCO,當你緩慢升高電壓時,它的輸出頻率也相應地從1G變到2G。但是由于這個非線性的存在,當你緩慢升高電壓時,剛開始頻率是1G變化到1.5G;然后你在緩慢升高電壓,發現頻率又緩慢變回去了。當然,也不是完全不能用,但是總覺得心里有那么點不舒服。

而且,這種非線性的頻率調諧特性,在鎖相環設計中是個問題,會使得鎖相環失鎖。

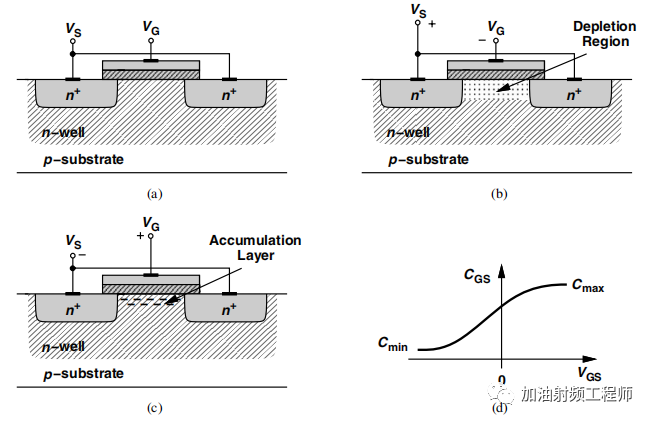

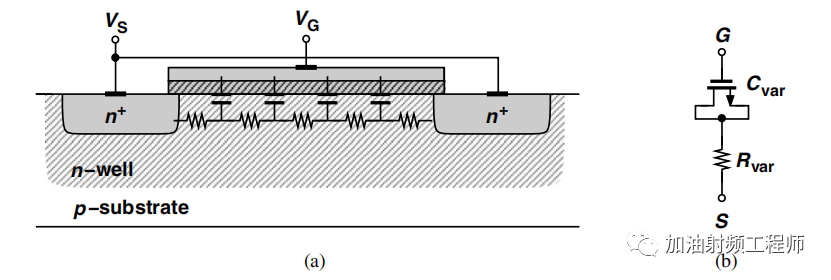

那怎么辦?解決辦法,就是對MOS管做一個小小的調整,具體方法,就是把NMOS管放在一個N阱中,這種MOS管,稱為“累積型MOS變容二極管(Accumulation-mode MOS varacotr)”。

當VGVS時,硅/氧化物的交接面從n+的源極和漏極吸收電子,形成一個通道。此時,等效電容為柵氧電容。

在65nm器件中, VGS ≈ ±0.5 V時,接近其飽和水平的Cmax和Cmin。MOS變容二極管可以在低供電電壓下工作,而且,為了使得MOS管提供最大的調諧特性,MOS管需要正負偏置。

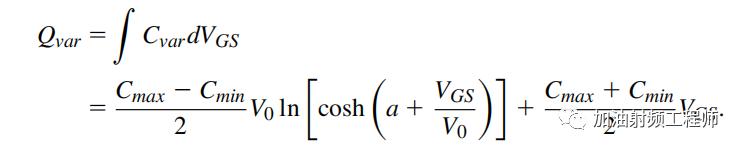

電路仿真,需要在一定程度上能夠模擬變容管的C/V特性曲線。在實際中,這種特性是對加工器件進行測量,然后以由一系列的離散值組成的表格來表征。然后,再用一個連續函數來對C/V曲線進行擬合。雙曲正切能夠很好地模擬其飽和特性,具有連續導數,因此可以用來擬合C/V曲線。

其中a和V0分別允許擬合截點和斜率,而Cmin和Cmax則包含柵漏和柵源的重疊電容。

什么是重疊電容呢(overlap capacitance)?

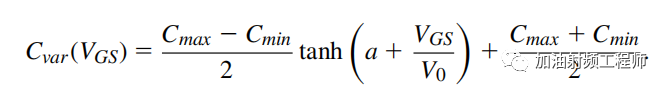

如上圖所示,MOS管有三種主要電容:

一種是柵極和溝道之間的電容,稱為柵氧電容,值為WLCox;

一種為源極和襯底,漏極和襯底之間的PN結電容;

一種為重疊電容(overlap capacitance)。

在加工過程中,會使得柵極和漏極,柵極和源極在結構上部分重疊;另外柵極邊緣與源極/漏極區域頂部之間的邊緣場線,這兩者構成了重疊電容。

上述C/V模型,也可轉換成Q/V模型,即電荷隨電壓變化的曲線。由dQ=C(V)/dV可知,

MOS變容管的Q值,由柵極和漏極之間的電阻決定,如下圖所示。

MOS變容管的Q值又是如何變化的呢?當變容管的容值為Cmin時,其容值低,電阻又比較大;而當變容管的容值為Cmax時,其容值大,而電阻又比較低。由Q=1/(RCw)可知,Q如果按照上述規律變化的話,可能能夠保持不變。實際上,當Cgs從Cmin變化到Cmax時,Q值也是下降的。這表明,當Cgs從Cmin變大到Cmax時,R也會從Rmax變化Rmin,但是顯然C的變化量要大于R的變化量。

在振蕩器設計中,希望最大化變容管的Q值。當溝道長度最短的時候,變容管的Q值最大;但是,此時柵源和柵漏之間的重疊電容在總電容中所占比值增大,從而限制了電容的調諧范圍。重疊電容(overlap capacitance)基本上不太隨電壓變化,它的存在,會使得變容管的特征曲線上移,即從Cmin+2WCov變化到Cmax+2WCov。當溝道長度最短的時候,2WCov甚至會比Cmin還大。因此會降低電容的調諧范圍。

具體用數字來表征一下:假設, Cmax=0.85fF,Cmin=0.18fF,此時R=Cmax/Cmin=4.72;如果考慮重疊電容,假設其值為0.18fF,則Cmax=0.18fF+0.85fF=1.03fF,Cmin=0.18fF+0.18fF=0.36fF,此時R=Cmax/Cmin=2.86。調諧范圍下降。

因此,溝道長度短,變容管Q值大,但是電容的調諧范圍相對較小。變容管Q值和調諧范圍之間的矛盾,反應到VCO的性能上,就是頻率調諧范圍和相噪的矛盾。在實際的設計中,需要折中取舍。

審核編輯:湯梓紅

-

VCO

+關注

關注

12文章

190瀏覽量

69183 -

MOS

+關注

關注

32文章

1269瀏覽量

93683 -

變容管

+關注

關注

0文章

3瀏覽量

5989

原文標題:芯片設計中的變容管

文章出處:【微信號:加油射頻工程師,微信公眾號:加油射頻工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ir21834驅動全橋逆變問題 mos管的漏極和柵極通了

基于積累型MOS變容管的射頻壓控振蕩器設計

硅調頻變容管及其應用

基于積累型MOS 變容管的射頻壓控振蕩器設計

變容管電調諧微波帶通濾波器的設計

MOS管變容特性研究及振蕩頻率估計

RFIC設計中的MOS變容管

RFIC設計中的MOS變容管

評論