在設(shè)計高速高密度PCB時,串擾(crosstalk interference)確實是要特別注意的,因為它對時序(timing)與信號完整性(signal integrity)有很大的影響。以下提供幾個注意的地方:

控制走線特性阻抗的連續(xù)與匹配。

走線間距的大小,一般常看到的間距為兩倍線寬。可以透過仿真來知道走線間距對時序及信號完整性的影響,找出可容忍的最小間距。不同芯片信號的結(jié)果可能不同。

選擇適當?shù)亩私臃绞健?/p>

避免上下相鄰兩層的走線方向相同,甚至有走線正好上下重疊在一起,因為這種串擾比同層相鄰走線的情形還大。

利用盲埋孔(blind/buried via)來增加走線面積,但是PCB板的制作成本會增加。在實際執(zhí)行時確實很難達到完全平行與等長,不過還是要盡量做到。

除此以外,可以預留差分端接和共模端接,以緩和對時序與信號完整性的影響。

考慮電路板尺寸和電流

大多數(shù)從事電子設(shè)計的人都知道,就像沿著河道走的河流,流動的電子也可能會遇到咽喉點和瓶頸;這一點被直接應用在車用保險絲(automotive fuse)的設(shè)計中。透過控制走線的厚度和形狀(U型彎曲、V型彎曲、S形等),保險絲可以經(jīng)過校準,在電流超載時熔斷于咽喉點。

問題是,設(shè)計工程師偶爾會在他們的PCB設(shè)計中遭遇類似的電氣咽喉點;舉例來說:在用兩個陡峭45度也可以的地方,使用90度彎角;當彎曲度大于90度時,采用之字形狀。充 其量那些導線只會讓訊號傳播速度變慢;最糟糕的情況是它們會像汽車保險絲一樣在電阻點熔斷。

避開裂片風險

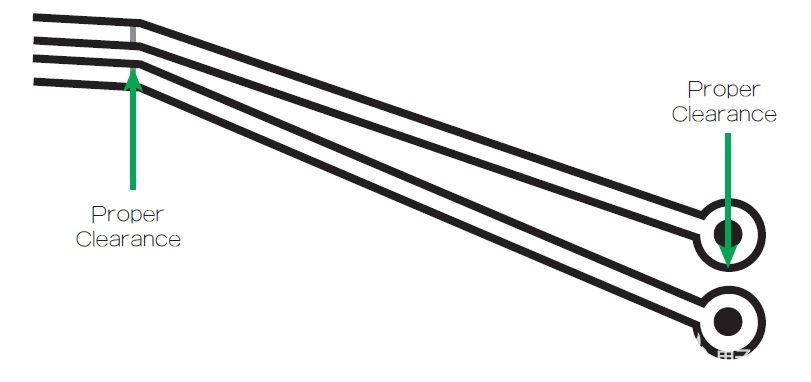

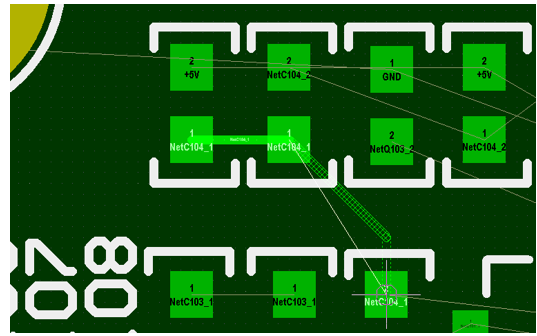

裂片(sliver)是一種制造上的失誤,可透過適當?shù)碾娐钒逶O(shè)計獲得最佳管理(如圖1);為了理解裂片問題,我們需要復習一下化學蝕刻工藝。化學蝕刻是為了分解不需要的銅,但如果要蝕刻的部分特別長、薄、呈片狀,那些形狀有時候會在完全被分解之前整塊剝離;這種裂片會飄浮在化學溶液中,有可能隨機落在另一片電路板上。

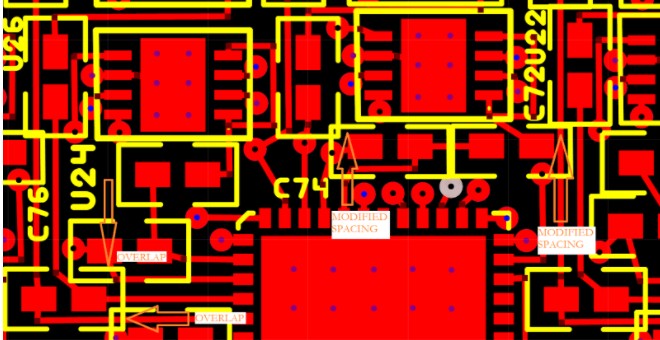

圖1 在這個案例中,走線之間的窄屏蔽對電路基板來說是安全的。

同樣有可能發(fā)生的風險是,裂片仍留在原來那片電路板上;如果裂片夠窄,酸液池可能會腐蝕掉下方足夠多的銅,使裂片部分剝離。于是裂片像旗子一樣黏著電路板四處飄,最后還是免不了落到那片板子上導致其他走線短路。

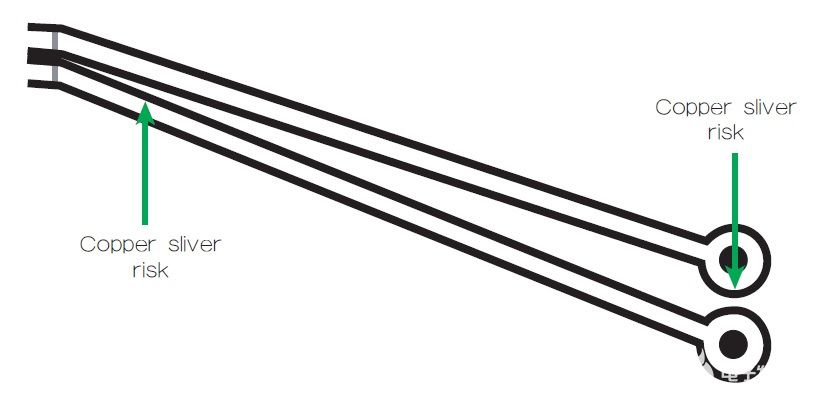

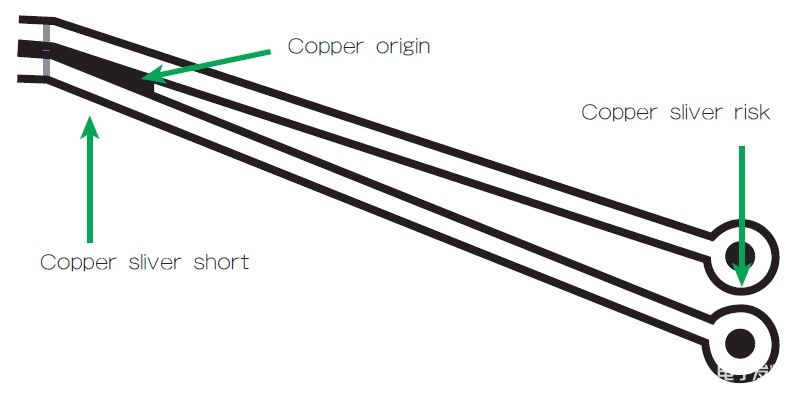

那么該去哪里尋找潛在的裂片?又如何避免裂片產(chǎn)生呢?在進行PCB布線時,最好避免留下非常窄的銅線區(qū)域(如圖2);這種區(qū)域通常是走線與焊墊間隙出現(xiàn)交叉、平面被填滿的情況造成(圖3)。將銅線的最小寬度設(shè)置為大于制造商允許的最小值,你的設(shè)計應該就不會有這方面的問題。標準的最小蝕刻寬度是0.006英吋。

圖2 一個非常狹窄的裂片風險區(qū)域,例如圖中這個原始設(shè)計檔內(nèi)的案例,在制造時可能不受控制地剝離,導致短路和良率問題。

圖3 在這個案例中,化學蝕刻會改變狹窄裂片填充的形狀/尺寸;裂片剝離時會產(chǎn)生意料不到的碎屑或漂浮物。

關(guān)注DRC

自動布線器的設(shè)置通常是針對設(shè)計功能,而設(shè)計規(guī)則檢查器(Design Rule Checker,DRC)一般是用來擷取制造商的設(shè)計約束;雖然設(shè)置過程同樣繁瑣,跟自動布線器比起來要好得多。大多數(shù)設(shè)計團隊最終都會建立一整套設(shè)計規(guī)則,目的是標準化裸板制作成本、最大化良率,并讓組裝、檢查和測試盡可能一致。

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4319文章

23080瀏覽量

397511 -

電路板

+關(guān)注

關(guān)注

140文章

4951瀏覽量

97689 -

串擾

+關(guān)注

關(guān)注

4文章

189瀏覽量

26943

發(fā)布評論請先 登錄

相關(guān)推薦

高速PCB設(shè)計指南的高密度(HD)電路設(shè)計

PCB布線常見面試題,你都會嗎?(4)

在高速(>100MHz)高密度PCB設(shè)計中的技巧?

PCB布局及原理圖交互式抓取

高速高密度PCB設(shè)計的關(guān)鍵技術(shù)問題是什么?

高速高密度PCB設(shè)計中電容器的選擇

高速高密度PCB設(shè)計的新挑戰(zhàn)概述

高速高密度PCB的SI問題

Altium Designer入門教程之印刷電路板的布線設(shè)計詳細資料說明

高速高密度PCB設(shè)計面臨著什么挑戰(zhàn)

PCB設(shè)計中管理高密度通孔的需求設(shè)計

淺談高密度PCB設(shè)計中的元件放置

高密度PCB設(shè)計中的技巧

高密度PCB設(shè)計中的技巧

評論