本文作者:張倩憶,沈龍

Cadence 公司 DSG Product Engineering Group

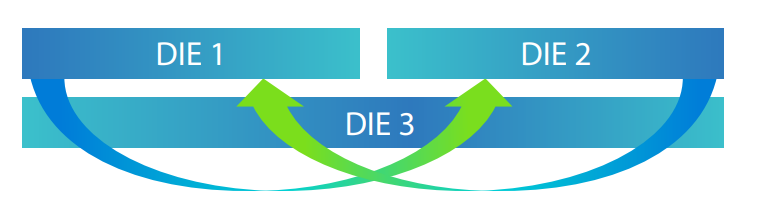

先進(jìn)工藝制程使得設(shè)計(jì)工程師們一次又一次突破了芯片性能、功耗和面積的極限。為了可以繼續(xù)速度更快、功能更強(qiáng)、造價(jià)更省的追求,摩爾人依然在孜孜不倦地尋找新的方法。3D-IC 即是其中之一:通過(guò)封裝和互聯(lián)技術(shù)的更新使得多個(gè)裸片(die)可以集成在同一片晶片(chip)中,這樣片內(nèi)的高速互聯(lián)就替代了之前片外的低速互聯(lián)。這一新維度為未來(lái)芯片的性能提升創(chuàng)造了無(wú)限可能,從今年 5 月起我們(查看文末往期內(nèi)容)已經(jīng)連續(xù) 5 期詳細(xì)揭秘了 Cadence 系統(tǒng)平臺(tái)如何為 3D 設(shè)計(jì)者提供幫助。現(xiàn)在我們來(lái)看一下這其中涉及的新的互聯(lián)方式和工藝集成對(duì)寄生參數(shù)和時(shí)序分析又帶來(lái)了哪些挑戰(zhàn),以及我們?nèi)绾蜗惹耙徊綖樾酒灪巳藛T做好準(zhǔn)備。

uBUMP 和 TSV 的寄生如何抽取

靜態(tài)時(shí)序分析的集成與擴(kuò)容

如何應(yīng)對(duì) PVT 分析 corner 的爆炸式增長(zhǎng)

設(shè)計(jì)案例

01uBUMP 和 TSV 的寄生如何抽取

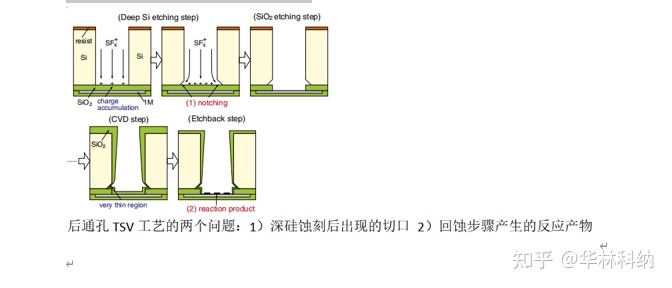

首先介紹下什么是 uBUMP 和 TSV。

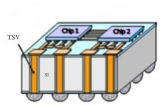

uBUMP 通常是用來(lái)連接上下兩個(gè)裸片堆疊的,需要用 IPF(Inter-Process-File)文件來(lái)定義。通孔(VIA)是定義在兩個(gè)相鄰繞線層之間的。TSV(Through Silicon Via)是指定義在 3D-IC 工藝中連接背面第一層金屬和正面第一層的通孔。還有一種 Long TSV 是指連接背面第一層金屬和正面第一層以上某一層金屬之間的通孔。

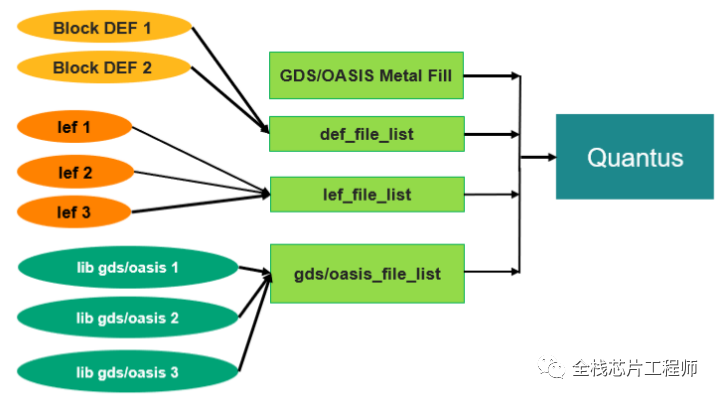

Quantus 在寄生參數(shù)抽取時(shí)對(duì)于 uBUMP 和 TSV 有兩種計(jì)算方式。一種是通常在 ICT 文件中用模型語(yǔ)句來(lái)描述,另一種是通過(guò)定義一個(gè)額外的 TSV 模型文件(.subckt)在整體寄生參數(shù)抽取時(shí)進(jìn)行標(biāo)注。目前 Quantus 對(duì)于用 TSV 模型語(yǔ)句的方式可以支持電阻和對(duì)地電容的抽取,這些電阻電容值和普通的寄生參數(shù)抽取一樣是寫(xiě)在輸出網(wǎng)表中。

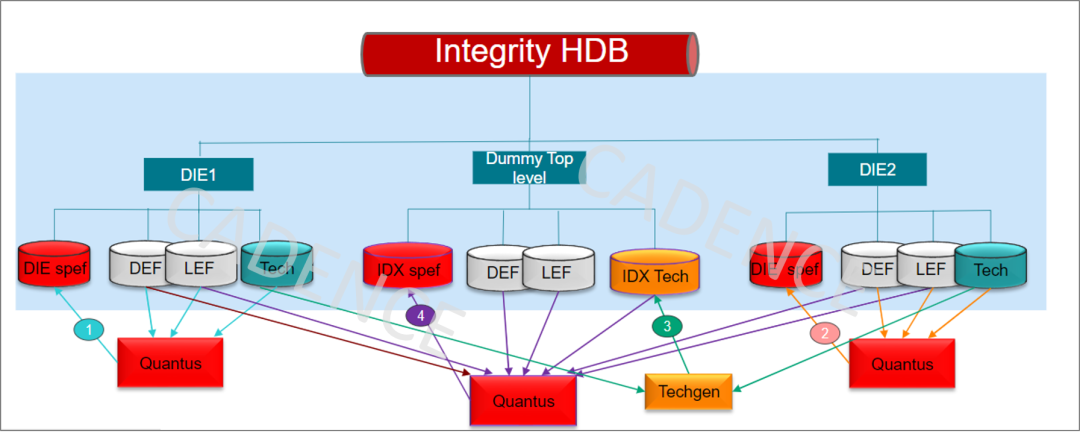

02中介層之間出現(xiàn)的耦合電容亟待考慮嗎

基本的 3D-IC 的寄生參數(shù)抽取包括 TSV、uBUMP 還有芯片背面金屬層的抽取。然而隨著工藝的進(jìn)步,兩個(gè) DIE 之間的距離更靠近,所以?xún)烧呃@線之間的電容就變得不容忽視了。Quantus 目前可以支持 IDX 電容抽取了。IDX 是 3D-IC 中兩個(gè) DIE 之間形成的新的耦合電容,利用兩個(gè) DIE 之間的耦合電容可以做更精準(zhǔn)的系統(tǒng)級(jí)靜態(tài)時(shí)序分析,這兩個(gè) DIE 可以是相同或者不同制造工藝。IDX 寄生抽取支持 Cadence Integrated 3D-IC 中的 iHDB 輸入,并且可以把輸出結(jié)果存入 iHDB 以便后續(xù)的 Tempus 進(jìn)行時(shí)序分析。

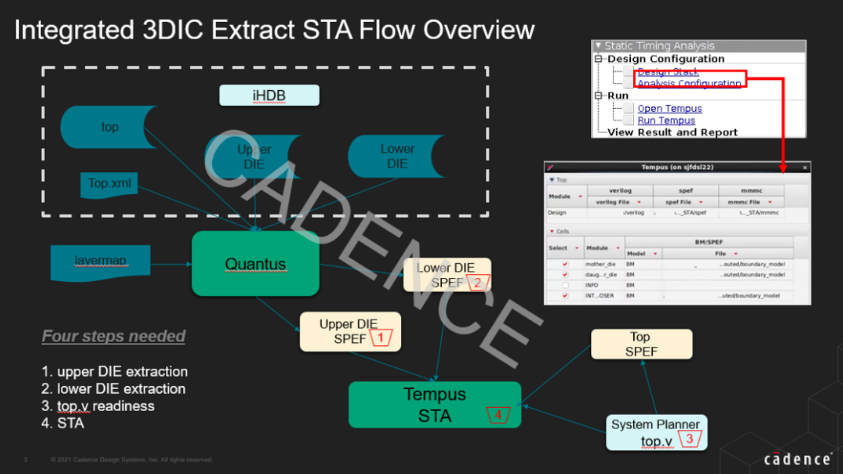

03靜態(tài)時(shí)序分析的集成與擴(kuò)容

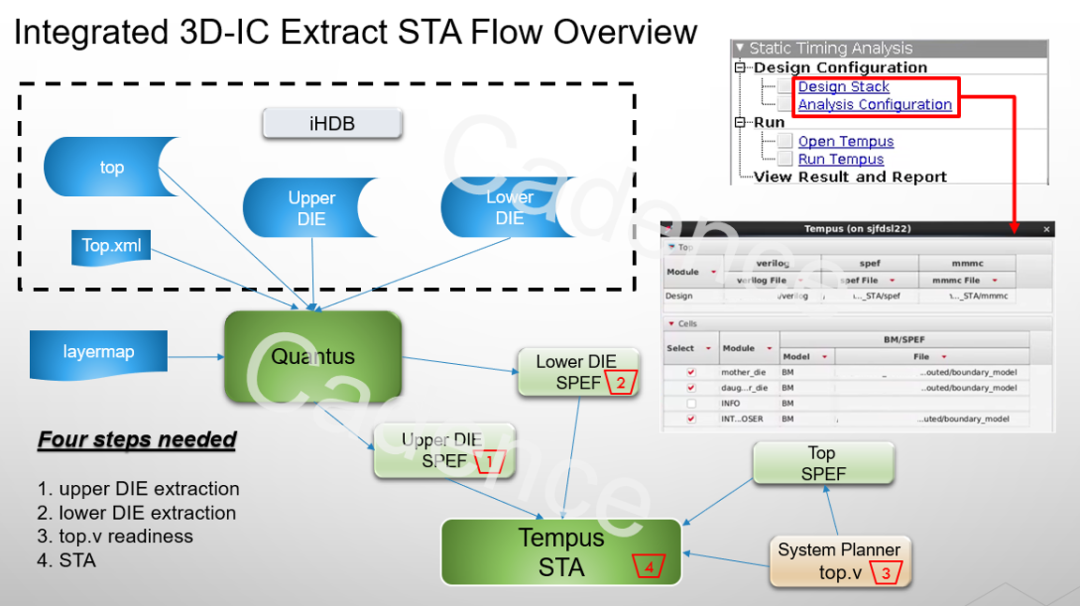

靜態(tài)時(shí)序分析(STA)一直是芯片簽核工程師關(guān)注的重點(diǎn)。Integrity 3D-IC 平臺(tái)自然是不能少了 STA 的功能集成。除了命令行和腳本的輸入,平臺(tái)的用戶(hù)界面也添加了用戶(hù)交互界面的支持,比如一直很受 Tempus 和 Innovus 使用者喜愛(ài)的 Global Timing Debug (GTD),該功能可以協(xié)助分析關(guān)鍵路徑的時(shí)序違例原因。

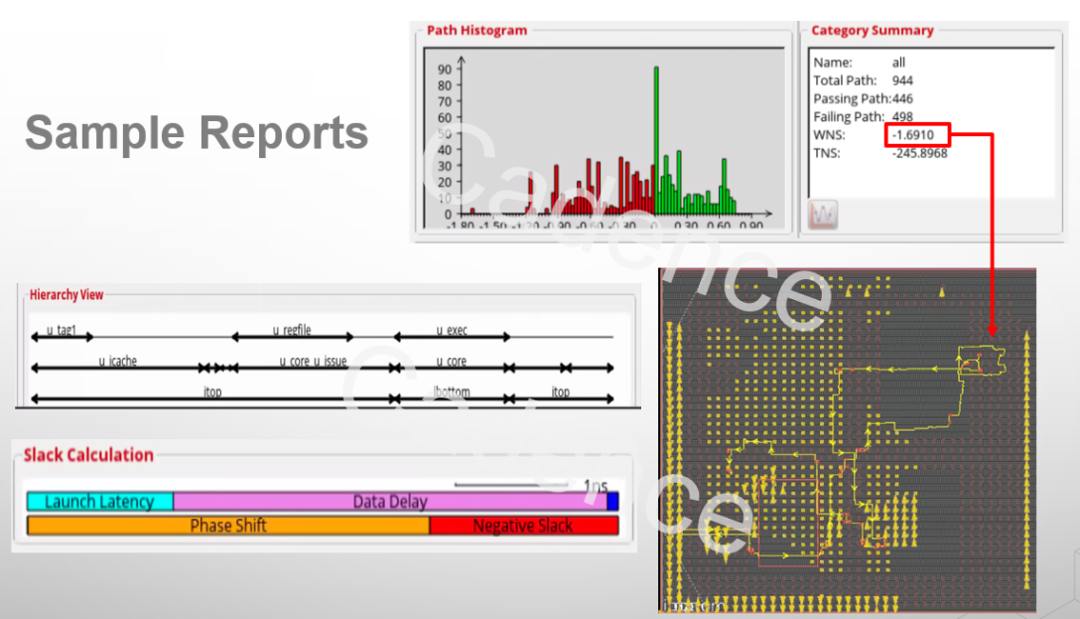

如下圖所示,STA 產(chǎn)生報(bào)告之后,GTD 為設(shè)計(jì)工程師顯示 Path Histogram、Path Layout、Hierarchy、Slack Calculation 和其他許多很有價(jià)值的分析報(bào)告和視圖。具體使用描述詳見(jiàn) Cadence support 官網(wǎng)上的Global Timing Debug(GTD)using Tempus or Innovus, version 18.1(cadence.com)(請(qǐng)掃描下方二維碼登錄 Cadence Support 查看)

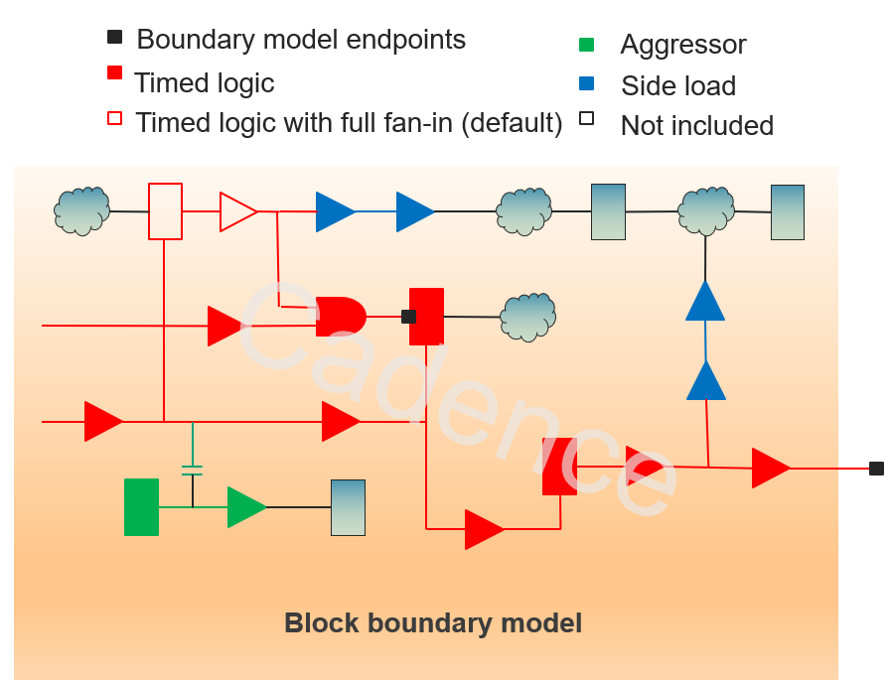

芯片的復(fù)雜度可以無(wú)限增加了,設(shè)計(jì)規(guī)模自然也隨之上升。當(dāng) flatten 的全芯片分析時(shí)間過(guò)長(zhǎng)或者內(nèi)存用量過(guò)大時(shí),就需要考慮通過(guò)抽取簡(jiǎn)化模型進(jìn)行層次化時(shí)序分析。在 Tempus 里這一解決方案叫做邊界模型(Boundary Mode)。如下圖左所示這個(gè)模型去除了 block 內(nèi)部 reg->reg 的 path 僅保留 block 對(duì)外互聯(lián)以及相關(guān)聯(lián)的部分,包括:

所有的 input ports 的 fan-out 邏輯和 output ports 的 fan-in 邏輯

所有對(duì)保留邏輯有 SI 影響的電路

所有保留邏輯的邊負(fù)荷電路(side load)

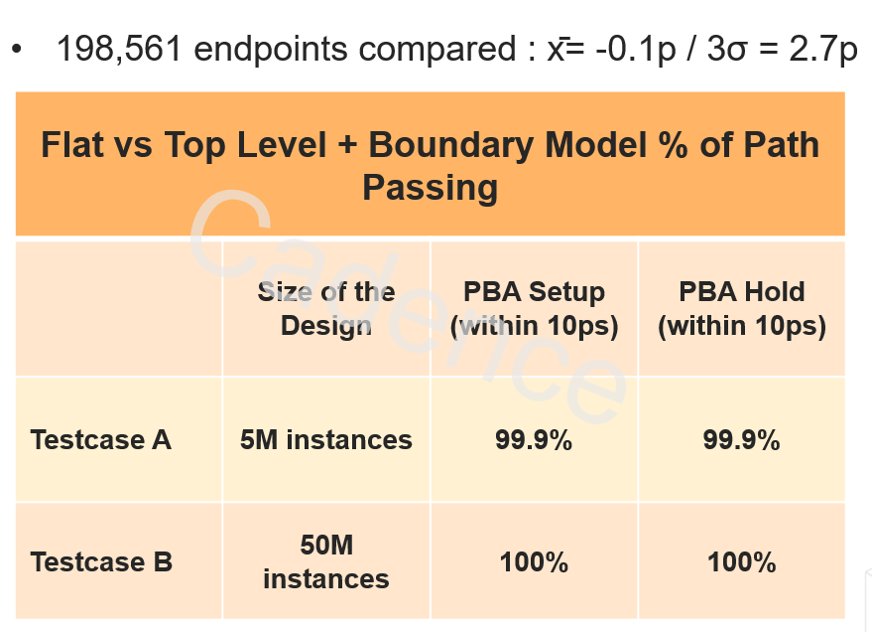

通過(guò)對(duì)每個(gè) die 做 Boundary Model 的抽取,整體網(wǎng)表的縮減率可以達(dá)到 90%,而 setup slack 的平均差異控制在 0.1ps,99.73% 的路徑在 2.7ps 以?xún)?nèi)。

04如何應(yīng)對(duì)PVT分析corner的爆炸式增長(zhǎng)

從性能的角度上來(lái)看,3D-IC 一個(gè)很強(qiáng)大的功能就是支持了本地的、高速的 Die 之間的同步通訊。然而這一新功能也給靜態(tài)時(shí)序簽核(STA)增加了大量的分析 corner。現(xiàn)今的設(shè)計(jì)只有一個(gè) Die 在做全局 STA,每條時(shí)序路徑都是在一組給定的 PVT 參數(shù)下做分析。在 3D-IC 設(shè)計(jì)中,多個(gè) Die 是同時(shí)工作在不同的 PVT 參數(shù)下。設(shè)想當(dāng)你有一條同步的時(shí)序路徑從 Bottom Die 開(kāi)始出發(fā)(startpoint),經(jīng)過(guò) Middle Die,最后抵達(dá) Top Die(endpoint),這條 path 就會(huì)經(jīng)歷三種不同的 PVT 條件,好像我們從北半球旅行到南半球會(huì)穿越不同地理環(huán)境和氣候。

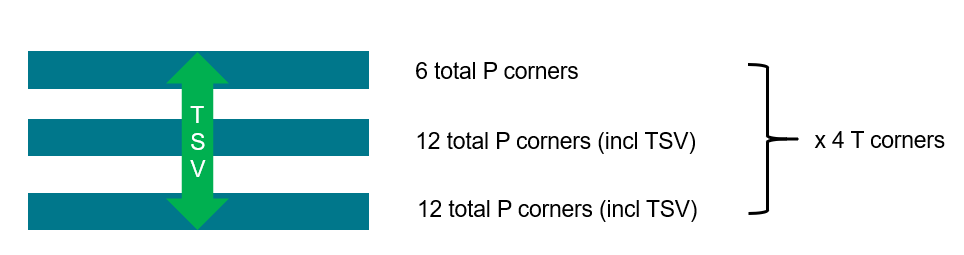

因?yàn)?3D 設(shè)計(jì)允許每個(gè) Die 可以有獨(dú)自的 PVT corner,這樣 STA 簽核就必須涵蓋所有的可能出現(xiàn)的組合情況。以上圖里三個(gè) Die 的典型設(shè)計(jì)為例,如果 Die1 和 Die2 的 process corner 都是 12 個(gè),Die3 是 6 個(gè);三個(gè) Die 的 Voltage corner 和 Temperature corner 都只考慮 2 個(gè)相同的,那么總共需要分析的 corner 數(shù)量就已經(jīng)達(dá)到(12x12x6)x 2 x 2 = 3456 個(gè)。

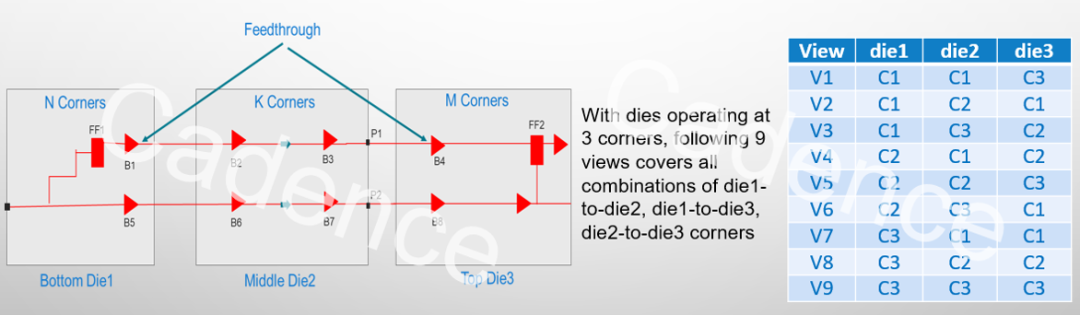

針對(duì)這個(gè) 3D 設(shè)計(jì)中 corner 爆炸式增長(zhǎng)的挑戰(zhàn),Tempus 開(kāi)發(fā)了一個(gè)新的 Rapid Automated Inter-Die(RAID)技術(shù),可以在分析這些 feed through paths 時(shí)巧妙地大量縮減 corner 數(shù)量,同時(shí)保證計(jì)算精度。下圖是一個(gè)非常簡(jiǎn)化的 3 層 Die 的例子,假設(shè)每層都只有 3 個(gè) corner(N=K=M=3),那么全組合需要分析的 corner 數(shù)量就是 27 個(gè)(N*K*M)。Feed through 的部分通過(guò) represent delay 和 adjustment 替換,K 最大就可以 reduce 到 1,這樣在這個(gè) case 里 corner 就減小到了 9 個(gè),corner 的縮減率是 3X。對(duì)于中間 Die 超過(guò) 10 個(gè) corner 的設(shè)計(jì),reduction ratio 將會(huì)超過(guò) 10X;對(duì)于更多層堆疊的 3D 設(shè)計(jì),縮減率就更為可觀!

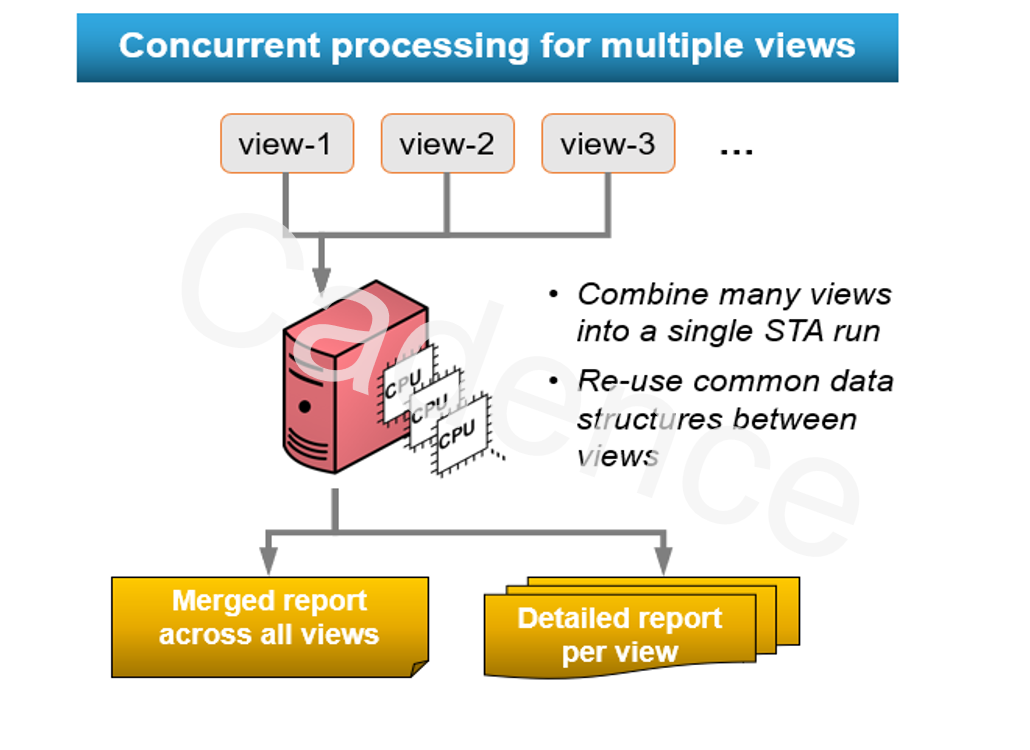

對(duì)于沒(méi)有 feed through 的一般 path 分析,corner 增長(zhǎng)的數(shù)量不會(huì)如此龐大,但是仍然會(huì)對(duì)機(jī)器的需求量隨著設(shè)計(jì)的復(fù)雜度增加不斷攀升。Cadence 另一現(xiàn)有的強(qiáng)大并行分析引擎 concurrent multi-mode multi-corner(C-MMMC)就為此提供了第二個(gè)維度的解決方案。該功能通過(guò)高效復(fù)用多個(gè) corner 的相同的 DB 數(shù)據(jù),儲(chǔ)存有效減輕計(jì)算量的中間數(shù)據(jù)和提高 CPU 的并行使用率,從而大幅降低了對(duì)機(jī)器和硬盤(pán)的使用需求。對(duì)于相同 delay corner 不同 constraint corner的 STA 分析,運(yùn)行時(shí)間和內(nèi)存使用的增加量都只有 20% 左右,相對(duì)于串行分析 CMMMC 的 runtime reduction 通常可以達(dá)到 4-5X。

05設(shè)計(jì)案例

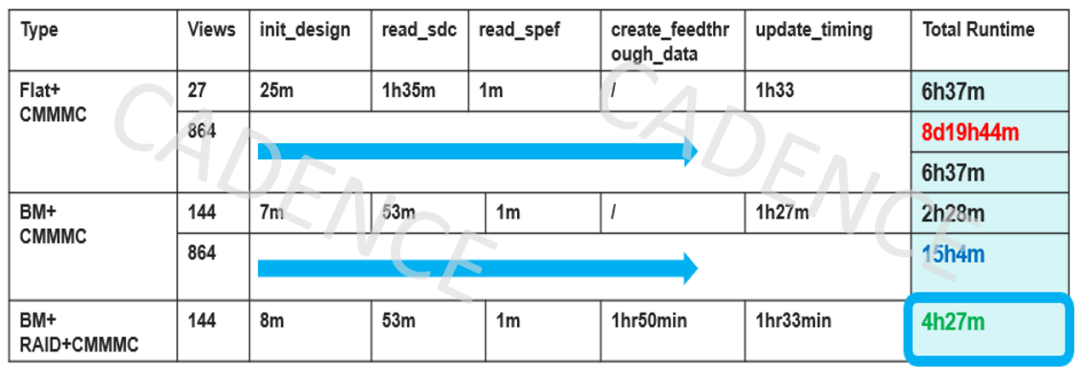

最后讓我們看一個(gè) 5nm 的實(shí)際 3D 設(shè)計(jì)案例,該設(shè)計(jì)包含一個(gè) logic die 有 6 個(gè) process corner,和 2 個(gè) SRAM 的 die 分別有 12 個(gè) process corner。如果使用傳統(tǒng)的 STA 分析,即使是在 CMMMC 模式下完成所有 864(6*12*12)個(gè) process corner 的組合分析也需要 8-9 天(多線程使用 32 個(gè) CPU,@2.6GHZ 主頻)。使用 Boundary Model 技術(shù)之后時(shí)間可以極大縮短至 15 個(gè)小時(shí);繼續(xù)使用 RAID 技術(shù)之后,簽核 corner 的個(gè)數(shù)降低至 144 個(gè),完成相同的時(shí)序分析僅僅使用了驚人的 4 小時(shí) 27 分鐘!加上產(chǎn)生 Boundary Model 所需要的最長(zhǎng)時(shí)間(6 小時(shí) 50 分鐘),速度提升仍然接近 40X!

Cadence Integrity 3D-IC 平臺(tái)是業(yè)界首個(gè)全面的整體 3D-IC 設(shè)計(jì)規(guī)劃,實(shí)現(xiàn)和分析平臺(tái)。該平臺(tái)以全系統(tǒng)的視角,集成了 Cadence 公司的多個(gè)強(qiáng)勢(shì)分析工具和優(yōu)化引擎,對(duì)芯片的性能、功耗、散熱和面積做了全面的評(píng)估和優(yōu)化。其中寄生參數(shù)提取工具 Quantus 準(zhǔn)確計(jì)算 3D 通孔和中階層之間的電阻電容效應(yīng);靜態(tài)時(shí)序分析工具 Tempus 極大地提高了多工藝組合 STA 分析的效率,把之前需要以周記的分析速度減少以小時(shí)計(jì)算。強(qiáng)大準(zhǔn)確的算力為高帶寬高數(shù)據(jù)吞吐量的機(jī)器學(xué)習(xí)、高性能存儲(chǔ)設(shè)備、云端計(jì)算等 3D-IC 應(yīng)用保駕護(hù)航。

如您需了解更多這部分的內(nèi)容,請(qǐng)點(diǎn)擊“閱讀原文”注冊(cè)申請(qǐng)我們的 Integrity 3D-IC 資料包:

- Cadence Integrity 3D-IC 平臺(tái)產(chǎn)品手冊(cè)

- Cadence 3D-IC Extraction & STA Solutions PPT 介紹

注冊(cè)成功且通過(guò) Cadence 審核的用戶(hù)可獲得完整版 PPT 資料。

注:審核通過(guò)后 Cadence 會(huì)將 PPT 發(fā)送至您的郵箱,提供您的公司郵箱地址通過(guò)審核的幾率更大哦!

Cadence Integrity 3D-IC 平臺(tái)提供了一個(gè)高效的解決方案,用于部署 3D 設(shè)計(jì)和分析流程,以實(shí)現(xiàn)強(qiáng)大的硅堆疊設(shè)計(jì)。該平臺(tái)是 Cadence 數(shù)字和簽核產(chǎn)品組合的一部分,支持 Cadence 公司的智能系統(tǒng)設(shè)計(jì)戰(zhàn)略(Intelligent System Design),旨在實(shí)現(xiàn)系統(tǒng)驅(qū)動(dòng)的卓越 SoC 芯片設(shè)計(jì)。

關(guān)于 Cadence

Cadence 在計(jì)算軟件領(lǐng)域擁有超過(guò) 30 年的專(zhuān)業(yè)經(jīng)驗(yàn),是電子系統(tǒng)設(shè)計(jì)產(chǎn)業(yè)的關(guān)鍵領(lǐng)導(dǎo)者。基于公司的智能系統(tǒng)設(shè)計(jì)戰(zhàn)略,Cadence 致力于提供軟件、硬件和 IP 產(chǎn)品,助力電子設(shè)計(jì)從概念成為現(xiàn)實(shí)。Cadence 的客戶(hù)遍布全球,皆為最具創(chuàng)新能力的企業(yè),他們向超大規(guī)模計(jì)算、5G 通訊、汽車(chē)、移動(dòng)設(shè)備、航空、消費(fèi)電子、工業(yè)和醫(yī)療等最具活力的應(yīng)用市場(chǎng)交付從芯片、電路板到完整系統(tǒng)的卓越電子產(chǎn)品。Cadence 已連續(xù)八年名列美國(guó)財(cái)富雜志評(píng)選的 100 家最適合工作的公司。如需了解更多信息,請(qǐng)?jiān)L問(wèn)公司網(wǎng)站 cadence.com。

2022 Cadence Design Systems, Inc. 版權(quán)所有。在全球范圍保留所有權(quán)利。Cadence、Cadence 徽標(biāo)和 www.cadence.com/go/trademarks 中列出的其他 Cadence 標(biāo)志均為 Cadence Design Systems, Inc. 的商標(biāo)或注冊(cè)商標(biāo)。所有其他標(biāo)識(shí)均為其各自所有者的資產(chǎn)。

-

芯片

+關(guān)注

關(guān)注

456文章

50892瀏覽量

424326 -

Cadence

+關(guān)注

關(guān)注

65文章

923瀏覽量

142222 -

TSV

+關(guān)注

關(guān)注

4文章

115瀏覽量

81485

原文標(biāo)題:3D-IC 設(shè)計(jì)之寄生抽取和靜態(tài)時(shí)序分析

文章出處:【微信號(hào):gh_fca7f1c2678a,微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TSV工藝流程與電學(xué)特性研究

請(qǐng)問(wèn)有TSV6390AIDT和/或TSV6290AIDT的SPICE型號(hào)嗎?

硅通孔(TSV)電鍍

通用輸入/輸出軌到軌低功耗操作放大器TSV321/TSV358/TSV324/TSV321A/TSV358A/TSV324A

微(60μ一)寬的帶寬(2.4 MHz)的CMOS運(yùn)算放大器TSV6390/TSV6390A/TSV6391/TSV6391A

高功因數(shù)(1.15兆赫為45微米)cmos運(yùn)算放大器TSV521/TSV522/TSV524/TSV521A/TSV522A/TSV524A

軌到軌輸入/輸出60μ880千赫5V CMOS運(yùn)算放大器TSV630/TSV630A/TSV631/TSV631A

軌到軌輸入/輸出,29μ,420 kHz的CMOS運(yùn)算放大器TSV62x,TSV62xA

軌到軌輸入/輸出29μ420 kHz的CMOS運(yùn)算放大器TSV620,TSV620A,TSV621,TSV621A

寄生電感怎么產(chǎn)生的_寄生電感產(chǎn)生原因是什么

什么是TSV封裝?TSV封裝有哪些應(yīng)用領(lǐng)域?

抽取式摘要方法中如何合理設(shè)置抽取單元?

TSV陣列建模流程詳細(xì)說(shuō)明

什么是硅或TSV通路?使用TSV的應(yīng)用和優(yōu)勢(shì)

uBUMP和TSV的寄生如何抽取

uBUMP和TSV的寄生如何抽取

評(píng)論