復位的目的

復位信號在數字電路里面的重要性僅次于時鐘信號。對一個芯片來說,復位的主要目的是使芯片電路進入一個已知的,確定的狀態。主要是觸發器進入確定的狀態。在一般情況下,芯片中的每個觸發器都應該是可復位的。

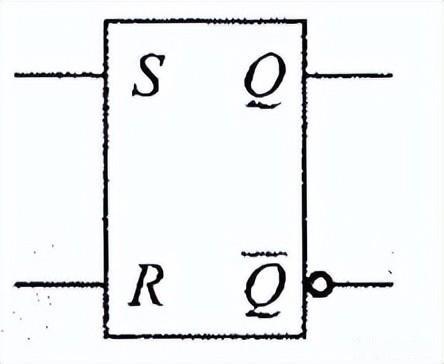

異步復位D觸發器

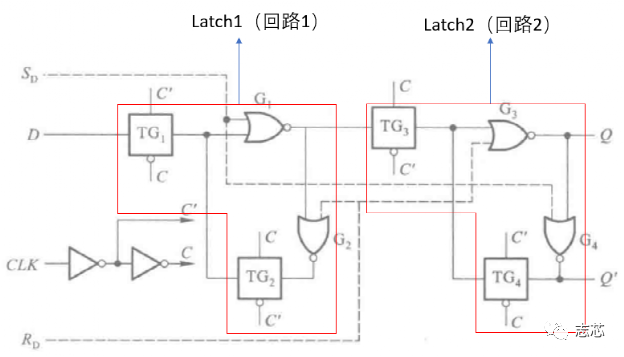

如圖1,將邊沿觸發的D觸發器的結構稍作改變,可以得到異步復位和異步置位的D觸發器;所謂置位就是不需要通過時鐘電平變化直接將D觸發器的鎖存值改變;所謂復位就是不需要通過時鐘電平變化,直接將觸發器鎖存值置0。為了實現異步復位和置位功能,需要引入SD和RD信號。因為SD和RD是以高電平作為置1和置0輸入信號的,所以必須把D觸發器的4個反相器變成或非門。其中,SD和RD端的內部連線以虛線示出。

圖1異步復位的D觸發器

對于該異步復位D觸發器的功能探討如下:在非置位或非復位時,SD=RD=0,此時該異步復位D觸發器具有和普通的D觸發器一樣的功能,鎖存狀態只和輸出信號D以及時鐘電平相關。在SD或RD=1時,該異步復位D觸發器可以迅速置位和復位,SD=1,RD=0時,可以迅速置位為1;SD=0,RD=1時,可以迅速復位為0。

recovery time和removal time

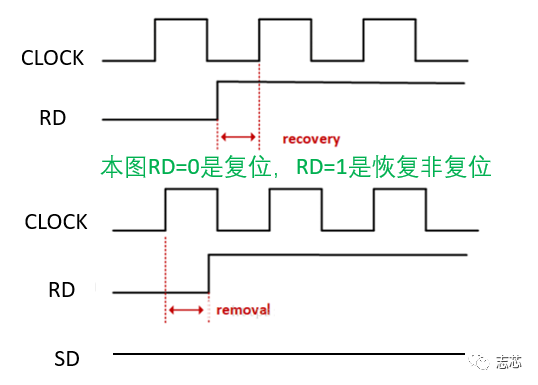

recovery time即恢復時間,撤銷復位時,恢復到非復位狀態的電平必須在時鐘有效沿來臨之前的一段時間到來,才能保證時鐘能有效恢復到非復位狀態,此段時間為recovery time。類似于同步時鐘的setup time。這個針對是本周期的RD的“恢復到非復位狀態的電平”。

removal time 即去除時間,撤銷復位時,在時鐘有效沿來臨之后復位信號還需要保持的時間為去除時間removal time(去除時間)。類似同步時鐘hold time。這個針對是下個周期的RD的“新的復位狀態的電平”。

如上文所討論,復位時SD=0,RD=1時,觸發器輸出態為0;那么撤銷復位時SD=0保持不變,RD會經歷一個從1變為0的下降沿,并保持為0。

圖2恢復時間和去除時間示意圖

圖2中是RD=0時是復位狀態,不過用來說明恢復時間和去除時間的含義,效果是一樣的。

Reset信號怎么產生的

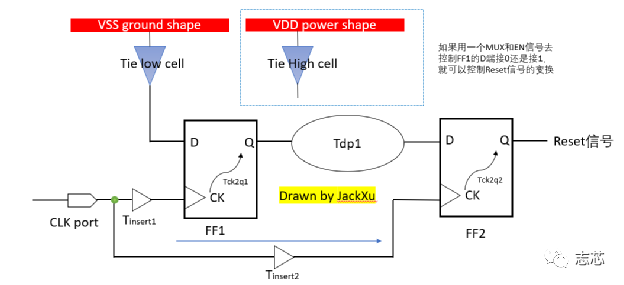

這個真沒研究過。Reset不就是0和1嗎?design中怎么可以提供的穩定的0和1?那就是TIE High cell (Tie 1)和TIE Low cell(Tie 0)。

圖3某reset信號產生電路示意圖

如圖3所示,是我畫的一個reset信號產生電路,沒有官方來源,僅供參考。

為什么reset信號要通過reg接出去?因為reset信號和下一級的異步reset信號之間存在timing check,reg2reg就是同步電路的timing check。

為什么用兩個reg打拍,一個不行嗎?因為reg去采集TIE high或TIE low的信號時,是有一個時間將窗的(時鐘上升沿附近的Tsetup+Thold區間),那么相對來說reg本身采集到的glitch態(亞穩態)幾率很小;如果用兩個reg去采,采集到glitch態的幾率更小。

為什么TIE high和TIE low采集的信號會有glitch?影響因素太多了:環境溫度的突變、附近pg網絡的瞬時變化(例如附近的cell突然翻轉,crosstalk的影響等)、供電電源的電壓突變等等。

審核編輯:湯梓紅

-

D觸發器

+關注

關注

3文章

164瀏覽量

47902 -

reset

+關注

關注

0文章

34瀏覽量

12877 -

復位信號

+關注

關注

0文章

54瀏覽量

6314

原文標題:淺談異步reset

文章出處:【微信號:IC學習,微信公眾號:IC學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

verilog描述異步置0,異步置1功能的D觸發器

D觸發器,CLK突變時,輸入D也突變,觸發器的輸出應該如何判定?

異步復位信號亞穩態的原因與D觸發器的Verilog描述

數字電路中的RS觸發器詳解

D觸發器的類型詳解 同步復位和異步復位D觸發器講解

異步復位D觸發器原理詳解 Reset信號怎么產生的

異步復位D觸發器原理詳解 Reset信號怎么產生的

評論