MS90C386B、MS90C385B/G是瑞盟2012年推出的1Port_LVDS_RxTx,MS90C386B為L(zhǎng)VDS to LVTTL(RGB),直接替換THC63LVDF84B、DS90C386、DTC34LF86L等;MS90C385B/G為L(zhǎng)VTTL(RGB) to LVDS,MS90C385B為TSSOP56封裝,MS90C385G為TFBGA56封裝,直接替換THC63LVD83D、DS90C385、DTC34LF85L等。關(guān)鍵特點(diǎn)如下:

一、MS90C386B:LVDS轉(zhuǎn)LVTTL

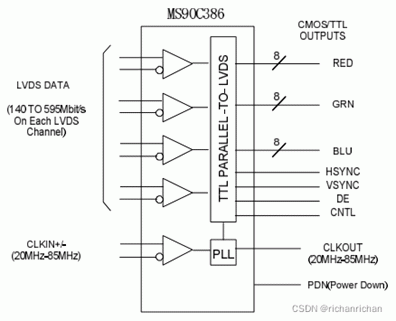

MS90C386(B)芯片能夠?qū)?4 通道的低壓差分信號(hào)(LVDS)轉(zhuǎn)換成 28bit 的 TTL 數(shù)據(jù)。時(shí)鐘通道經(jīng)過(guò)鎖相之后與數(shù)據(jù)通道并行輸出。在時(shí)鐘頻率為 85MHz 時(shí),24bit 的 RGB 數(shù)據(jù)、3bit 的 LCD 時(shí)序數(shù)據(jù)和1bit 的控制數(shù)據(jù)以 595Mbps 的速率在每個(gè) LVDS 數(shù)據(jù)通道中傳輸。輸入時(shí)鐘頻率為85MHz時(shí),數(shù)據(jù)的傳輸速率為 297.5Mbytes/sec。此款芯片配合 MS90C385,是解決高帶寬、高速 TTL 信號(hào)層面的電磁干擾和電纜長(zhǎng)度問(wèn)題的理想產(chǎn)品。

◇Pin to Pin替代:THC63LVDF84B、DS90C386、DTC34LF86L

◇MS90C386 與 MS90C386B 僅版本差異,MS90C386B兼容MS90C386!

◇MS90C386功能框圖

◇頻率范圍:20-85MHz 時(shí)鐘信號(hào)

◇較少的總線減少了連線尺寸和費(fèi)用

◇支持VGA、SVGA、XGA、SXGA,最大支持1440×1050@60Hz、1360×768@60Hz、1280×768@60Hz

◇2.38Gbps數(shù)據(jù)吞吐量

◇297.5Megabytes/sec 帶寬

◇減小LVDS擺幅來(lái)減小電磁干擾(300mV LVDS 擺幅)

◇遵循 TIA/EIA-644 LVDS 標(biāo)準(zhǔn)

二、MS90C385B/G:LVTTL to LVDS

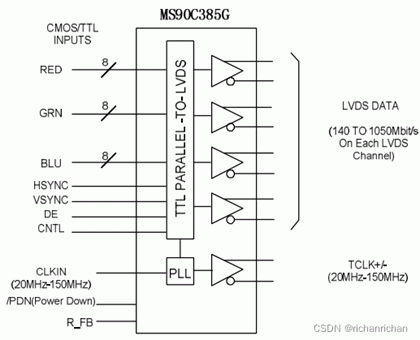

MS90C385B/G 芯片能夠?qū)?8bit 的TTL 數(shù)據(jù)轉(zhuǎn)換成4通道的低壓差分型號(hào)(1Port LVDS)。時(shí)鐘通道經(jīng)過(guò)鎖相之后與數(shù)據(jù)通道并行輸出。在時(shí)鐘頻率為 150MHz 時(shí),24bit的RGB 數(shù)據(jù)、3bit 的 LCD 時(shí)序數(shù)據(jù)和1bit的控制數(shù)據(jù)以 1050Mbps 的速率在每個(gè) LVDS 數(shù)據(jù)通道中傳輸。輸入時(shí)鐘頻率為 150MHz 時(shí),數(shù)據(jù)的傳輸速率為 525Mbytes/sec。MS90C385 的R_FB 管腳可以選擇在時(shí)鐘的上升沿或者下降沿有效。此款芯片是解決高帶寬、高速 TTL 信號(hào)層面的電磁干擾和電纜長(zhǎng)度問(wèn)題的理想產(chǎn)品。

◇MS90C385B/G功能框圖

◇MS90C385B封裝TSSOP56, MS90C385G封裝TFBGA56

◇MS90C385B Pin to Pin替代:THC63LVD83D、DS90C385、DTC34LF85L

◇MS90C385B兼容MS90C385!

◇頻率范圍:20-150MHz 時(shí)鐘信號(hào)

◇內(nèi)核供電電源 3.3V

◇IO供電電源1.8V、3.3V兼容

◇支持VGA、SVGA、XGA、SXGA,最大支持1440×1050@60Hz、1360×768@60Hz、1280×768@60Hz

◇支持?jǐn)U展頻譜時(shí)鐘產(chǎn)生

◇內(nèi)部集成輸入抖動(dòng)濾波器

◇減小LVDS擺幅來(lái)減小電磁干擾(200mV、345mV LVDS擺幅可供選擇)

◇PLL不需要外部結(jié)構(gòu)

◇遵循 TIA/EIA-644 LVDS 標(biāo)準(zhǔn)

三、MS90C385B、MS90C386B在JEIDA-VESA模式中的具體應(yīng)用

LVDS信號(hào)模式有兩種: JEIDA與VESA。 LCD屏老一點(diǎn)的有6Bit的,現(xiàn)在普通的是8Bit,新的就是10Bit了,每個(gè)clock周期內(nèi)7bit數(shù)據(jù)(跟TMDS標(biāo)準(zhǔn)有差別)。

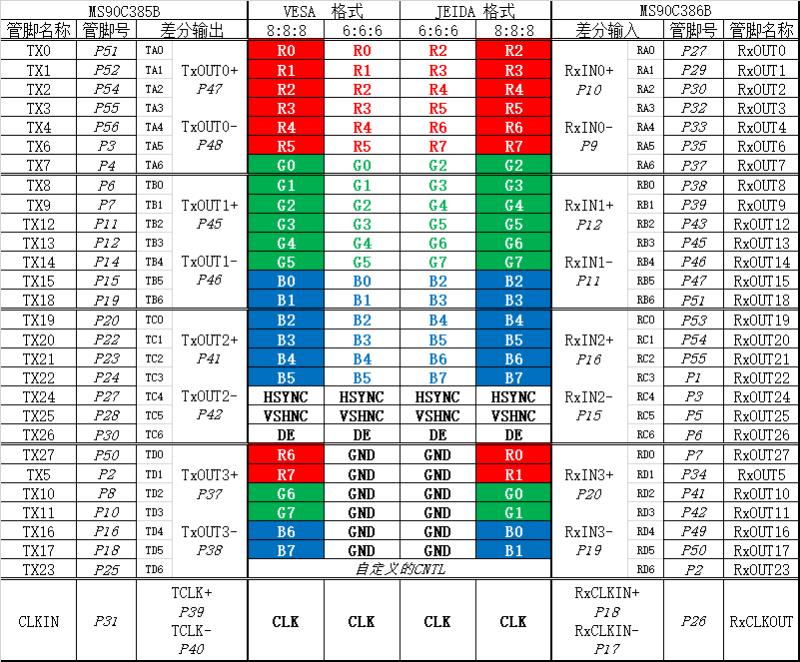

本篇以我公司代理的1Port LVDS發(fā)送(Tx)MS90C385B及接受(Rx)MS90C386B為例詳解,我們根據(jù)電子產(chǎn)品CPU定義的JEIDA(或VESA)及輸出的RGB565、RGB666、RGB888視頻格式對(duì)MS90V385B、MS90C386B數(shù)據(jù)引腳作對(duì)應(yīng)調(diào)整, JEIDA 、VESA模式的RGB數(shù)據(jù)對(duì)應(yīng)的LVDS轉(zhuǎn)換IC Pin腳參見(jiàn)下表。

MS90C385B MS90C386B之JEIDA VESA模式引腳對(duì)應(yīng)RGB數(shù)據(jù)表

(注意:上圖展示MS90C385B 6:6:6為連接18bit顯示屏之Pin對(duì)應(yīng)關(guān)系)

以連接18bit顯示(即6Bit屏)及主板顯示輸出18bit/24bit、3Lane_LVDS為例,詳解JEIDA、VESA模式下MS90C386B、MS90C385B對(duì)應(yīng)引腳連接方法:

1、MS90C386B之RGB666輸出引腳連接

1.1、VESA格式下之高位引腳空置:RGB666之高位(R6 R7 G6 G7 B6 B7)對(duì)應(yīng)Pin腳7、34、41、42、49、50懸空(建議接地),屏驅(qū)動(dòng)軟件按VESA模式高位RGB數(shù)據(jù)(R6 R7 G6 G7 B6 B7)不使用配置,啟用R0 R1 R2 R3 R4 R5 G0 G1 G2 G3 G4 G5 B0 B1 B2 B3 B4 B5 Hsync Vsync DE ,對(duì)應(yīng)MS90C386B Pin腳為27 29 30 32 33 35 37 38 39 43 45 46 47 51 53 54 55 1 3 5 6腳 ,無(wú)用Pin腳接地,防止電磁干擾!

1.2、JEIDA格式下之低位引腳空置:RGB666之低位(R0 R1 G0 G1 B0 B1)對(duì)應(yīng)Pin腳7、34、41、42、49、50懸空(建議接地),與上述1.1懸空引腳一致!屏驅(qū)動(dòng)軟件按JEIDA模式低位RGB數(shù)據(jù)(R0 R1 G0 G1 B0 B1)不使用配置,啟用R2 R3 R4 R5 R6 R7 G2 G3 G4 G5 G6 G7 B2 B3 B4 B5 B6 B7 Hsync Vsync DE ,對(duì)應(yīng)MS90C386B Pin腳分別為27 29 30 32 33 35 37 38 39 43 45 46 47 51 53 54 55 1 3 5 6腳 ,與上述1.1對(duì)應(yīng)引腳一致!無(wú)用Pin腳接地。

1.3、RGB666視頻格式下,LVDS差分輸入僅用3組:JEIDA、VESA格式下3Lane數(shù)據(jù)LVDS輸入與RGB666輸出對(duì)應(yīng)引腳一致,具體參考上面圖表“MS90C385B MS90C386B之JEIDA VESA模式引腳對(duì)應(yīng)RGB數(shù)據(jù)表”,即啟用3Lane LVDS輸入數(shù)據(jù)RxIN0±、RxIN1±、RxIN2±,對(duì)應(yīng)引腳分別為10-9、12-11、16-15,還有1Lane輸入時(shí)鐘RxCLKIN±, 對(duì)應(yīng)引腳18-17。

第4Lane LVDS RxIN3±不用(P20-P19),但需按以下電路連接:

2、MS90C385B連接18bit LVDS顯示之RGB666輸入引腳連接

2.1、VESA格式下之高位引腳空置:RGB666之高位(R6 R7 G6 G7 B6 B7)對(duì)應(yīng)Pin腳50、2、8、10、16、18懸空(建議接地),屏驅(qū)動(dòng)軟件按VESA模式高位RGB數(shù)據(jù)(R6 R7 G6 G7 B6 B7)不使用配置,啟用R0 R1 R2 R3 R4 R5 G0 G1 G2 G3 G4 G5 B0 B1 B2 B3 B4 B5 Hsync Vsync DE ,對(duì)應(yīng)MS90C385B Pin腳為51 52 54 55 56 3 4 6 7 11 12 14 15 19 20 22 23 24 27 28 30腳,無(wú)用Pin腳接地,防止電磁干擾!

2.2、JEIDA格式下之低位引腳空置:RGB666之低位(R0 R1 G0 G1 B0 B1)對(duì)應(yīng)Pin腳50、2、8、10、16、18懸空(建議接地),與上述2.1項(xiàng)懸空引腳一致!屏驅(qū)動(dòng)軟件按JEIDA模式低位RGB數(shù)據(jù)(R0 R1 G0 G1 B0 B1)不使用配置,啟用R2 R3 R4 R5 R6 R7 G2 G3 G4 G5 G6 G7 B2 B3 B4 B5 B6 B7 Hsync Vsync DE ,對(duì)應(yīng)MS90C385B Pin腳分別為51 52 54 55 56 3 4 6 7 11 12 14 15 19 20 22 23 24 27 28 30腳 ,與上述2.1項(xiàng)對(duì)應(yīng)引腳一致!無(wú)用Pin腳接地。

2.3、在18bit LVDS顯示之RGB666視頻格式下,LVDS差分輸出僅用3組:JEIDA、VESA格式下3Lane數(shù)據(jù)LVDS輸出與RGB666輸入對(duì)應(yīng)引腳一致,具體參考上面圖表“MS90C385B MS90C386B之JEIDA VESA模式引腳對(duì)應(yīng)RGB數(shù)據(jù)表”,即僅用3Lane LVDS輸出數(shù)據(jù)TxOut0±、TxOut1±、TxOut2±,對(duì)應(yīng)引腳分別為47-48、45-46、41-42,還有1Lane輸出時(shí)鐘TCLK±, 對(duì)應(yīng)引腳39-40。第4Lane LVDS TxOut3±懸空不用(P37、P38),建議該P(yáng)in接地。

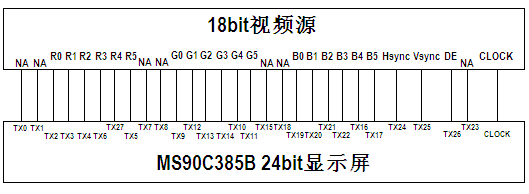

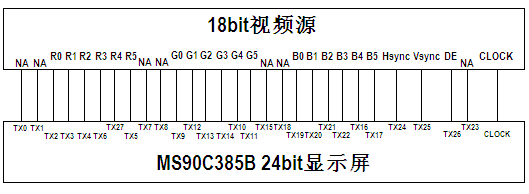

2.4、視頻源為18bit(RGB666),而輸出顯示屏為24bit時(shí):MS90C385B之TX0(P51)、TX1(P52)、TX7(P4) 、TX8(P6)、TX15(P15)、TX18(P19)懸空或接地,這是MS90C385B應(yīng)用特殊點(diǎn),切記!具體如下圖所示:

3、MS90C385B、MS90C386B 在RGB888 之VESA、JEIDA模式下Pin連接方法則按上面圖表“MS90C385B MS90C386B之JEIDA VESA模式引腳對(duì)應(yīng)RGB數(shù)據(jù)表”對(duì)應(yīng)連接即可,這里不再詳細(xì)說(shuō)明。

4、MS90C385B MS90C386B在RGB565格式之輸入_輸出引腳連接

MS90C386B之RGB565格式輸入LVDS與輸出RGB引腳連接與本篇上述1.1-1.3項(xiàng)應(yīng)用一致,不同點(diǎn)為:JEIDA模式下R2、B2對(duì)應(yīng)之引腳27、47腳懸空不用,無(wú)用引腳接地。VESA模式下R5、B5對(duì)應(yīng)之引腳35 、1腳懸空不用,無(wú)用引腳接地。

MS90C385B之RGB565格式輸入RGB與輸出LVDS引腳連接與本篇上述2.1-2.3項(xiàng)應(yīng)用一致,不同點(diǎn)為:JEIDA模式下R2、B2對(duì)應(yīng)之引腳51、15腳懸空不用,無(wú)用引腳接地。但有客戶(hù)將R2(P51腳)與R7(P3腳)連接,將B2(P15腳)與B7(P24腳)連接事例。VESA模式下R5、B5對(duì)應(yīng)之引腳3、24腳懸空不用,無(wú)用引腳接地。

四、LVDS信號(hào)PCB Layout注意事項(xiàng)

1、LAYOUT時(shí),差分信號(hào)輸出端,幾組線必須等長(zhǎng)、等寬(8mil-10mil), 且阻抗必須控制在每對(duì)線100Ω。

2、電源需分成3組LVDS,Logic,PLL,其三組電源必須分開(kāi)LAYOUT。

3、地不需分割,分割反而不好。

5、接收端之LVDS必須于每對(duì)線終端(靠LVDS腳位處)各接100Ω電阻(即MS90C386)。

6、輸入訊號(hào)端串聯(lián)一個(gè)終端電阻為20Ω-40Ω(建議值)連接至信號(hào)端再串接一個(gè)電容(其電容值取決于EMC的頻率,其建議值為100PF~400PF)。

7、RGB信號(hào)線,其盡可能要等長(zhǎng)、等寬,不然也不可以差太多,否則信號(hào)會(huì)受影響。

8、CLOCK和信號(hào)線Fan out時(shí),其最好可以等長(zhǎng)、等寬,若無(wú)法等長(zhǎng)、等寬,也不能差距太多,否則輸出訊號(hào)品質(zhì)會(huì)很差。

9、CLOCK走線兩邊包GND,其作用在于避免串音到其它信號(hào),若無(wú)包地,與其它信號(hào)必須至少留3倍線寬的間距。

10、LAYOUT時(shí),若正反面擺件時(shí),須注意正面要擺放ANALONG及高頻的零件 ,而背面則放置低頻的零件,例如: LAYER1.ANALONG/高頻零件, LAYER2.GND , LAYER3.VCC , LAYER4.低頻零件。

11、電源腳須接上濾波電容,不可將濾波電容距離IC電源腳太遠(yuǎn),否則沒(méi)有慮波效果。

12、重要的信號(hào)腳預(yù)留連接IC電源(Vcc)之電阻位置(如Clock引腳)。

13、LVDS LAYOUT時(shí), 須獨(dú)立出一塊(中間挖空),上下走線,其中間不走任何信號(hào)線。

14、CONNECTOR(中間挖空),上下走線,其中間不走任何信號(hào)線,其做用在于防打靜電及EMI。

15、信號(hào)頻率較高的信號(hào)線與信號(hào)頻率較低的信號(hào)線(約相差100KHZ)平行走線時(shí),此二線中間需加GND trace或Plane(平面,層)避免串音發(fā)生。高電壓(高電流)與低電壓(低電流)的信號(hào)線平行走線時(shí),此二線中間亦需加GND Trace 或Plane(平面,層),避免串音發(fā)生。

-

電源

+關(guān)注

關(guān)注

184文章

17712瀏覽量

250098 -

lvds

+關(guān)注

關(guān)注

2文章

1043瀏覽量

65804

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

MS90C385B——+3.3V 145MHz 的 24bit 平板顯示器(FPD) LVDS 信號(hào)發(fā)送器

采用ds90c385a + ds90ub927q + ds90ub940傳輸顯示視頻,屏幕無(wú)法正常顯示怎么解決?

DS90C385A用18位RGB對(duì)LVDS屏有什么影響?

DS90C385A想實(shí)現(xiàn)RGB565輸入LVDS 4組輸出,如何實(shí)現(xiàn)?

MS90C031——LVDS 四通道總線驅(qū)動(dòng)器

MS-A2836URAH1C規(guī)格書(shū)

MS320C5517器件的功耗估算和功耗摘要

DS90CR216A、SN65LVDS84A、DS90CR286A、SN75LVDS83x

DS90C385A +3.3V可編程LVDS發(fā)射器24位平板顯示器鏈路數(shù)據(jù)表

DS90C383B可編程LVDS發(fā)射機(jī)24位平板顯示器(FPD)鏈路數(shù)據(jù)表

DS90C032B LVDS四路CMOS差分線路接收器數(shù)據(jù)表

DS90C031B LVDS四路CMOS差分線路驅(qū)動(dòng)器數(shù)據(jù)表

DS90C363B可編程LVDS發(fā)射器18位平板顯示器(FPD)鏈路數(shù)據(jù)表

MS90C385B與MS90C386B功能特點(diǎn)及應(yīng)用詳解

MS90C385B與MS90C386B功能特點(diǎn)及應(yīng)用詳解

評(píng)論