對于DDR4的設計,相信攻城獅們經歷過萬千項目的歷練,肯定是很得心應手,應該已經有自己的獨門技巧了。比如選擇合適的拓撲結構,信號同組同層,容性負載補償,加上拉電阻等等。但是對于時序方面的控制,理論上只有一個辦法——繞等長,速率越高的DDR4,等長控制越嚴格,從±100mil,到±50mil,甚至±5mil……

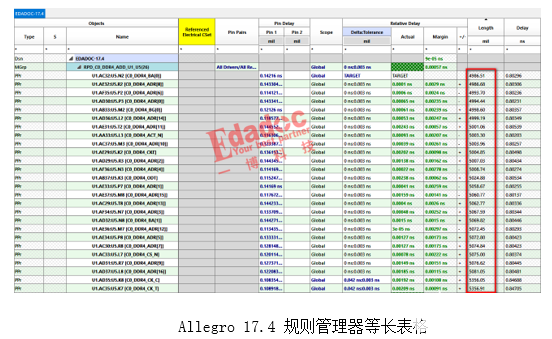

一個平平無奇的日子,網紅芬帶著新合作的客戶項目經理李工來找我,客戶對我們做某FPGA DDR4設計要求有疑問,說我給的等長規則不對,為啥要按時間設置等長,以及他看到規則管理器的長度差很大,其中時鐘和地址信號長度明顯超過了手冊spec要求,以前用P軟件設計從來沒有出現這樣的問題。緊接著李工急促說道:“我們設計的DDR4項目本來就運行不到2400Mbps,找你們debug優化設計,就是信任你們的品牌,你們這樣做設計讓我感覺很不專業,我們項目很重要……”

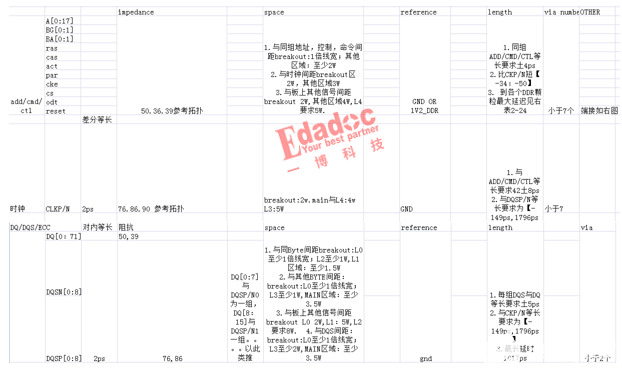

某FPGA等長要求

對于李工個中艱辛自不必多說,我們相當明白他的痛點。我問道:“李工你們對于DDR4換層過孔的補償在P軟件是如何考量的?pin delay是怎樣設置的?表層布線和內層布線長度一樣,就是時序一樣了嗎?”李工當場就愣住了!

高速先生以前說過,等長從來都不是目的,DDRx系統要求的是等時,除了差分對內的等時是為了相位之外,絕大多數的等時都是為了時序!現在流行重要的事情說三遍:等時,等時,等時!那如何保證我們的DDR4 PCB設計是等時的呢?大致可以按照下面的操作步驟來。

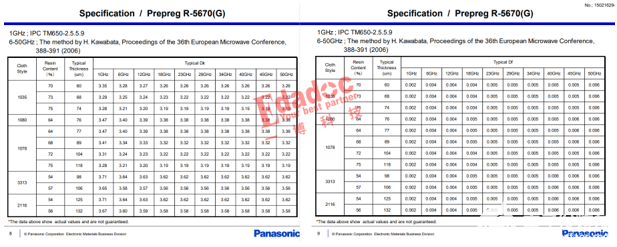

做等長第一步是要設置準確的層疊參數,介質厚度和Dk。在設計過程中我們需要將設計層疊發送給板廠做加工層疊確認和備料。加工備料層疊如下圖所示:

根據備料層疊按照材料手冊來設置相關的介質厚度和Dk/Df參數:

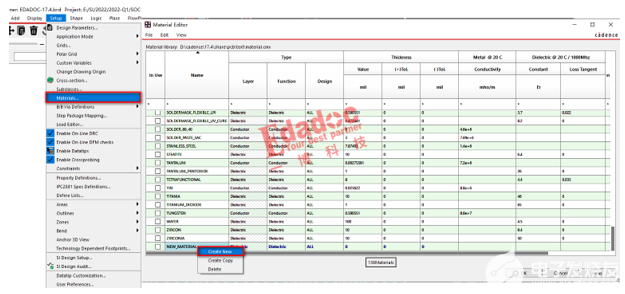

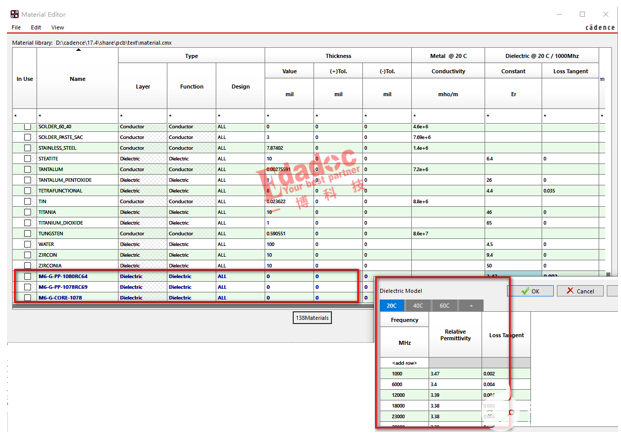

點擊Setup菜單欄下方-Materials,即可以打開allegro自帶的材料參數表,由于我們使用M6-G材料需要自定義增加相關材料參數,選中表格點擊右鍵即可增加自定義的材料參數。

自定義一個自己使用習慣的名字,既可設置不同頻率下的Dk/Df,也可設置不同溫度下的Dk/Df,相關數據設置如下所示:

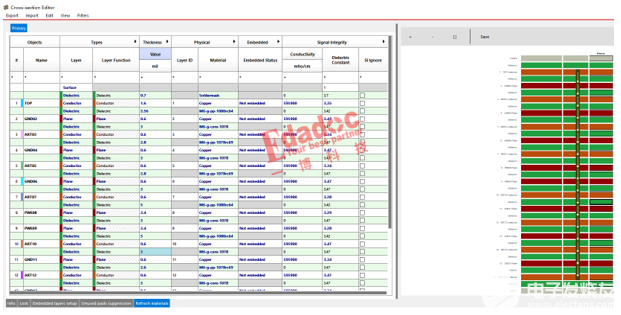

設置好材料參數之后,就可以打開層疊將相關參數設置好,這樣我們對于層疊部分的設置就基本完成了,如下所示:

接著就可以導入Pin delay和設置等長規則了,我們的網紅芬就是按照上述操作設置的相關規則。

審核編輯:劉清

-

PCB設計

+關注

關注

394文章

4691瀏覽量

85865 -

DDR4

+關注

關注

12文章

322瀏覽量

40835

發布評論請先 登錄

相關推薦

關于DDR4的繞等長,您想知道的都有

關于DDR4的繞等長,您想知道的都有

評論