隨著集成電路芯片向亞3納米技術節點邁進,晶體管中關鍵尺寸不斷微縮,帶來更高的開關速度和集成度,但也會導致短溝道效應,嚴重影響晶體管性能,摩爾定律正逼近物理極限,這使得業界亟需開發新材料和新架構。原子級厚度的高遷移率二維半導體將取代傳統硅鍺,成為備選溝道材料,而柵介質的等效氧化層厚度(equivalent oxide thickness,EOT)也需微縮至0.5納米以下。如何有效地將高遷移率二維半導體與高介電常數柵介質集成并極限微縮(EOT<0.5納米)是電子學領域的一個重要挑戰。近日,北京大學彭海琳課題組建立了高遷移率二維半導體Bi2O2Se的紫外光輔助插層氧化方法,實現了新型自然氧化物單晶柵介質β-Bi2SeO5的可控制備,其介電常數高達22,絕緣性能優異。二維Bi2O2Se/Bi2SeO5基頂柵場效應晶體管的柵介電層EOT可微縮至0.41納米,突破了二維電子器件超薄柵介質集成這一瓶頸。相關研究成果以“亞0.5納米等效氧化層厚度的二維半導體單晶自然氧化物柵介質”(A single-crystalline native dielectric for two-dimensional semiconductors with an equivalent oxide thickness below 0.5 nm)為題,于2022年9月15日在線發表在《自然-電子學》(Nature Electronics)。

集成電路芯片中晶體管的關鍵尺寸在摩爾定律的推動下不斷微縮。當晶體管中半導體溝道長度小于6倍特征長度(λ)時,會發生閾值電壓漂移、漏電流增大等短溝道效應,制約了晶體管進一步向亞3納米技術節點微縮。如公式λ=

所示,這一特征長度λ與晶體管的有效柵極數目(n)、半導體溝道厚度(tb)與介電常數(εb),以及柵介質的厚度(tox)與介電常數(εox)直接相關。因而,業界計劃使用原子級厚度的高遷移率二維半導體材料取代傳統硅鍺作為溝道材料,同時需將柵介質的等效氧化層厚度(equivalent oxide thickness,EOT)微縮至0.5納米以下,來減小特征長度λ以抑制短溝道效應。

然而,將高遷移率二維半導體與高介電常數的柵介質有效集成并極限微縮是電子學領域的一個重要挑戰。目前,商用硅基集成電路中所用的柵介質為原子層沉積法(ALD)制備的氧化鉿(HfO2),其在二維半導體無懸掛鍵的范德華表面難以均勻沉積,無法形成連續薄膜。而與二維半導體兼容的柵介質,如六方氮化硼(hBN)、氟化鈣(CaF2)、有機緩沖層復合的HfO2等,由于介電常數較低、絕緣性不足等原因,EOT僅能微縮至0.9納米水平。因此,二維電子學領域亟需開發與二維半導體兼容的亞0.5納米EOT的柵介質。

北京大學化學與分子工程學院彭海琳教授課題組前期開發了新型高遷移率二維半導體Bi2O2Se(Nature Nanotechnology 2017, 12, 530),并對其氧化轉化及自然氧化物介電層進行了深入研究。首次發現通過熱氧化(Nature Electronics 2020, 3, 473)或等離子體氧化(Nano Letters 2020, 20, 7469),二維Bi2O2Se表面可形成具有高介電常數(21~22)和較好絕緣性能的自然氧化物柵介質Bi2SeO5(多晶或無定型相),并基于二維Bi2O2Se/Bi2SeO5構筑了高性能的場效應晶體管器件和邏輯門電路(Acc. Mater. Res. 2021, 2, 842-853),其柵介質的EOT可微縮至0.9納米水平。

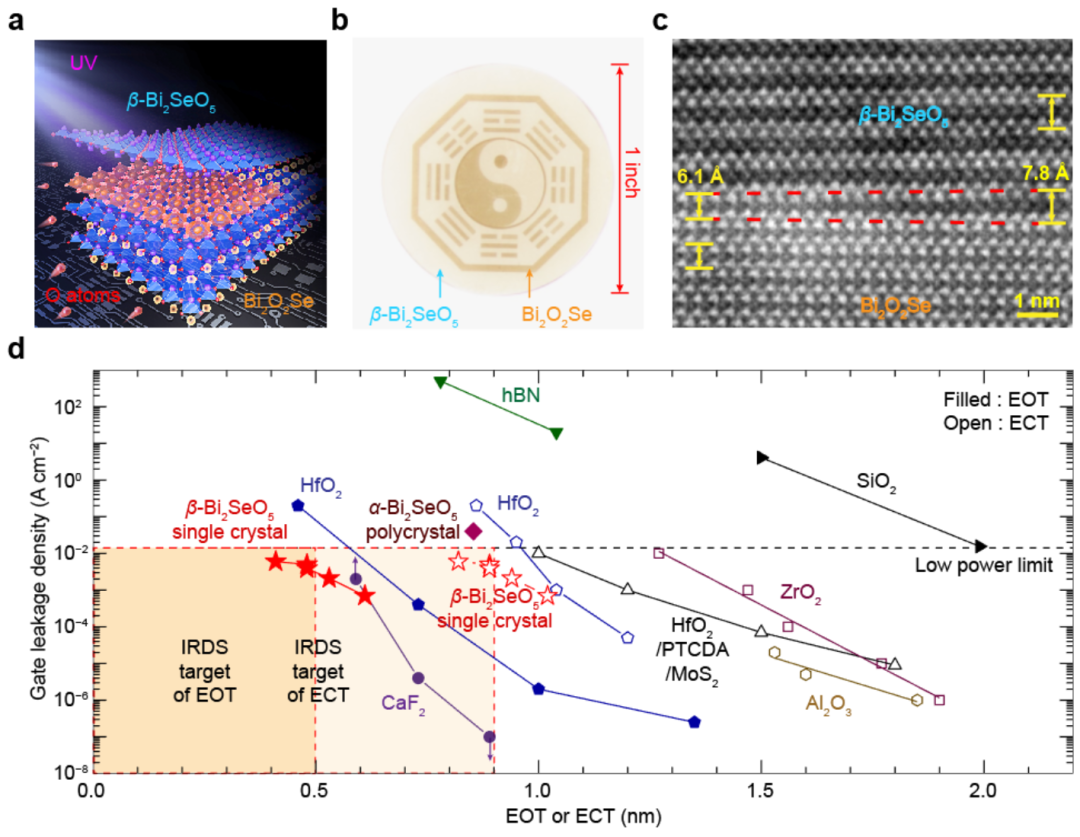

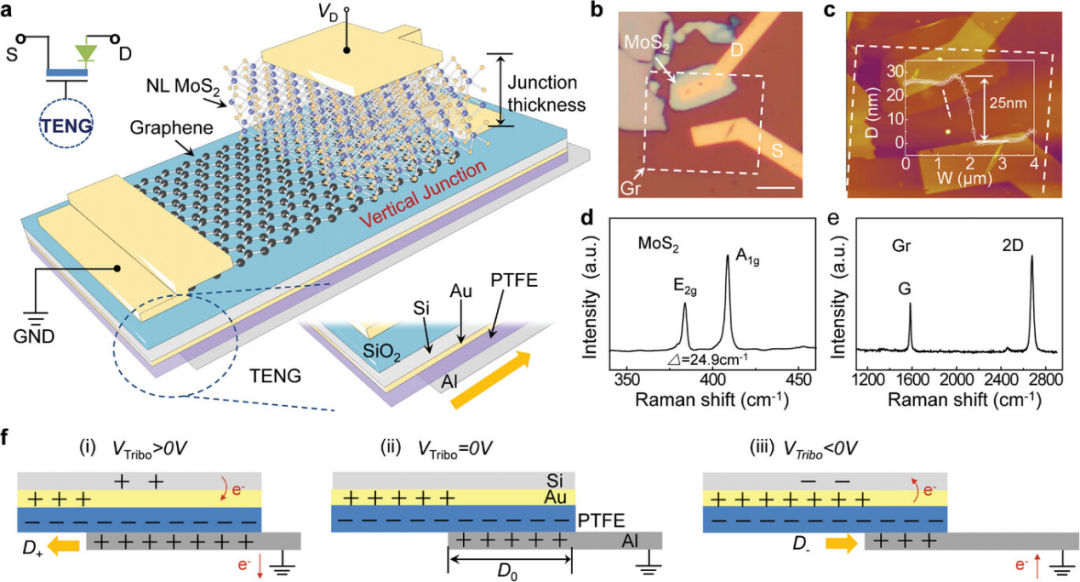

最近,彭海琳教授課題組從二維半導體Bi2O2Se的拉鏈形層狀結構受到啟發,借鑒二維材料插層化學,建立了Bi2O2Se的紫外光輔助插層氧化方法(圖1a),保持其Bi-O層狀骨架結構不變,將二維半導體Bi2O2Se原位轉化為單晶氧化物柵介質β-Bi2SeO5。這是繼先前熱氧化工作制得的多晶α-Bi2SeO5介電層之后,Bi2O2Se自然氧化物的另一種物相。這種紫外光輔助插層氧化方法可與紫外光刻技術相兼容,借助特制的光刻掩模版,可實現晶圓級樣品的區域選擇性氧化(圖1b)。二維Bi2O2Se可被逐層可控插層氧化,并形成原子級平整、晶格匹配的高質量半導體/介電層界面(圖1c)。

單晶β-Bi2SeO5可用作二維Bi2O2Se基晶體管的理想柵介質。掃描微波阻抗顯微鏡表征和電容-電壓測量表明,單晶β-Bi2SeO5具有高達22且不受厚度影響的面外介電常數。除具有高質量界面和高介電常數以外,β-Bi2SeO5柵介質還因其層狀單晶結構而具有優良的絕緣性。原位插層氧化構筑的二維Bi2O2Se/Bi2SeO5頂柵場效應晶體管表現出優良的電學性能:室溫遷移率可高達427cm2/Vs,回滯可低至20~60 mV,亞閾值擺幅(SS)可低于65 mV/dec,接近理論值60 mV/dec。更重要的是,柵介質β-Bi2SeO5即使薄至3層(2.3納米),EOT低至0.41納米,在1 V柵壓下的漏電流依然低于0.015A/cm2,滿足業界低功耗器件對柵介質的要求。

單晶柵介質β-Bi2SeO5在漏電流滿足業界低功耗器件要求的同時,等效氧化層厚度可以微縮到滿足業界要求的亞0.5納米水平,相對于商用HfO2、hBN、CaF2、熱氧化多晶α-Bi2SeO5等各種柵介質,在等效厚度與絕緣性方面均具有優勢(圖1d)。該項研究成果彌補了二維半導體在超薄柵介質集成方面的短板,對二維電子器件的發展具有重要意義。

圖1.單晶自然氧化物柵介質β-Bi2SeO5的制備與性質。(a)二維Bi2O2Se紫外光輔助插層氧化轉化為單晶柵介質β-Bi2SeO5示意圖;(b)晶圓級區域選擇性制備二維Bi2O2Se/Bi2SeO5異質結;(c)二維Bi2O2Se/Bi2SeO5異質結界面結構;(d)β-Bi2SeO5的等效厚度(EOT:等效氧化層厚度;ECT:等效電容厚度)及絕緣性與其他柵介質的對比。

該研究成果于2022年9月15日在線發表在《自然-電子學》(Nature Electronics 2022, https://doi.org/10.1038/s41928-022-00824-9)。北京大學化學與分子工程學院彭海琳教授為該論文的通訊作者,第一作者為北京大學化學與分子工程學院博士研究生張亦弛。其他主要合作者還包括德州大學奧斯汀分校物理系賴柯吉教授、北京大學物理學院高鵬教授等。Nature Electronics期刊每期會挑選論文邀請作者撰寫研究簡介(Research Briefing),與研究論文同期在線刊出,方便讀者更好地理解重要成果。彭海琳教授和張亦弛同學代表論文作者發表了題為“Producing ultrathin monocrystalline native oxide dielectrics for 2D transistors(為二維晶體管制備超薄單晶自然氧化物介電層)”的研究簡介,簡要介紹了此項研究的背景、過程、發現和意義。

該研究工作得到了國家自然科學基金委、科技部、北京分子科學國家研究中心、騰訊基金會等機構的資助,并得到了北京大學化學與分子工程學院分子材料與納米加工實驗室(MMNL)儀器平臺的支持。

論文原文鏈接:

https://www.nature.com/articles/s41928-022-00824-9

審核編輯 :李倩

-

半導體

+關注

關注

334文章

27290瀏覽量

218102 -

晶體管

+關注

關注

77文章

9682瀏覽量

138084

原文標題:北京大學《Nature Electronics》:突破瓶頸,0.5 nm以下!

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

193nm紫外波前傳感器(512x512高相位分辨率)助力半導體/光刻機行業發展!

氧化鎵探測器性能指標及測試方法

電子科普!什么是激光二極管(半導體激光器)

紫外光源的分類

如何通過霍爾效應測量半導體中電子和空穴的遷移率?

SiC MOSFET溝道遷移率提升工藝介紹

CG2H80015D氮化鎵(GaN)高電子遷移率晶體管(HEMT)規格書

n型硅太陽能電池組件產品的紫外光衰(UVID)及可靠性評估

二維材料 ALD 的晶圓級集成變化

Atomic QRCode2 Base | ATOM系列新寵!一維/二維碼掃碼神器

膠體量子點和二維材料異質結光電探測器應用綜述

天津大學團隊開創石墨烯半導體新紀元

高遷移率二維半導體Bi2O2Se的紫外光輔助插層氧化方法

高遷移率二維半導體Bi2O2Se的紫外光輔助插層氧化方法

評論