“bins”是在功能覆蓋率coverpoint中收集設計特性用的。

功能覆蓋率覆蓋的就是一個個的coverpoint bins(不同的變量),對于一個8bit addr,那么默認的bins就是8‘h00~8’hFF,當然也可以顯式地指定不同值之間的切換為一個bins。

從這個角度來理解,coverpoint bins非常容易理解,但是涉及到具體的應用還是會有很多問題需要考慮的。

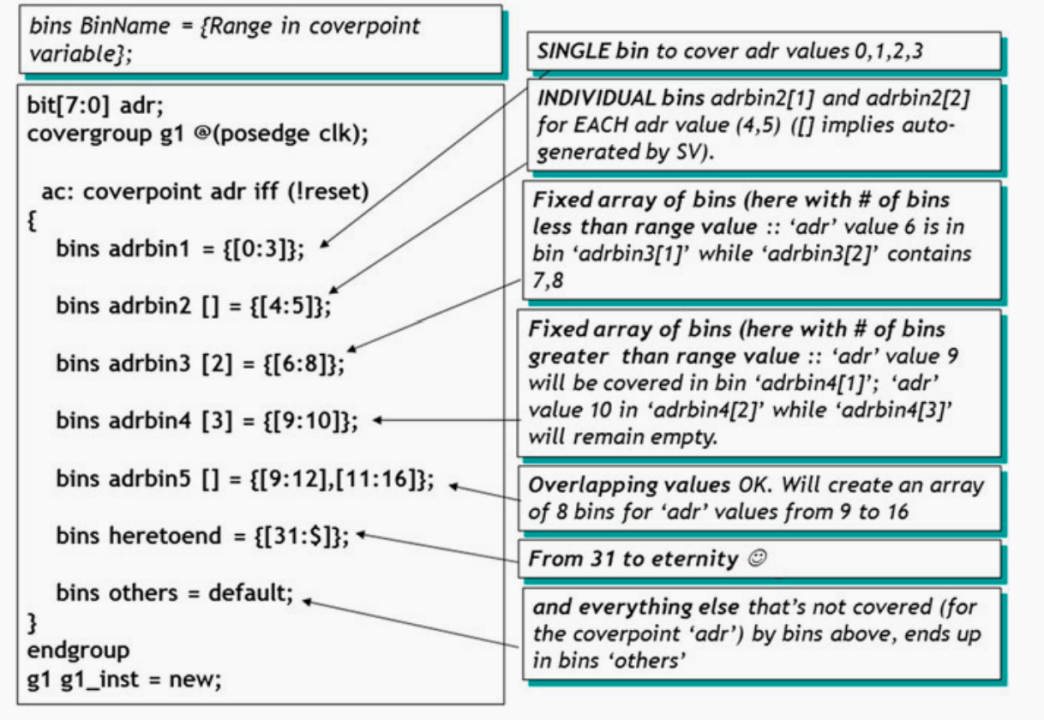

例如,在下面的聲明中,將創建多少個bins?

bins adrbin1 = {[0:3]};

16個、4個還是1個。

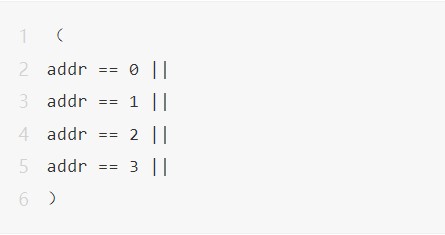

答案是1個bin,相當于覆蓋了

注意上面的寫法' bins adrbin1 '沒有[]括號。換句話說,' bins adrbin1 '不會為' addr '值{[0:3]}自動創建4個bins,而是只創建1個bins來覆蓋值' 0 ',' 1 ',' 2 ',' 3 '。

也就是說,只要覆蓋了0~3其中的一個,這個coverpoint覆蓋率就是100%

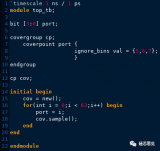

但是,如果你希望分別收集變量“adr”的每個值,該怎么辦呢。應該按照下面的這種寫法,加上“[]”

binsadrbin2[]={[4:5]};

這時候會為4、5分別創建一個bins,只有4和5全部覆蓋,這個coverpoint的覆蓋率才是100%

在開發SV功能覆蓋率模型時可能沒有辦法把所有的值都寫滿,這個時候可以利用符號“$”,很多語義下它都代表著無限大的意思。對于一個8bit addr變量

bins adr[] = {[31:$]}

就意味著顯式地收集{[31:255]}

審核編輯:劉清

-

Verilog

+關注

關注

28文章

1351瀏覽量

110148 -

變量

+關注

關注

0文章

613瀏覽量

28404

原文標題:什么是systemverilog bins?

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

[啟芯公開課] SystemVerilog for Verification

round robin 的 systemverilog 代碼

做FPGA工程師需要掌握SystemVerilog嗎?

SystemVerilog Assertion Handbo

SystemVerilog的斷言手冊

SystemVerilog的正式驗證和混合驗證

怎樣去使用SystemVerilog中的Static方法呢

從Verilog PLI到SystemVerilog DPI的演變過程

SystemVerilog里的regions以及events的調度

ignore_bins和default兩者之間有些什么細微差別呢?

systemverilog bins是如何去定義的

systemverilog bins是如何去定義的

評論