1. 應用背景

靜態時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設計的要求,根據電路網表的拓撲結構,計算并檢查電路中每一個DFF(觸發器)的建立和保持時間以及其他基于路徑的時延要求是否滿足。STA作為FPGA設計的主要驗證手段之一,不需要設計者編寫測試向量,由軟件自動完成分析,驗證時間大大縮短,測試覆蓋率可達100%。

靜態時序分析的前提就是設計者先提出要求,然后時序分析工具才會根據特定的時序模型進行分析,給出正確是時序報告。

進行靜態時序分析,主要目的就是為了提高系統工作主頻以及增加系統的穩定性。對很多數字電路設計來說,提高工作頻率非常重要,因為高工作頻率意味著高處理能力。通過附加約束可以控制邏輯的綜合、映射、布局和布線,以減小邏輯和布線延時,從而提高工作頻率。

2. 理論分析

2.1 靜態時序分析的理論基礎知識

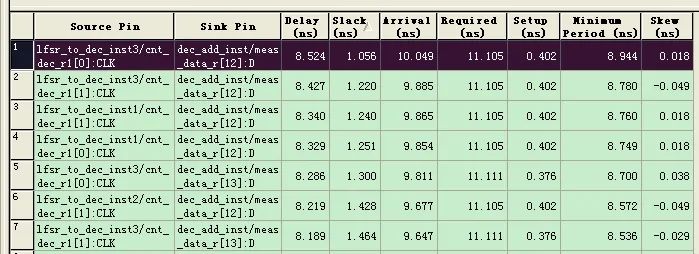

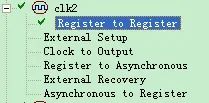

在進行正確的時序分析前,我們必須具備基本的靜態時序的基本知識點,不然看著編譯器給出的時序分析報告猶如天書。如圖3.1所示,為libero軟件給出的寄存器到寄存器模型的時序分析報告的截取,接下來我們會弄清楚每個欄目的數據變量的含義,以及計算方法。

圖3.1 libero靜態時序分析報告

2.1.1 固定參數launch edge、latch edge、Tsu、Th、Tco概念

1. launch edge

時序分析起點(launch edge):第一級寄存器數據變化的時鐘邊沿,也是靜態時序分析的起點。

2. latch edge

時序分析終點(latch edge):數據鎖存的時鐘邊沿,也是靜態時序分析的終點。

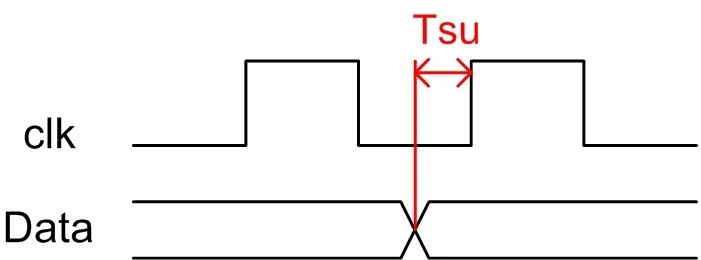

3. Clock Setup Time (Tsu)

建立時間(Tsu):是指在時鐘沿到來之前數據從不穩定到穩定所需的時間,如果建立的時間不滿足要求那么數據將不能在這個時鐘上升沿被穩定的打入觸發器。如圖3.2所示:

圖3.2 建立時間圖解

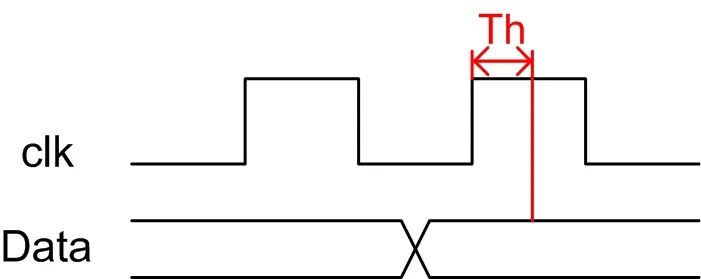

4. Clock Hold Time (Th)

保持時間(Th):是指數據穩定后保持的時間,如果保持時間不滿足要求那么數據同樣也不能被穩定的打入觸發器。保持時間示意圖如圖3.3所示:

圖3.3 保持時間圖解

5. Clock-to-Output Delay(tco)

數據輸出延時(Tco):這個時間指的是當時鐘有效沿變化后,數據從輸入端到輸出端的最小時間間隔。

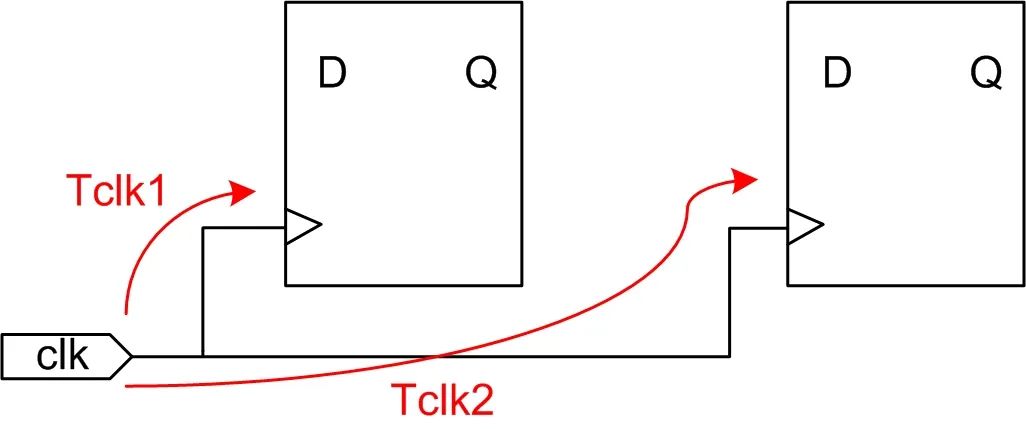

2.1.2 Clock skew

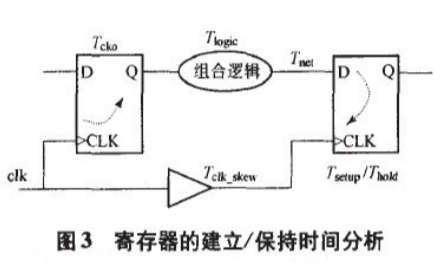

時鐘偏斜(clock skew):是指一個時鐘源到達兩個不同寄存器時鐘端的時間偏移,如圖3.4所示:

圖3.4 時鐘偏斜

時鐘偏斜計算公式如下:

Tskew = Tclk2 - Tclk1(公式3-1)

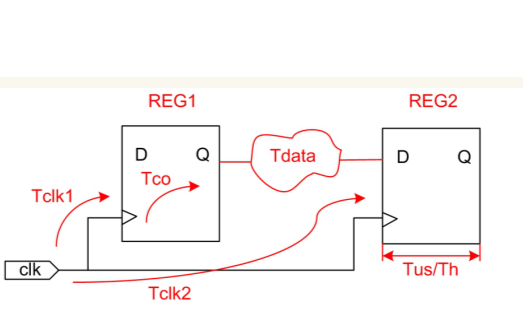

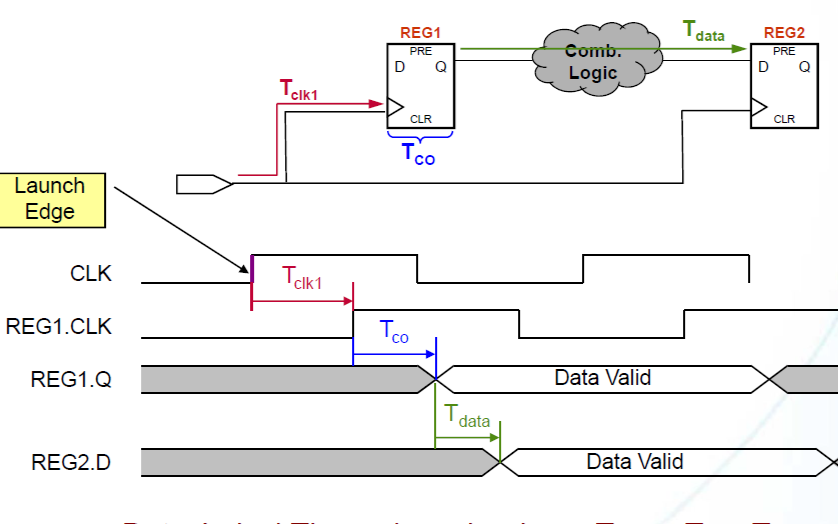

2.1.3 Data Arrival Time

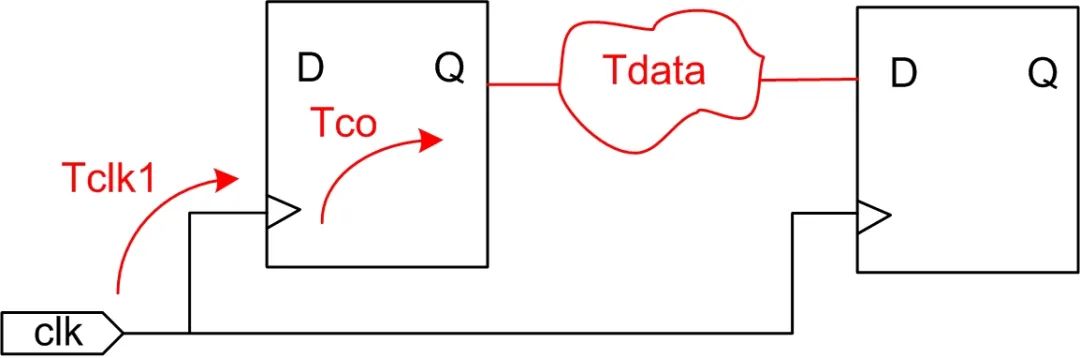

數據到達時間(Data Arrival Time):輸入數據在有效時鐘沿后到達所需要的時間。主要分為三部分:時鐘到達寄存器時間(Tclk1),寄存器輸出延時(Tco)和數據傳輸延時(Tdata),如圖3.5所示

圖3.5 數據到達時間

數據到達時間計算公式如下:

Data Arrival Time = Launch edge + Tclk1 +Tco + Tdata(公式3-2)

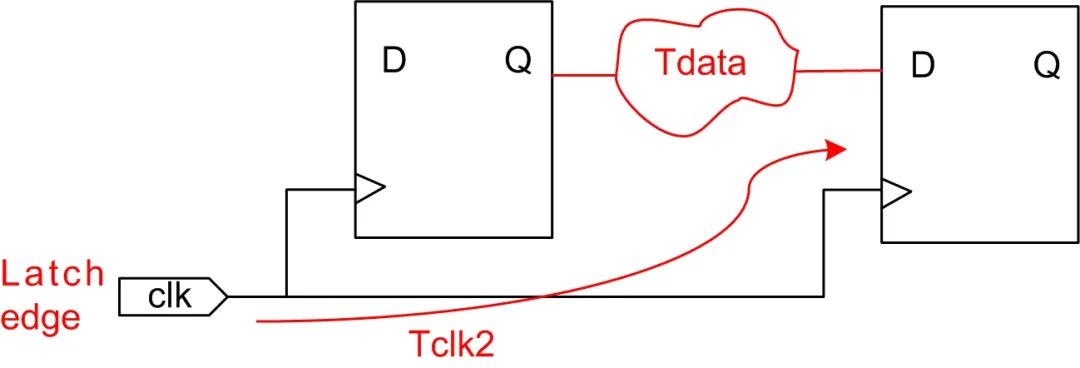

2.1.4 Clock Arrival Time

時鐘到達時間(Clock Arrival Time):時鐘從latch邊沿到達鎖存寄存器時鐘輸入端所消耗的時間為時鐘到達時間,如圖3.6所示

圖3.6 時鐘到達時間

時鐘到達時間計算公式如下:

Clock Arrival Time = Lacth edge + Tclk2(公式3-3)

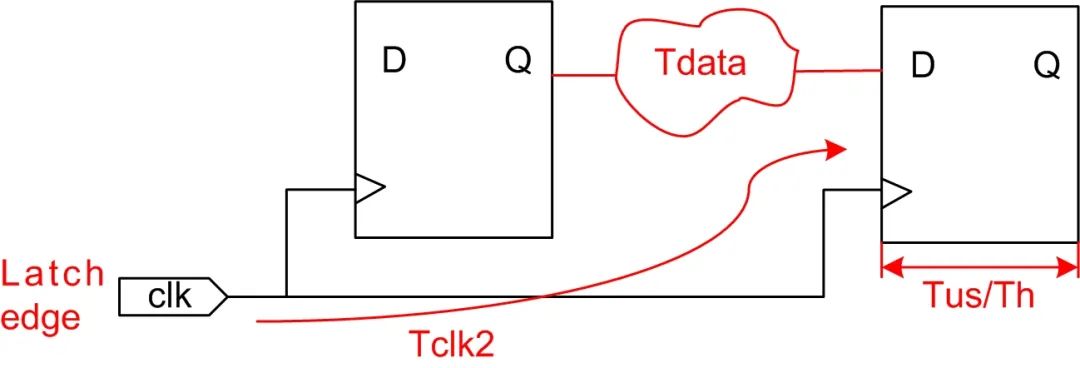

2.1.5 Data Required Time(setup/hold)

數據需求時間(Data Required Time):在時鐘鎖存的建立時間和保持時間之間數據必須穩定,從源時鐘起點達到這種穩定狀態需要的時間即為數據需求時間。如圖3.7所示:

圖3.7 數據需求時間

(建立)數據需求時間計算公式如下:

Data Required Time = Clock Arrival Time - Tsu(公式3-4)

(保持)數據需求時間計算公式如下:

Data Required Time = Clock Arrival Time + Th (公式3-5)

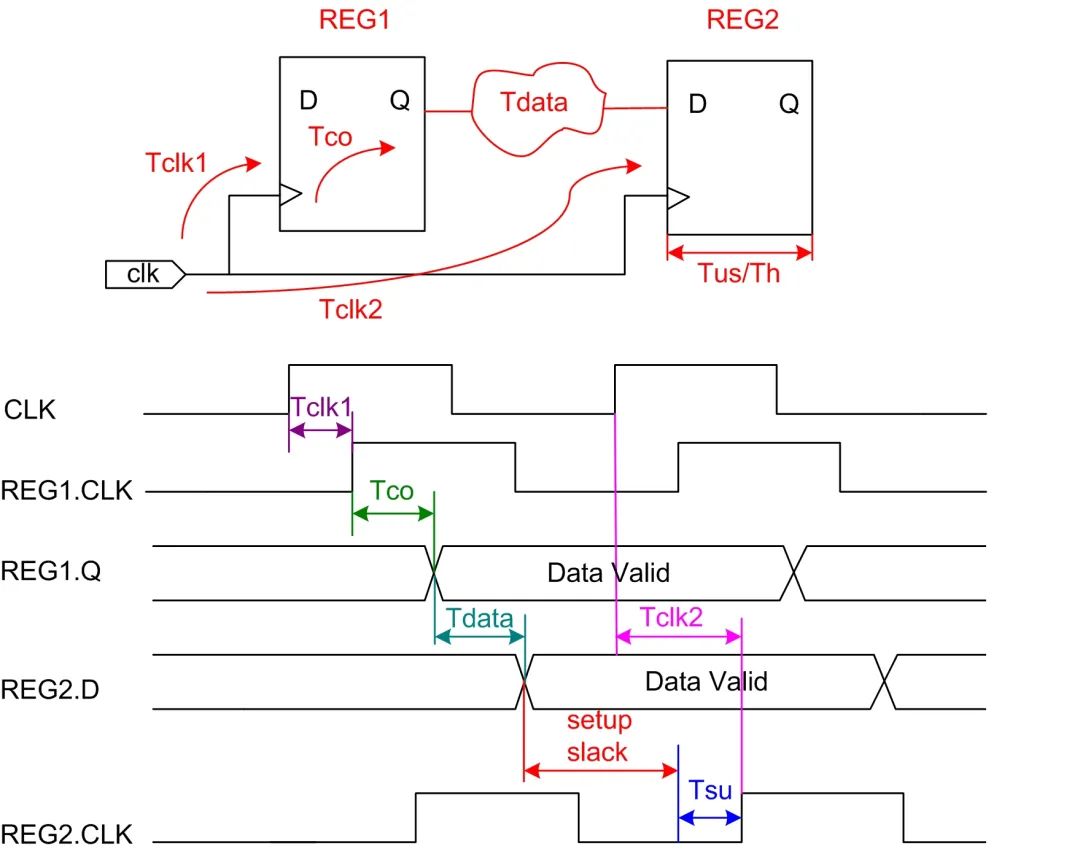

2.1.6 Setup slack

建立時間余量(setup slack):當數據需求時間大于數據到達時間時,就說時間有余量,Slack是表示設計是否滿足時序的一個稱謂。

圖3.8 建立時間余量

如圖3.8所示,建立時間余量的計算公式如下:

Setup slack = Data Required Time - Data Arrival Time(公式3-6)

由公式可知,正的slack表示數據需求時間大于數據到達時間,滿足時序(時序的余量),負的slack表示數據需求時間小于數據到達時間,不滿足時序(時序的欠缺量)。

2.1.7 時鐘最小周期

時鐘最小周期:系統時鐘能運行的最高頻率。

1. 當數據需求時間大于數據到達時間時,時鐘具有余量;

2. 當數據需求時間小于數據到達時間時,不滿足時序要求,寄存器經歷亞穩態或者不能正確獲得數據;

3. 當數據需求時間等于數據到達時間時,這是最小時鐘運行頻率,剛好滿足時序。

從以上三點可以得出最小時鐘周期為數據到達時間等于數據需求時間,的運算公式如下:

Data Required Time = Data Arrival Time(公式3-7)

由上式推出如下公式:

Tmin + Latch edge + Tclk2 - Tsu = Launch edge + Tclk1 + Tco + Tdata

最終推出最小時鐘周期為:

Tmin = Tco + Tdata + Tsu -Tskew(公式3-8)

3. 應用分析

3.1 設置時鐘主頻約束

所有的靜態時序分析都是在有約束的情況下編譯器才給出分析報告,所以進行時序分析的第一步就是設置約束。

Libero軟件設置時鐘約束的途徑三種,單時鐘約束,多時鐘約束和在Designer里面進行約束。

3.1.1 單時鐘約束

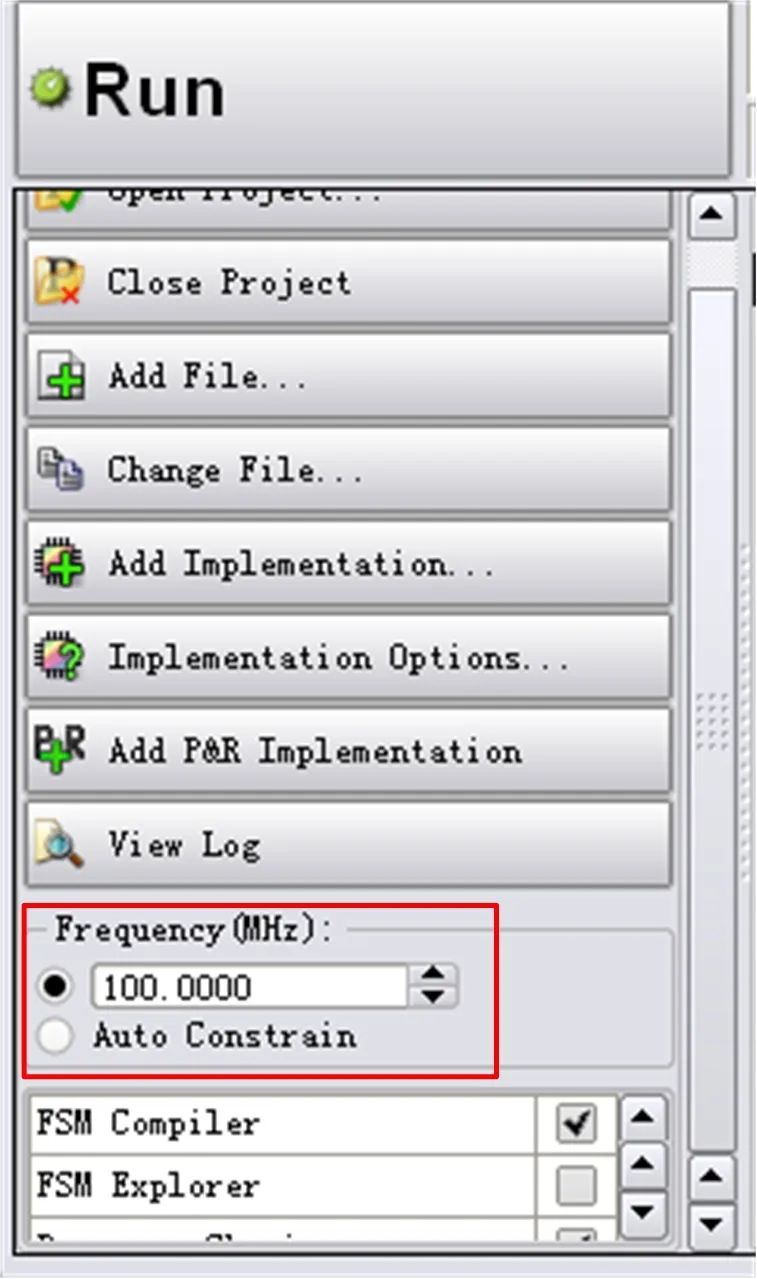

有時我們系統所有模塊都采用同一個時鐘,這種方式最為簡單,直接在Synplify主界面上有個設置時鐘約束的,如圖4.1中紅框所示:

圖4.1 單時鐘設置

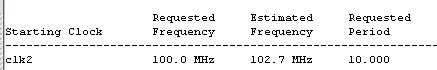

設置完成后,編譯,通過Synplify時鐘報告看初步時鐘運行頻率能否達到要求,時鐘報告如圖4.2所示,設定100Mhz,能運行102.7Mhz,滿足時序。

圖4.2 時序報告

3.2 多時鐘約束

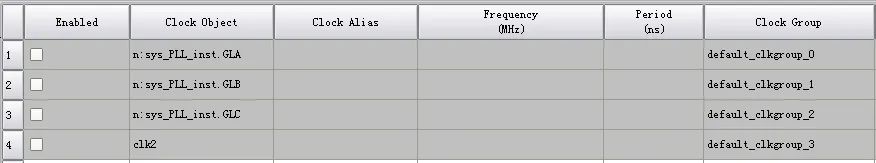

當系統內部模塊采用了多個時鐘時,那就需要進行多時鐘約束了。首先需要打開設置界面,在Synplify中選擇:File->New->Constraint File建立SDC文件,選擇時鐘約束如圖4.3所示:

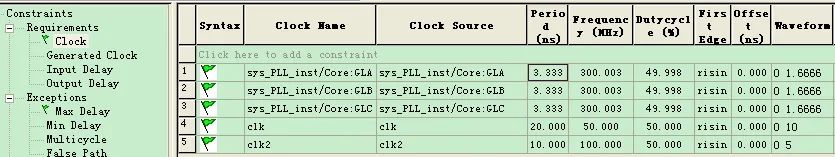

圖4.3 多時鐘約束

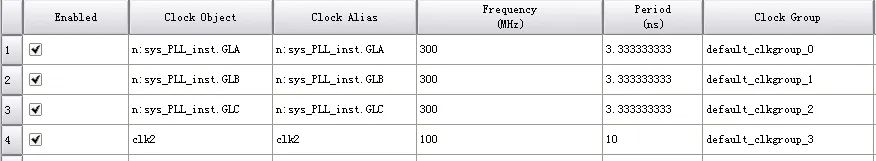

對時鐘進行如下約束后保存SDC文件,約束如圖4.4所示

圖4.4 多時鐘約束完成

3.3 Designer SmartTime時鐘約束

時鐘約束除了在Synplify中可以約束外,還可以在Designer SmartTime中設置時鐘約束,打開Designer Constraint,選擇Clock進行針對每個使用時鐘的設置,如圖4.5所示:

圖4.5 Designer時序約束

4.4 時序報告分析

3.4.1 Synplify時序報告

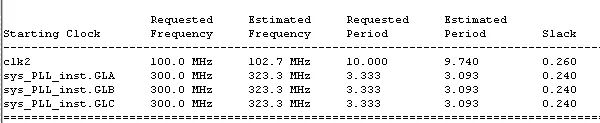

當約束了時序后,需要觀察時序報告,看時鐘能否達到我們需要的時鐘,首先觀察Synplify綜合報告。以多時鐘約束為例子,從Synplify得到的時序報告如圖4.6所示:

圖4.6 多時鐘約束時序報告

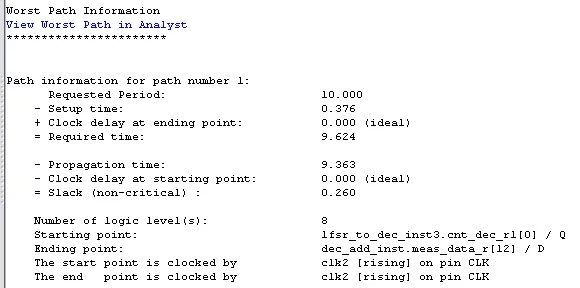

由上圖可知時序都滿足約束,未出現違規,可以在下面的報告中查看最差路徑,如圖4.7所示是clk2的最差路徑。

圖4.7 最差路徑

3.4.2 Designer SmartTime時序分析報告

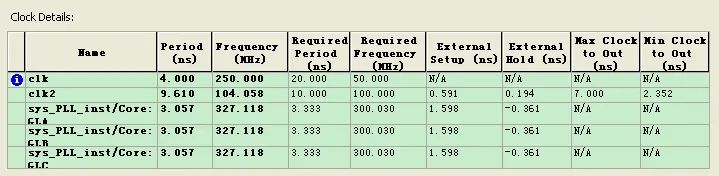

當設計經過Synplify綜合給出網表文件后,還需要Designer進行布局布線,通過布局布線優化后的時序會有變化,因此,還需要分析布局布線后的時序,打開Designer->Timing Analyzer查閱整體時序分析報告如圖4.8所示:

圖4.8 布局布線后時序報告

由Synplify綜合后的報告和Designer進行布局布線后的報告可以看出,布局布線后優化了一些時序,特別是clk2時鐘,通過布局布線后優化到了184Mhz,完全滿足時序。

3.4.3 詳細時序報告圖

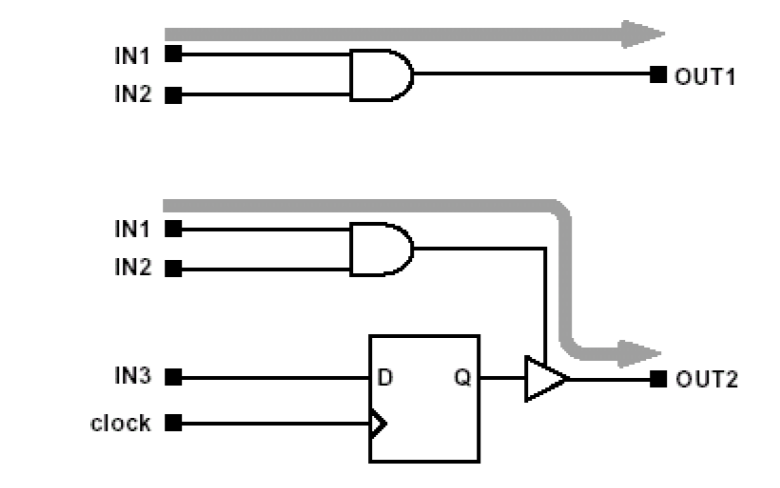

通過Synplify綜合后的和Designer進行布局布線都只是看到了一個大體的時序報告,當我們需要分析時序時候必須觀察仔細的時序報告,在SmartTime中提供這種報告功能,以clk2分析為例,在Timing Analyzer找到如下區域。

圖4.9 時序報告選擇

如圖4.9所示,選擇寄存器到寄存器進行分析時鐘主頻。

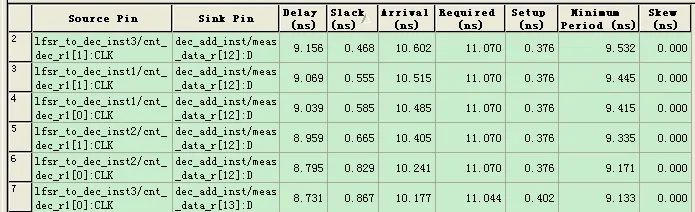

圖4.10 寄存器到寄存器分析

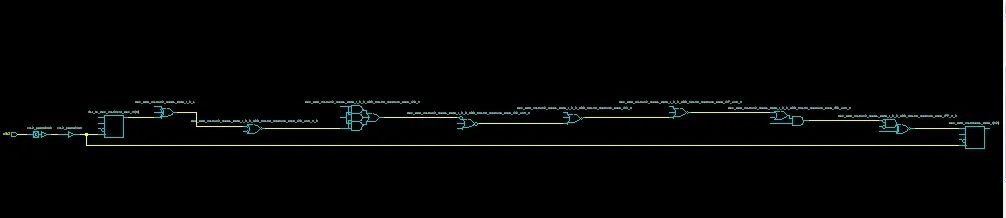

如圖4.10所示,時序報告中給出了數據延時,時序余量,數據到達時間,數據需求時間,數據建立時間,以及最小周期和時鐘偏斜等信息,有了上一節的時序分析基礎知識,我們完全能看懂這些數據代表的意義,這樣對我們時序分析就知己知彼,進一步雙擊其中一條路徑,還會給出這條路徑的硬件電路圖,如圖4.11所示,有了這些詳細的時序報告,對設計進行調整更加清晰。

圖4.11 硬件路徑

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21967瀏覽量

614268 -

STA

+關注

關注

0文章

52瀏覽量

19234 -

靜態時序分析

+關注

關注

0文章

29瀏覽量

9667

原文標題:FPGA靜態時序分析模型——寄存器到寄存器

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA quartus ii里的靜態時序分析

使用pt對fpga進行靜態時序分析需要哪些文件

靜態時序分析在高速 FPGA設計中的應用

FPGA進行靜態時序分析

評論