某年某月某日

我在知乎看到了多bit信號跨時鐘的問題,于是整理了一下自己對于跨時鐘域信號的處理方法。

1,fifo

數據的話,直接用fifo

2,使用賽靈思原語XPM(Xilinx Parameterized Macros)

打開vivado -- tools -- language_templates,里面直接搜索XPM,相關的原語里會注釋相應的用法和參數配置,對于不同場景的跨時鐘,有不同的原語。

同步復位,XPM_CDC_SYNC_RESET

異步復位,XPM_CDC_ASYNC_RESET

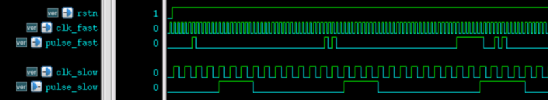

脈沖信號,XPM_CDC_PULSE

單bit信號(電平信號),XPM_CDC_SINGLE

單bit信號數組,xpm_cdc_array_single

(這個用得較多,官方說數組的每1bit需不相關,即可以把多個不相關的單bit信號拼起來,用一個原語,甚至可以是上百bit位寬。

除了不相關的單bit信號,同一個多bit信號我也經常使用此原語,這種信號一般是跨時鐘域的參數,在下發后保持不變,這樣有助于時序收斂。)

格雷碼同步器,利用了格雷碼單次只能跳變1位的特性,要求輸入的數據是累加1或者累減1的數據,本質上是單比特跨時鐘域處理,xpm_cdc_gray

握手機制的跨時鐘域總線數據同步,XPM_CDC_HANDSHAKE

3,只要是正確處理了跨時鐘域的問題,也可以不用xpm,直接使用set_false,但xpm是賽靈思官方認可的跨時鐘處理,處理后不會有時序問題出現在時序報告中。

-

數據

+關注

關注

8文章

7002瀏覽量

88942 -

時鐘

+關注

關注

10文章

1733瀏覽量

131446 -

XPM

+關注

關注

0文章

12瀏覽量

8670 -

時鐘域

+關注

關注

0文章

52瀏覽量

9535

原文標題:vivado時序-多bit信號跨時鐘域

文章出處:【微信號:FPGA通信小白成長之路,微信公眾號:FPGA通信小白成長之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

看看Stream信號里是如何做跨時鐘域握手的

基于FPGA的跨時鐘域信號處理——MCU

關于跨時鐘域信號的處理方法

關于跨時鐘域信號的處理方法

評論