4.系統及存儲器架構

華大電子MCU CIU32F011x3、CIU32F031x5器件是基于 ARM Cortex M0處理器的 32位通用微控制器存儲器芯片。采用了哈佛結構,具有低中斷延遲時間和低成本調試特性,而且高集成度和增強的特性使這顆處理器

適合于那些需要高性能和低功耗微控制器的市場領域。預先定義的存儲器映射和高達 4GB的存儲空間,充分保證了系統的靈活性和可擴展性。

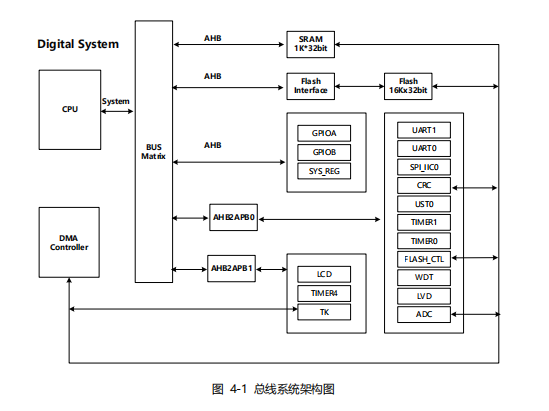

4.1.系統架構

華大電子MCU CIU32F011x3、CIU32F031x5器件采用 32位多層總線結構,該結構可使系統中的多個主機和從機之間的并行通信成為可能。多層總線結構包括一個 AHB互聯矩陣、兩個 AHB總線和兩個 APB總線。AHB互聯矩陣的互聯關系接下來將進行說明。

CIU32F011x3、CIU32F031x5主系統由以下兩部分構成

? 2個驅動單元

– CPU內核系統總線(S-bus)

– DMA總線

? 2個存儲單元

– 內部閃存存儲器

– 內部 SRAM

系統總線

此總線連接 CPU內核的系統總線(外設總線)到總線矩陣,總線矩陣協調著內核和各個高速部件間的訪問。

DMA控制器

此總線將 CPU與各外設模塊訪問相聯競爭,協調訪問優先級,仲裁等。

總線矩陣(Bus Matrix)

? 總線矩陣管理著內核系統總線與各外設模塊的訪問仲裁,總線矩陣由主模塊總線及從模塊總線組成。

? AHB外設通過總線矩陣與系統總線相連。

? AHB到 APB橋(AHB2APB bridges-APB)。

? AHB到 APB橋在 AHB與 APB總線間提供同步連接。

注:當對 APB寄存器進行 8位或者 16位訪問時,該訪問會被自動轉換成 32位的訪問;橋會自動將 16位或者 8位的數據擴展以配合 32位的寬度。

4.2.存儲器映射

此 32位處理器采用同一套總線來讀取指令和加載/存儲數據。指令代碼和數據都位于相同的存儲器地址空間,但在不同的地址范圍。程序存儲器,數據存儲器,寄存器和 IO端口都在同一個線性的 4GB的地址空間之內。這是 32位處理器的最大地址范圍,因為它的地址總線寬度是 32位。此外,為了降低不同客戶在相同應用時的軟件復雜度,存儲映射是按 32位處理器提供的規則預先定義的。在存儲器映射表中,一部分地址空間由 32位處理器的系統外設所占用,且不可更改。此外,其余部分地址空間可由芯片供應

商定義使用。CIU32F011x3、CIU32F031x5器件的存儲器映射表顯示了 CIU32F011x3、CIU32F031x5器件的存儲器映射,包括代碼、SRAM、外設和其他預先定義的區域。簡化了每個外設的地址譯碼。

審核編輯 黃昊宇

-

mcu

+關注

關注

146文章

17141瀏覽量

351077 -

存儲器

+關注

關注

38文章

7487瀏覽量

163798

發布評論請先 登錄

相關推薦

TMS320F28002x、TMS320F280015x和TMS320F280013x之間的遷移指南

從MSP430F12x(2)遷移到MSP430F21x2 MCU

使用MSP430F522x和MSP430F521x器件進行設計

【GD32 MCU 移植教程】9、從 STM32F10x 系列移植到 GD32F30x 系列

MSP430F677x、MSP430F676x、MSP430F674x多相位計量SoC數據表

MSP430F677x1、MSP430F676x1、MSP430F674x1多相位計量SoC數據表

TMS320F280x、TMS320C280x、TMS320F2801x數字信號處理器數據表

MSP430F665x、MSP430F645x、MSP430F565x、MSP430F535x混合信號微控制器數據表

CC430F614x、CC430F514x、CC430F512x MSP430? SoC數據表

MSP430F15x, MSP430F16x, MSP430F161x混合信號微控制器數據表

MSP430F471x3,MSP430F471x6, MSP430F471x7混合信號微控制器數據表

MSP430F20x1,MSP430F20x2,MSP430F20x3混合信號微控制器數據表

MSP430F14x、MSP430F14x1、MSP430F13x混合信號微控制器數據表

華大電子MCU-CIU32F011x3、CIU32F031x5系統及存儲器架構

華大電子MCU-CIU32F011x3、CIU32F031x5系統及存儲器架構

評論