我們學習一下Systemverilog中的有符號數據類型的賦值。

module top; logic [7:0] r1; logic signed [7:0] sr1; initial begin r1 = -2; $display($stime,,,"r1=%d",r1); sr1 = -2; $display($stime,,,"sr1=%d",sr1); r1 = r1+1; $display($stime,,,"r1=%d",r1); sr1 = sr1+1; $display($stime,,,"sr1=%d",sr1); end endmodule

Simulation log:

# run –all # 0 r1=254 # 0 sr1= -2 # 0 r1=255 # 0 sr1= -1 # exit

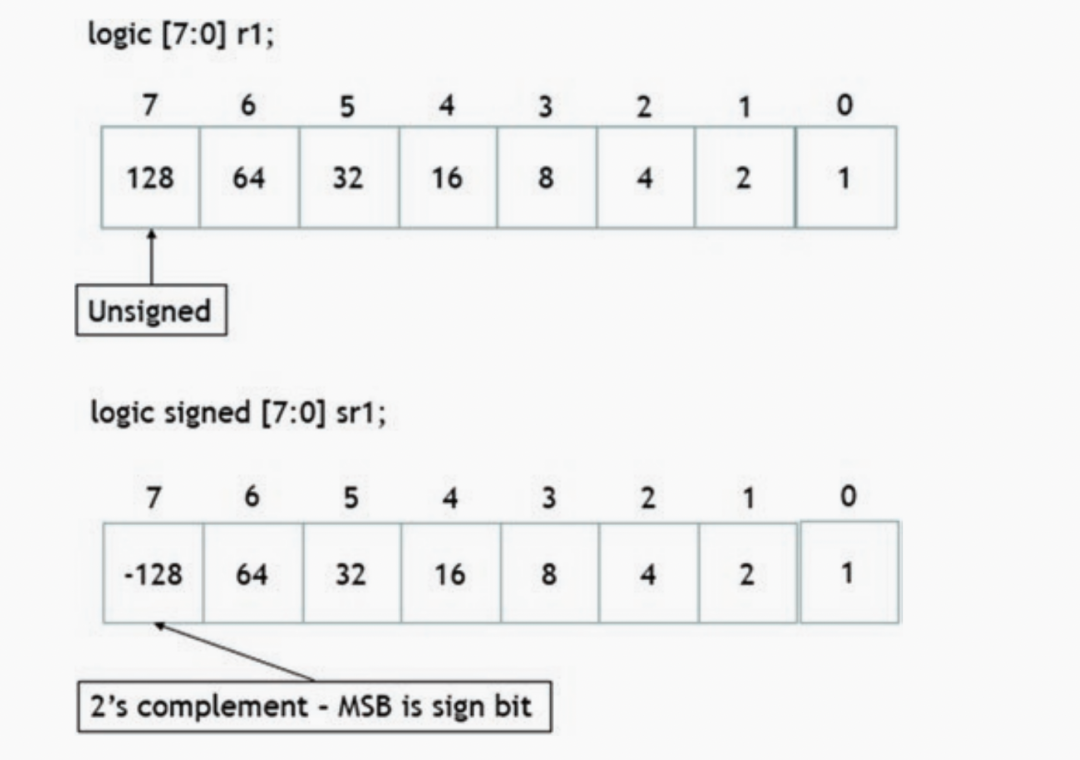

" r1 "被聲明為默認的無符號8位向量,而" sr1 "被聲明為有符號8位向量。

當我們賦值r1 =?2時,因為“r1”是無符號的,所以它實際上會拿到值254(相當于十進制數字?2)。但是“sr1”會拿到值?2。

當我們給“r1”加一個1時,它的計算結果是255(254 + 1)。當我們給“sr1”加一個1時,它的計算結果是- 1(?2 + 1)。

默認情況下,logic, reg, wire,input,output都是無符號的,但是也可以聲明為signed:

wire signed [7:0] w; module sm (input signed [7:0] iBus, output logic signed [7:0] oBus);

下面還有一些簡單的示例:

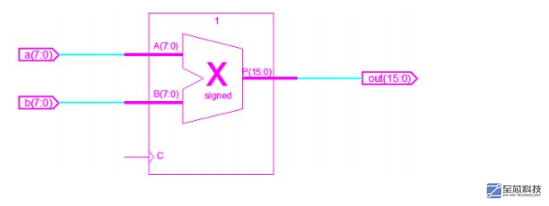

logic signed [3:0] sr = -1; ( sr = 4’sb1111) logic signed [7:0] sr1 = 1; (sr1 = 8’sb00000001) logic [7:0] adds = sr + sr1; ( adds = 8’b00000000) logic [7:0] usr = 1; logic signed [7:0] s_add; s_add = sr + usr; (s_add = 15+1 = 8’sb00010000) (signed + unsigned = unsigned; sr is treated as unsigned 15)

審核編輯:湯梓紅

-

Verilog

+關注

關注

29文章

1367瀏覽量

112359 -

System

+關注

關注

0文章

166瀏覽量

37904 -

數據類型

+關注

關注

0文章

237瀏覽量

13909

原文標題:SystemVerilog中的有符號數據類型

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

關于verilog中的無符號數和有符號數

采集的數據轉換成有符號數的問題

1.2FreeRTOS中的數據類型

Verilog 變量聲明與數據類型二

SpinalHDL的UInt與SInt數據類型能夠進行有符號/無符號數操作

是否可以使用ActiveX API獲取符號數據類型?

fpga 有符號數、無符號數

plc位、字節、字、雙字、有符號、無符號數據類型的關系

PLC數據類型

FreeRTOS使用的數據類型有哪些

Redis的數據類型有哪些

verilog中數據的符號屬性(有符號數和無符號數)探究根源

評論