Zynq的JTAG配置過程

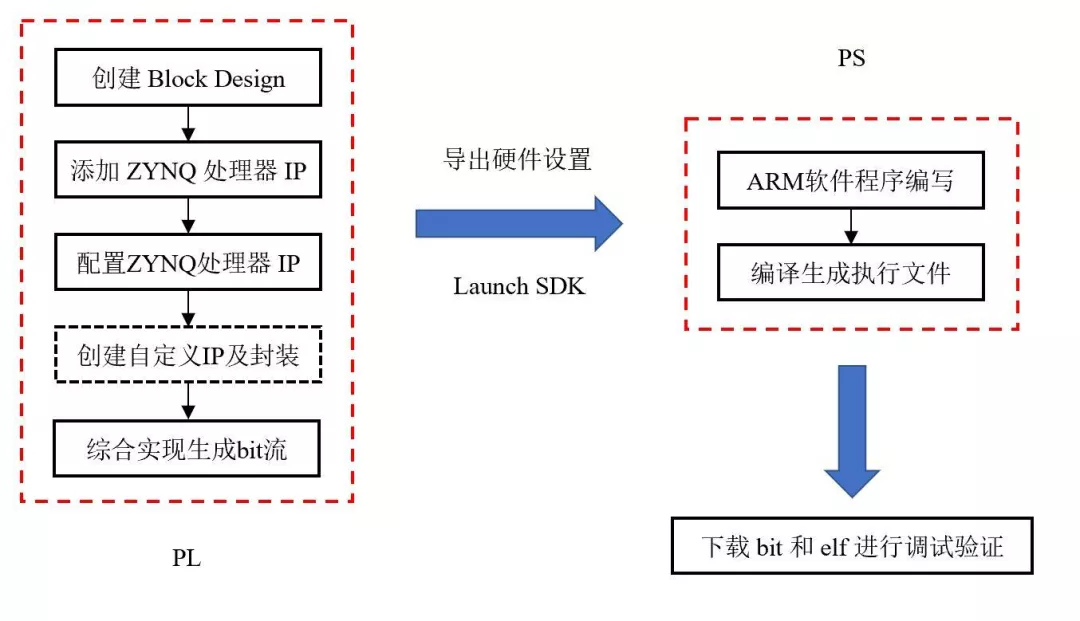

初學(xué) Zynq 的時候,我相信大家應(yīng)該和我一樣,都是按照慣例打開 Vivado 軟件,然后實現(xiàn) Zynq 可編程邏輯硬件部分PL的設(shè)置后,把硬件部署導(dǎo)出,再打開 SDK 進行 ARM 核的軟件部分 PS 編程設(shè)計,最后再將硬件比特流文件(.bit)和軟件的可執(zhí)行鏈接文件(.elf)下載到 Zynq 開發(fā)板中,這樣就可以對自己的軟硬件設(shè)計進行調(diào)試和驗證。這種設(shè)計方式可以用下面的圖很好的描述:

如上圖所示,這其實是剛接觸 Zynq 軟硬件設(shè)計時需要了解的最基本開發(fā)流程,也是PL和PS設(shè)計結(jié)合的完美體現(xiàn)。但是,上述開發(fā)的過程都有一個基本的前提,就是 Zynq 開發(fā)板是通過 JTAG 直接與電腦相連,然后實現(xiàn)程序的下載。從另一個角度來說,PL和PS的配置都可以認(rèn)為是電腦主機通過 JTAG 完成的。但是,在實際中,Zynq 開發(fā)板不可能實時與電腦連接,當(dāng) JTAG 不起作用時,Zynq 芯片是怎樣實現(xiàn)對自己的配置?這也是本文將要和大家共同討論的問題。

Zynq的啟動流程

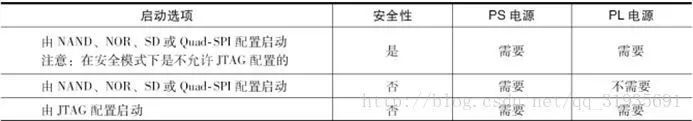

在無 JTAG 的模式下,Zynq 是通過片上CPU完成對芯片的配置,也就是PS和PL的配置是通過 PS 處理器 ARM 核來實現(xiàn)的。需要注意的是,與傳統(tǒng)的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持從 PL 端進行直接啟動配置的,一定要通過 PS 部分來完成。

Zynq 的具體啟動配置是分級進行的,一共可以分為3個階段,可以用0~2來表示:

Stage 0:BootROM 階段

Stage 1:FSBL (First Stage Boot loader)階段

Stage 2:SSBL (Second Stage Boot loader)階段

熟悉 ARM 開發(fā)的小伙伴應(yīng)該對上面的啟動過程感到很熟悉,但又有陌生的地方。不用急,下面對這三個階段進行詳細的分析。

Zynq啟動階段0——BootROM

階段0,又稱為 BootROM 階段。ROM 相信大家都知道,Read-Only Memory,只讀存儲器的意思;而 Boot 是引導(dǎo)的含義,所以 BootROM 從字面的意思來看,就是只能去讀取的引導(dǎo)存儲器。實際上,BootROM 的作用和它的字面意思完全一樣,就是指 ARM 核在上電之后,需要第一時間去讀取 BootROM 中固化的程序,完成對芯片的最初始化的配置。因為是只讀的,所以根據(jù) ROM 的性質(zhì),BootROM 中的程序是無法修改的。有的朋友會問BootROM 這一部分代碼主要完成了對 Zynq 的哪些配置?

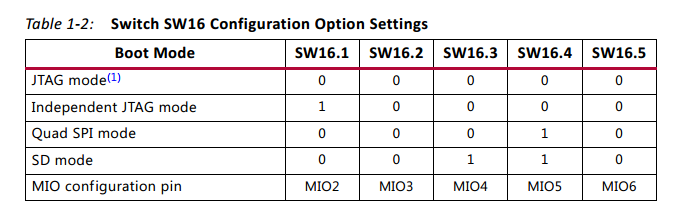

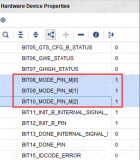

在具體說明 BootROM 進行哪些配置之前,先要描述一下關(guān)于 Zynq 的啟動引腳配置。Zynq 擁有5個可以進行配置的 MIO 引腳,是 MIO[6:2],在硬件形式上就表現(xiàn)為5個跳線帽,可以分別接 GND 或 3V3 的高電平。它們的作用如下:

MIO[2] :選擇 JTAG 模式

MIO[5:3] :選擇啟動方式,包括 SD 卡,QSPI Flash 等

MIO[6] :PLL 使能控制

通過不同的引腳作用說明可以發(fā)現(xiàn),當(dāng) JTAG 不起作用是,就需要通過改變 MIO[5:3] 的連接來實現(xiàn)從 SD 卡等不同的存儲介質(zhì)啟動。

而 BootROM 最重要的作用就是通過讀取 MIO[6:2] 的引腳配置情況,決定從何種介質(zhì)中加載階段1需要使用的啟動鏡像。當(dāng)然在加載之前,BootROM 會先完成對 SD 卡,NAND,NOR,QSPI Flash 等的初始化,從而使得ARM 核能夠成功訪問并使用這些外設(shè)。BootROM 在完成以上任務(wù)的同時,也會對安全模式等運行模式進行配置,這部分博主暫時不太了解,所以不做過多敘述。

BootROM 在從外部存儲設(shè)備讀取了啟動鏡像后,通常會把它進行加載到 OCM 中。OCM,On Chip Memory,是Zynq 中 ARM 內(nèi)核的片上存儲器,也叫片上內(nèi)存。自此之后,BootROM 階段的啟動任務(wù)就算是圓滿結(jié)束了,接下來 BootROM 階段就把控制權(quán)轉(zhuǎn)移到了階段1手中。

注:BootROM 階段不對 PL 進行配置

Zynq啟動階段1——FSBL

FSBL,(First Stage Boot Loader),就是 BootROM 加載到 OCM 中的啟動鏡像。FSBL 完成的任務(wù)是 Zynq 啟動過程中的關(guān)鍵一環(huán),可以分為以下4項:

完成 PS 的初始化

加載 PL 的bit流文件,完成 PL 配置

加載 SSBL 引導(dǎo)程序或是ARM的裸跑程序到 DDR

跳轉(zhuǎn)執(zhí)行 SSBL 或裸跑程序

FSBL 的任務(wù)如上所示,整個思路還是非常清晰的。第1步就是對 PS 端初始化,包括 DDR,MIO 等。第2步就是PL的配置,也就是傳統(tǒng)的 FPGA 下載 bit 流的過程,但要注意的是,在 Zynq 的非 JTAG 模式下,PL 是無法直接自行配置的。第3步是加載 SSBL 或裸跑程序到 DDR 內(nèi)存中,其中 SSBL,Second Stage Boot Loader,是在 Zynq 需要運行操作系統(tǒng)時才進行加載。而像我們?nèi)腴T學(xué)習(xí)時做的點亮 LED 燈實驗,就只是屬于裸跑程序。最后第4步,ARM 會跳轉(zhuǎn)到 DDR 中執(zhí)行所加載的程序。所以 FSBL 階段的運行思路是很好理解的。

Zynq啟動階段2——SSBL

SSBL 在 Zynq 的啟動過程中是可選的一個階段,就像所提到的點亮 LED 實驗,包括一些其他的比較小型的程序,如果不需要用到操作系統(tǒng)的話,那么 Zynq 的啟動流程到 FSBL 階段就足夠了。因此,SSBL 是面向于需要運行操作系統(tǒng)的應(yīng)用場合。相信熟悉操作系統(tǒng)啟動知識的朋友到這里應(yīng)該很清楚了,SSBL 就是操作系統(tǒng)在啟動過程中的引導(dǎo)程序 boot loader。對于 Linux 而言,Zynq 的 SSBL 階段和 u-boot 的作用是相同的。具體來說,SSBL 的作用就是將 Zynq 所需要的操作系統(tǒng)加載到 DDR 內(nèi)存之中。

到此,Zynq 的啟動與配置就算完成了。Zynq 啟動過程其實與傳統(tǒng)的 ARM 開發(fā)過程類似,區(qū)別就在于它是PS + PL 的架構(gòu),所以在啟動過程中,額外需要加載二進制 bit 流文件。Xilinx 將 Zynq 的啟動劃分為3個階段,從結(jié)構(gòu)上看也是科學(xué)合理的。

總結(jié)

本文主要與大家分享了 Zynq 在非 JTAG 模式下的啟動配置流程,旨在讓大家對 Zynq 的三階段啟動模式有一個具體的認(rèn)識,希望大家多多交流。

-

JTAG

+關(guān)注

關(guān)注

6文章

403瀏覽量

72882 -

存儲設(shè)備

+關(guān)注

關(guān)注

0文章

166瀏覽量

19129 -

Zynq

+關(guān)注

關(guān)注

10文章

614瀏覽量

47997

原文標(biāo)題:zynq配置成jtag模式,啟動與配置過程詳解

文章出處:【微信號:ZYNQ,微信公眾號:ZYNQ】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

淺談ZYNQ的三種啟動方式-JTAG、SD card、Flash

詳解Zynq的兩種啟動模式

通過JTAG啟動Linux的方法和腳本

【Z-turn Board試用體驗】+Zynq7000啟動流程介紹

JTAG如何允許我在任何啟動模式下編程QSPI?

詳細解讀Zynq的三種啟動方式(JTAG,SD,QSPI)

FPGA JTAG的配置模式詳細說明

Zynq 在非 JTAG 模式下的啟動配置流程

評論