數字硬件建模SystemVerilog-決策語句-if-else語句

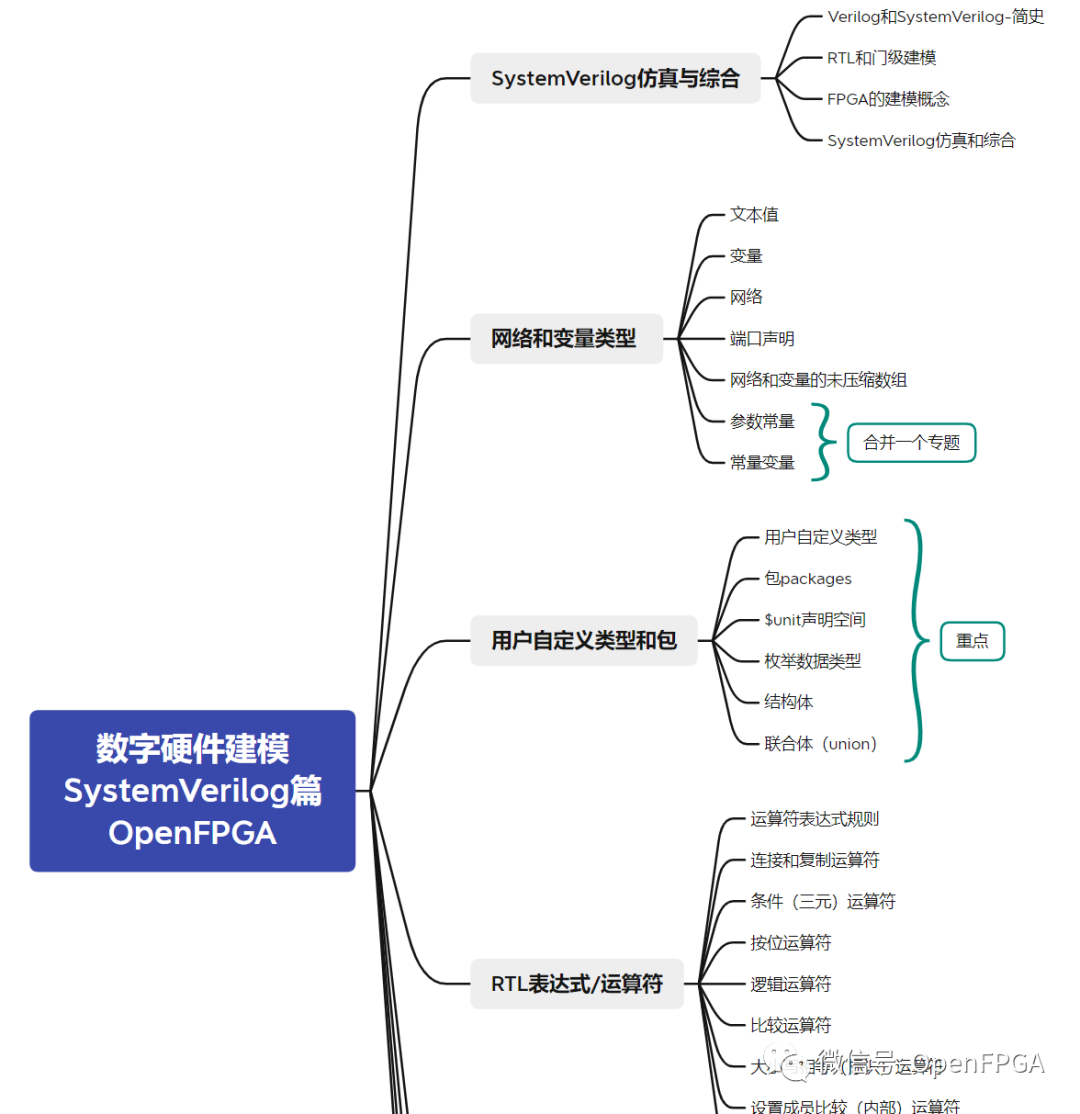

經過幾周的更新,SV核心部分用戶自定義類型和包內容已更新完畢,接下來就是RTL表達式和運算符。

馬上HDLBits-SystemVerilog版本也開始準備了,基本這一部分完成后就開始更新~

決策語句(Decision statements)允許程序塊的執行流程根據設計中信號的當前值分支到特定語句。SystemVerilog有兩個主要的決策語句:if…else語句和case語句,使用關鍵字case、case…inside,casex和casez。

介紹

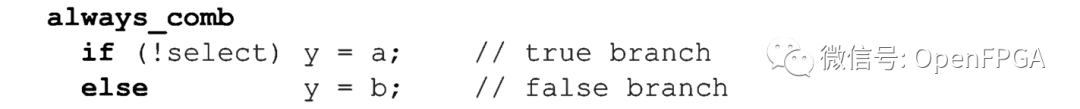

if-else語句對表達式求值并執行兩個可能的分支之一,即true分支或false分支。

if-else表達式可以是任何向量大小的網絡或變量,也可以是運算的返回值,如果表達式的一個或多個位設置為l,則向量表達式的計算結果為true。如果表達式的所有位均為0,則表達式的計算結果為false。例如:

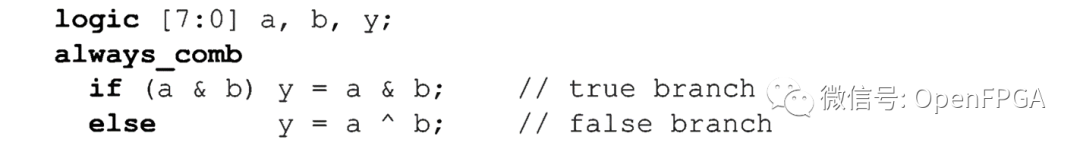

a和b的按位AND運算的結果是8位向量(因為a和b都是8位向量)。如果AND操作導致任何位置1,那么將執行true分支。如果邏輯AND的結果為零,則將執行false分支,

| 最佳實踐指南6-1 |

|---|

| 對于if-else條件表達式,盡量只使用1位值或返回true/false操作。不要將向量用作if-else表達式。 |

之前的文章也詳細介紹了返回true/false結果的運算符。

不要對向量進行true/false測試。評估向量為true/false可能會導致設計錯誤。在前面的示例中,編寫代碼的工程師打算測試(a & b)的true/false,但是它是8位向量值,它并不是true/false邏輯運算的1位結果。對于a和b的某些值,if-else決策執行的哪個分支可能不同,通過遵循僅使用標量(1位)值或返回具有true/false結果的操作的指南,可以避免這種模糊性和可能的編碼錯誤。

對于4狀態值,表達式可能既不是真的也不是假的,如值8’b0000000z。一個既不正確也不錯誤的表達被認為是未知的。當if-else決策的表達式計算為未知時,將執行false分支。這可能會導致RTL模型的仿真方式以及綜合后門級模型的實際行為不匹配。后面我們會討論關于SystemVerilog模型中的X-optimism 和 X-pessimism對這種情況進行了討論。

if-else決策的每個分支可以是一條語句,也可以是一組包含在begin和end之間的語句,如下面的代碼段所示,

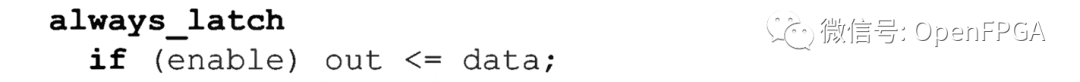

沒有else分支的if語句。if-else決策的else(false)分支是可選的。如果沒有else分支,且表達式的計算結果為false(或unknown),則不執行任何語句。在下面的代碼段中,如果enable為0,則out不會更改。由于out是一個變量,它保留了以前的值,仿真時會產生鎖存器行為。

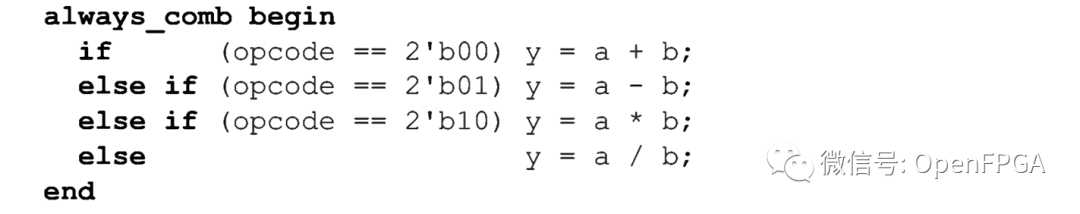

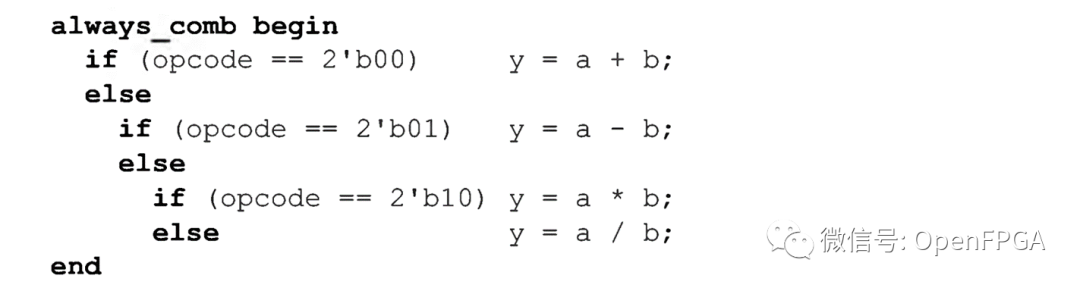

If-else-if。多個判斷語句可以由一系列if-else語句組成,如下面的代碼片段所示。

請注意,SystemVerilog不像某些編程語言那樣具有elsif關鍵字。決策鏈由包含嵌套if-else語句的每個else分支組成。當上面的代碼段使用不同的縮進編碼時,這種嵌套更為明顯,如下所示。

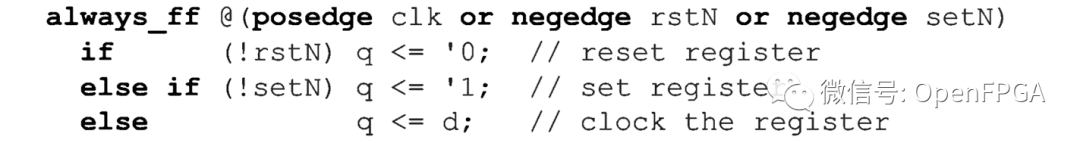

一系列if-else-if決策按照語句的列出時序進行評估。這將優先考慮首先列出的判斷條件。下面的示例演示了一個可以set和reset的觸發器。如果set和reset同時激活,reset具有優先級,因為它是在一系列決策中首先進行判斷的。本例中的set和reset為低電平有效信號。

(該set和reset觸發器示例存在潛在的仿真故障,后面我們再對此進行討論。)

綜合if-else語句。綜合編譯器實現if-else語句的方式取決于決策語句的上下文以及目標ASIC或FPGA中可用的組件類型。一般規則是:

組合邏輯中的if-else語句表現為多路復用器,通常在門級實現中實現為多路復用器。

如果沒有其他語句分配給同一個變量,則組合邏輯中沒有else的if將充當鎖存器,這是因為分配的變量保留其先前的值。綜合器通常將這種存儲效果作為鎖存器來實現,

組合邏輯中的if-else-if語句系列使用優先級編碼行為進行仿真,其中每個if語句優先于該系列中的任何后續if語句。如果所有決策表達式都是互斥的(兩個或多個表達式不可能同時為真),則綜合編譯器將刪除優先級編碼。

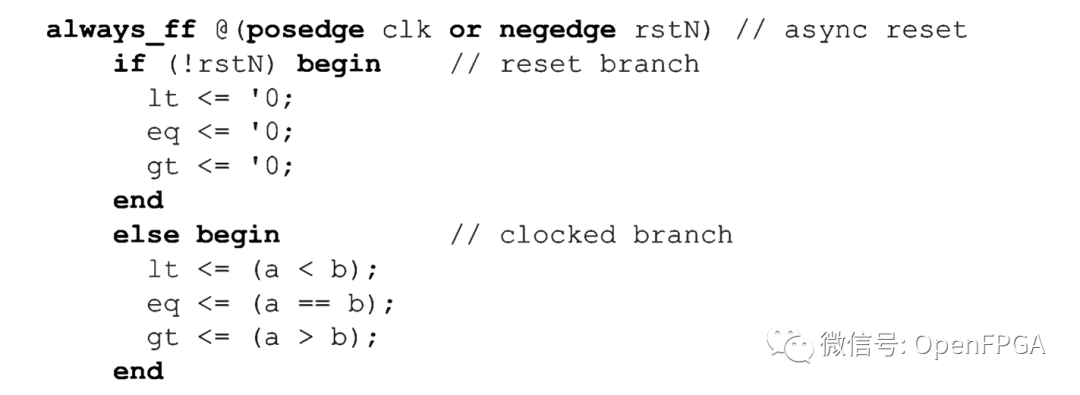

在時鐘邊沿評估的if-else語句表現為觸發器,并將在門級實現中綜合為某種類型的寄存器。

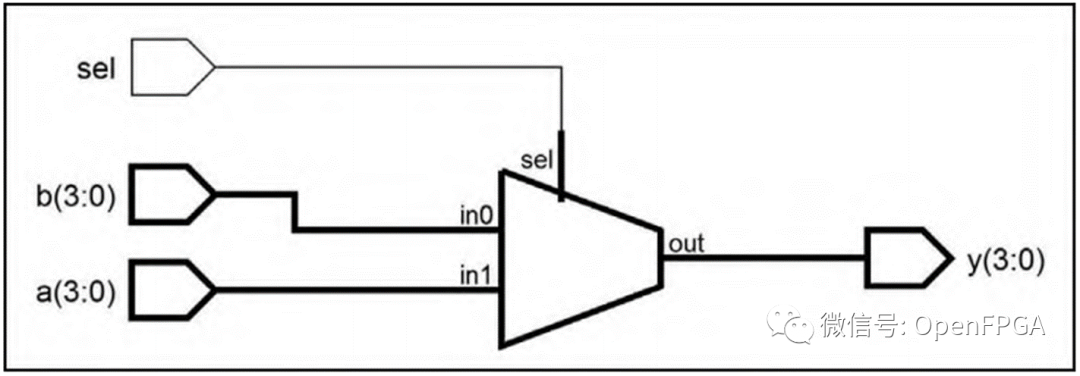

使用if-else作為多路復用器。圖6-1中的示例6-1及其附帶的綜合結果顯示了,綜合器會在多路復用器的上下文中判斷是否使用了else。

示例6-1:使用if-else對多路復用器功能進行建模

`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulemux2to1 #(parameterN=4)//bussize (inputlogicsel,//1-bitinput inputlogic[N-1:0]a,b,//scalableinputsize outputlogic[N-1:0]y//scalableoutputsize ); timeunit1ns;timeprecision1ns; always_combbegin if(sel)y=a; elsey=b; end endmodule:mux2to1 `end_keywords圖6-1:示例6-1的綜合結果:作為MUX的if-else

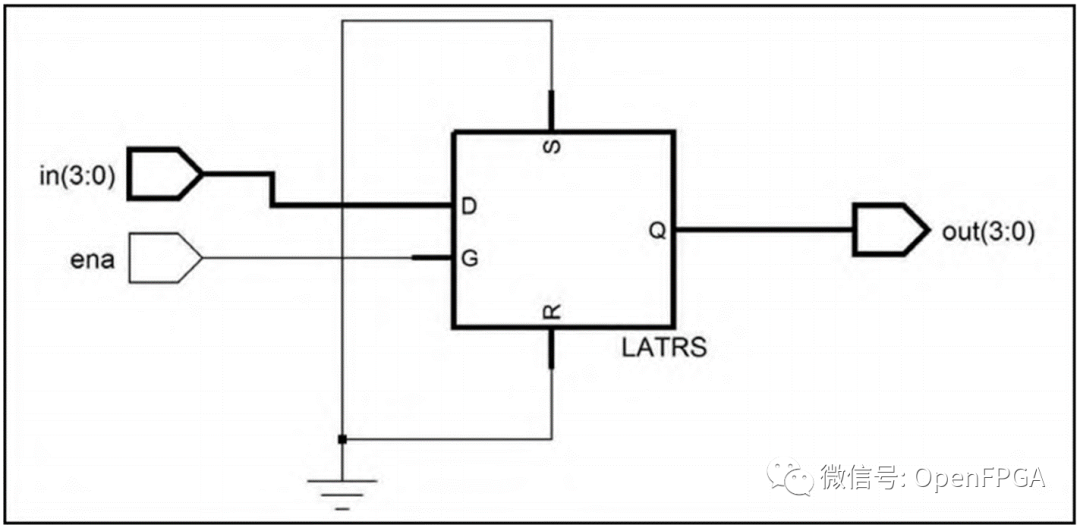

使用if-else作為鎖存器。示例6-2顯示了表示鎖存器的if語句。

示例6-2:使用if不適用else來仿真鎖存器功能

`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulelatch #(parameterN=4)//bussize (inputlogicena,//1-bitinput inputlogic[N-1:0]in,//scalableinputsize outputlogic[N-1:0]out//scalableoutputsize ); timeunit1ns;timeprecision1ns; always_latchbegin if(ena)out<=?in;? ??end endmodule:?latch `end_keywords圖6-2:示例6-2的綜合結果:if-else作為鎖存器

用于生成圖6-2的綜合編譯器將RTL功能轉換為具有未使用的set和reset輸入的通用鎖存器。最終實現中使用的鎖存器的具體類型將取決于目標ASIC或FPGA中可用的鎖存器類型。

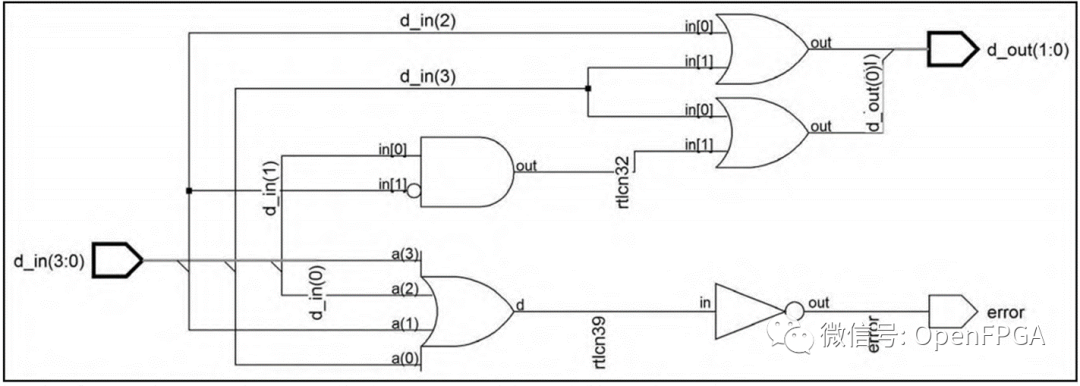

使用if-else作為優先級編碼器。示例6-3說明了4對2優先級編碼器中的if-else-if。

示例6-3:使用if else if系列對優先級編碼器建模

`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulepriority_4to2_encoder( inputlogic[3:0]d_in, outputlogic[1:0]d_out, outputlogicerror ); timeunit1ns;timeprecision1ns; always_combbegin error='0; if(d_in[3])d_out=2'h3;//bit3isset elseif(d_in[2])d_out=2'h2;//bit2isset elseif(d_in[1])d_out=2'h1;//bit1isset elseif(d_in[0])d_out=2'h0;//bit0isset elsebegin//nobitsset d_out=2'b0; error='1; end end endmodule:priority_4to2_encoder `end_keywords

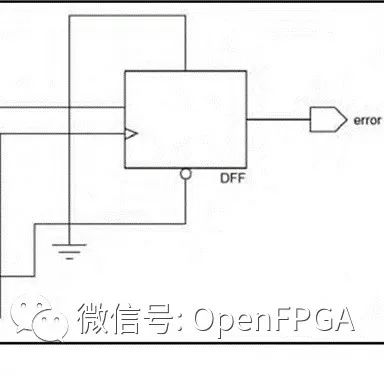

圖6-3;示例6-3的綜合結果:if-else作為優先編碼器

圖6-3;示例6-3的綜合結果:if-else作為優先編碼器

圖6-3中的“優先級編碼”被綜合為一系列邏輯門,其中一級的輸出成為“序列中下一級”的輸入,而不是并行編碼d_in的所有位。“該串行數據路徑”是“if-else-if”系列中計算d_in數據位的優先級的結果。

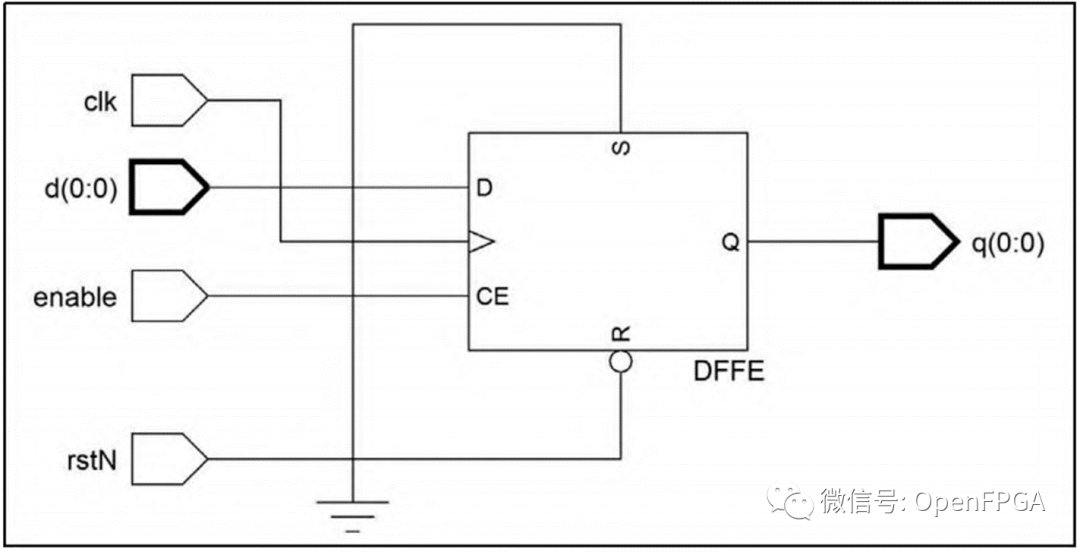

使用if-else作為觸發器。示例6-4顯示了帶有復位和芯片使能(也稱為負載使能或數據使能)輸入的時序邏輯觸發器中的if-else-if。因為復位輸入是首先評估的,所以它的優先級高于使能輸入,圖6-4顯示了綜合這個if-else-if決策序列的結果。

例6-4;使用if-else-if系列為帶復位和芯片使能的觸發器建模

moduleenable_ff #(parameterN=1)//bussize (inputlogicclk,//posedgetriggeredclk inputlogicrstN,//activelowasyncreset inputlogicenable,//activehighchipenable inputlogic[N-1:0]d,//scalableinputsize outputlogic[N-1:0]q//scalableoutputsize ); timeunit1ns;timeprecision1ns; always_ff@(posedgeclkornegedgerstN)//asyncreset if(!rstN)q<=?'0;??????????????//?active-low?reset ???else?if?(enable)?q?<=?d;???????????????//?store?if?enabled endmodule:?enable_ff

圖6-4:示例6-4的綜合結果:if-else作為芯片啟用觸發器

圖6-4:示例6-4的綜合結果:if-else作為芯片啟用觸發器

圖6-4顯示了綜合如何將帶低電平復位和使能的芯片觸發器映射到通用組件。該過程的下一步是綜合編譯器將該通用組件映射到目標ASIC或FPGA設備中可用的特定類型的觸發器,如果該目標設備沒有芯片使能觸發器,則綜合將在觸發器之外添加多路復用器功能,以模擬芯片使能行為,如果觸發器使能,多路復用器將把新的數據值傳遞給D輸入,并將觸發器Q輸出反饋給D輸入。如果觸發器未使能,則輸入。以類似的方式,如果目標設備沒有具有異步低電平有效的復位的觸發器,則綜合編譯器將在觸發器之外添加功能,以模擬這種行為,后面再討論具有各種復位類型的建模和綜合觸發器。

SystemVerilog-程序塊 (procedural blocks)

-

硬件

+關注

關注

11文章

3315瀏覽量

66203 -

編碼

+關注

關注

6文章

942瀏覽量

54814 -

RTL

+關注

關注

1文章

385瀏覽量

59763 -

運算符

+關注

關注

0文章

172瀏覽量

11081

原文標題:SystemVerilog-決策語句-if-else語句

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于運算符信息的數學表達式檢索技術

RTL表達式和運算符

RTL表達式和運算符

評論