前幾天,看到一個(gè)比喻,說鎖相環(huán)是一個(gè)電路的心臟,沒有它,整個(gè)電路都工作不了了。

想想也是,沒有鎖相環(huán),混頻器沒法變頻,ADC沒法采樣,確實(shí)很重要。

實(shí)際的PLL電路肯定相當(dāng)復(fù)雜,不過,可以從簡單的看起。

一個(gè)最最簡單的PLL,有三部分組成,VCO,鑒相器(PD)和低通濾波器。

這篇文章呢,就先講講鑒相器的原理。

鑒相器(Phase Detector/PD)

鑒相器,英文名為Phase Detector,簡稱PD。

Phase Detector直譯過來為相位檢測(cè)器,讀上去好像比鑒相器通俗一點(diǎn)哦。

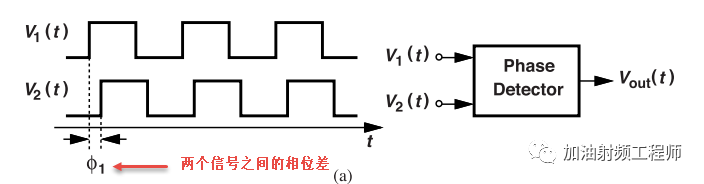

相位檢測(cè)器,就如其字面意思,就是檢測(cè)相位用的。不過呢,它是對(duì)兩個(gè)信號(hào)的相位差做出反應(yīng)。也就是說,它不管你相位的絕對(duì)值,它是比較兩個(gè)相位的相對(duì)值。相位檢測(cè)器的輸出呢,一般是一個(gè)電壓,而且這個(gè)電壓與相位差呈線性關(guān)系。如下圖所示。

它的主要工作時(shí)用來測(cè)量兩個(gè)信號(hào)之間的相位差,然后輸出一個(gè)參量,比如說電壓。而這個(gè)電壓與相位差呈線性關(guān)系。

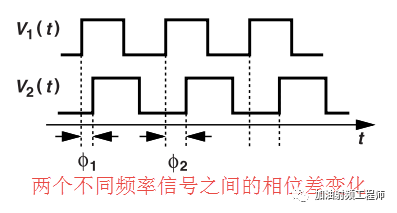

如果V1(t)和V2(t)的頻率不相等的話,兩者的相位差則會(huì)隨時(shí)間發(fā)生變化。如下圖所示。

PD怎么實(shí)現(xiàn)呢?

那上述的功能怎么用電路實(shí)現(xiàn)出來呢?

異或門

或許你想不到,一個(gè)簡單的異或門(XOR)就可以實(shí)現(xiàn)上面的功能。當(dāng)然,實(shí)際電路可能比這個(gè)復(fù)雜,這個(gè)等我了解到了,再談。

目前,先從原理層面上看看。

異或門的真值表如下:

換成文字描述就是:當(dāng)兩個(gè)輸入相同時(shí),輸出為0;當(dāng)兩個(gè)輸入不同時(shí),輸出為1.

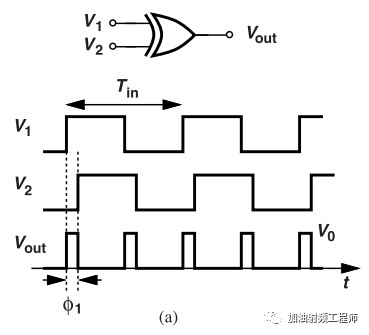

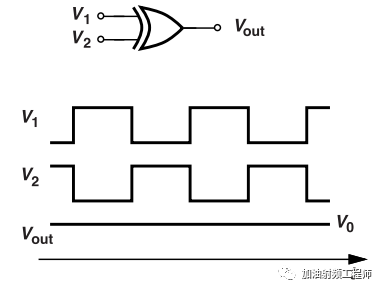

異或門當(dāng)做PD來使用時(shí),其工作原理如下圖所示。

如上圖所示,兩個(gè)方波信號(hào)V1和V2,而V2的相位比V1滯后,即V2的變化沿要比V1的來的晚一點(diǎn)。

在一個(gè)周期內(nèi),V1和V2會(huì)有一段時(shí)間,電平不一致。

當(dāng)V1和V2經(jīng)過異或門時(shí),兩者電平不同時(shí),異或門輸出高;當(dāng)兩者電平相同時(shí),異或門輸出低。這樣,異或門就將V1和V2的相位差,與電壓輸出連接起來了。

輸出Vout是一系列的脈沖信號(hào),因?yàn)樯仙靥幰咭淮危陆笛靥幰咭淮危栽撁}沖信號(hào)的頻率是輸入信號(hào)的2倍。

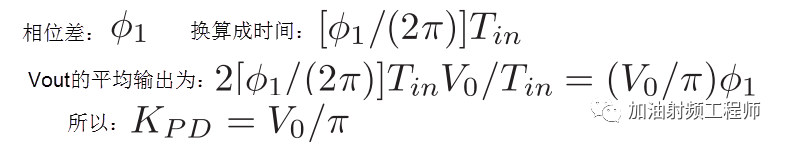

脈沖寬度與信號(hào)之間相位差的大小成正比關(guān)系,也就是說,相位差大,脈沖寬;相位差小,脈沖窄。

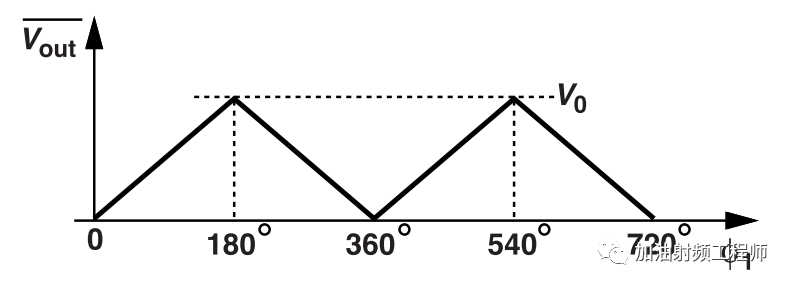

脈沖信號(hào)的平均值如下圖所示,與相位差線性相關(guān)。

當(dāng)V1和V2相差180度時(shí),這時(shí)Vout的輸出恒定為1, 此時(shí)Vout的平均值最大。

當(dāng)V1和V2的相位差超過180度時(shí),Vout的平均值開始線性下降。

因此,當(dāng)XOR作為PD時(shí),其輸入輸出的特性曲線如下圖所示。

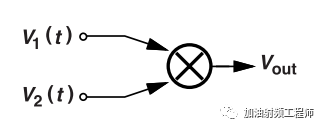

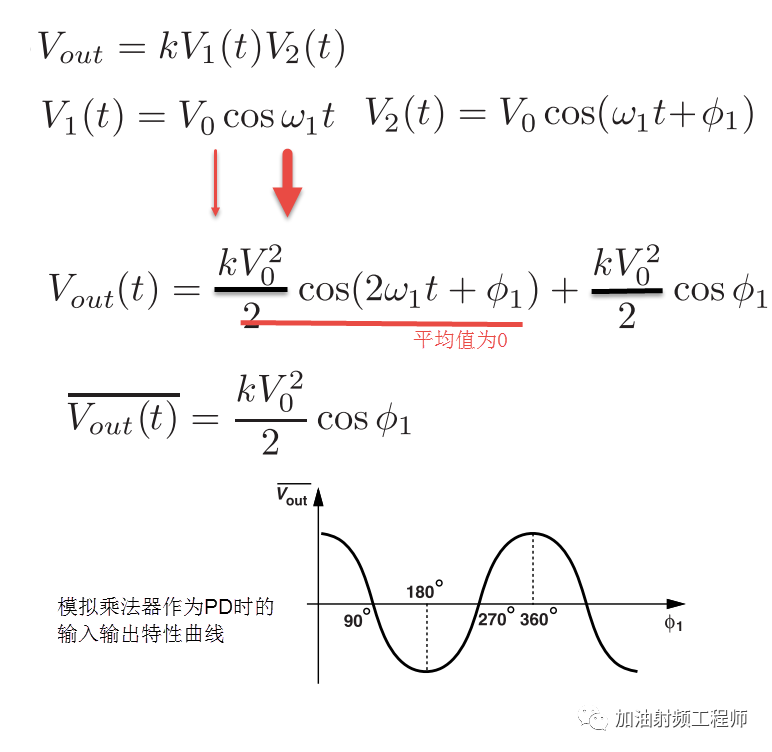

另外,模擬乘法器(或者混頻器),也可當(dāng)成PD來使用。想不到吧?

其輸入輸出特性曲線如下圖所示。

審核編輯:湯梓紅

-

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

584瀏覽量

87742 -

adc

+關(guān)注

關(guān)注

98文章

6496瀏覽量

544474 -

鑒相器

+關(guān)注

關(guān)注

1文章

60瀏覽量

23276

原文標(biāo)題:鎖相環(huán)中的鑒相器了解不?

文章出處:【微信號(hào):加油射頻工程師,微信公眾號(hào):加油射頻工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

鑒頻鑒相器的指標(biāo)對(duì)鎖相環(huán)死區(qū)及抖動(dòng)性能的影響

鎖相環(huán)和鑒相器的電路原理和結(jié)構(gòu)?

全數(shù)字鎖相環(huán)的設(shè)計(jì)及分析

mc1496用于鎖相環(huán)的鑒相器

鎖相環(huán)知識(shí)

請(qǐng)問ADF4153鑒相器的鑒相靈敏度是多少?

鎖相環(huán)控制頻率的原理

三角形取樣鑒相數(shù)字合成器鎖相環(huán)中的混沌

一種低噪聲雙鑒頻鑒相器的研究

集成鎖相環(huán)路原理特性及應(yīng)用

MAX9382在鎖相環(huán)中的應(yīng)用

數(shù)字鑒相器,數(shù)字鑒相器原理是什么?

鎖相環(huán)中YTO自校準(zhǔn)技術(shù)的應(yīng)用

鎖相環(huán)中的鑒相器了解不?

鎖相環(huán)中的鑒相器了解不?

評(píng)論