頻譜監(jiān)控已成為商業(yè)和國防應用的關鍵活動。

第 1 部分:

越來越多的技術正在使用前所未有的帶寬水平。盡管捕獲的數(shù)據(jù)有所增加,但通常最好收集盡可能多的頻譜。這給現(xiàn)代頻譜監(jiān)測解決方案帶來了一個重大問題。近乎實時地分析大量頻譜是計算密集型的。為了滿足頻譜監(jiān)測的動態(tài)捕獲和處理要求,軟件定義無線電(SDR)和外部數(shù)據(jù)處理系統(tǒng)已成為事實上的標準。高性能頻譜監(jiān)測需要仔細考慮系統(tǒng)架構,以防止系統(tǒng)瓶頸并實現(xiàn)有效的數(shù)據(jù)分析。在高層次上,無線電需要通過高速數(shù)據(jù)鏈路連接到數(shù)據(jù)處理系統(tǒng);最先進的SDR利用速度高達4x40 Gbps的無線電到主機連接,以完全實現(xiàn)寬帶監(jiān)控。

第2節(jié):

一旦數(shù)據(jù)從無線電卸載到處理系統(tǒng),就會出現(xiàn)各種瓶頸。通過網(wǎng)絡接口卡 (NIC) 引入數(shù)據(jù)可能會導致各種問題,首先是丟棄數(shù)據(jù)包。并非所有網(wǎng)卡都能夠處理多個 Gbps,即使它們通過 PCI 總線連接。一旦NIC過載,數(shù)據(jù)包將開始被丟棄,導致捕獲的數(shù)據(jù)丟失,這在頻譜監(jiān)控應用中是不可接受的。基于FPGA的NIC已經(jīng)開發(fā)出來解決這個問題,因為它們可以支持更高的吞吐量。傳統(tǒng) NIC 將通過總線以一對一的方式將數(shù)據(jù)包傳輸?shù)街骺刂破鳎@可能導致高吞吐量實例中的擁塞。如果使用傳統(tǒng) NIC 引入大量數(shù)據(jù),則由于無法預處理和聚合數(shù)據(jù)包,因此可能會丟棄數(shù)據(jù)包。基于 FPGA 的 NIC 可以 利用 預 處理 和 壓縮 來 減少 下游 處理 單元 (如 CPU 和 其他 FPGA) 的 攝取 工作量。

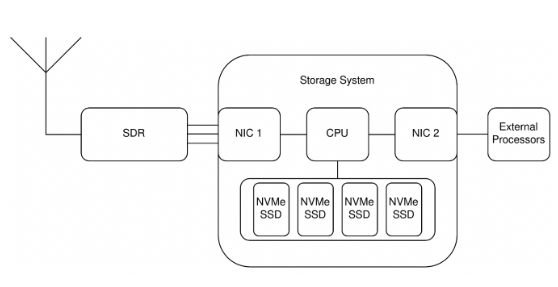

圖 1:典型的攝取硬件解決方案

第 3 部分:

數(shù)據(jù)被計算系統(tǒng)攝取后,需要對其進行存儲和處理。應仔細設計系統(tǒng)的體系結構,以最大限度地提高攝取率,同時最大限度地降低硬件成本。典型的硬件配置如圖1所示。實施扇出存儲架構是高通量頻譜監(jiān)測解決方案的理想選擇,因為它可以降低單個系統(tǒng)組件的性能要求。謹慎的做法是讓存儲系統(tǒng)利用環(huán)形緩沖區(qū)來提供最大的收集歷史記錄,同時自動丟棄最舊的數(shù)據(jù)。頻譜監(jiān)控存儲硬件的 HDD 與 SSD 的選擇既具體應用又成本相關。HDD的價格較低,寫入速度約為150 MBps,而PCI 4.0 SSD則更昂貴,但可以實現(xiàn)高達5,000 MBps的寫入速度。

具有較低數(shù)據(jù)捕獲和存儲要求的頻譜監(jiān)控解決方案可以利用 RAID 陣列中的 HDD。RAID 中的兩個硬盤將支持大約 2.4 Gbps 的攝取速率。這似乎很重要,但假設未存儲測量元數(shù)據(jù),則僅支持連續(xù)捕獲大約100 MHz的帶寬。捕獲 GHz 帶寬將需要將存儲寫入速度提高幾個數(shù)量級,因為許多頻譜監(jiān)控應用目前利用多個獨立的無線電接收器來提高性能和捕獲帶寬。為了滿足這一日益增長的需求,NVMe SSD是高性能頻譜監(jiān)控存儲的最佳解決方案。單個高性能 NVMe 固態(tài)硬盤可以取代 17 個硬盤 RAID,這意味著單個設備可以攝取超過 1600 MHz 的捕獲頻譜。雖然 SSD 比機械式 SSD 的性能顯著提高,但許多頻譜監(jiān)控解決方案仍需要 RAID 配置。要從最先進的 4x40 Gbps 網(wǎng)卡引入數(shù)據(jù),需要一個由四個高性能 SDD 組成的條帶陣列。

除了傳輸速度要求外,系統(tǒng)的計算能力還必須能夠滿足攝取和處理要求。隨著捕獲的頻譜量的增加,CPU和處理卡功能也隨之增加。高捕獲帶寬將需要分配多個 CPU 內核。存儲 160 Gbps 的數(shù)據(jù)需要大約 25 個 CPU 內核專用于攝取過程 [ntop]。建議使用分布式計算架構、板載 FPGA 和 GPU 或某種組合來處理這些數(shù)據(jù)的分析。除了 CPU 內核之外,在將數(shù)據(jù)寫入 RAID 陣列之前,還應分配幾 GB 的 RAM 來緩沖數(shù)據(jù)。對于 HDD 陣列,緩沖區(qū)大小應更大以補償寫入延遲,但對于基于 SSD 的存儲解決方案,可以減小其大小。

圖 2:數(shù)據(jù)包捕獲和處理數(shù)據(jù)流

第 4 部分:

基于SDR的頻譜監(jiān)測解決方案的一個顯著優(yōu)勢是它們提供了高水平的可重構性。由于硬件配置的可變性,捕獲的元數(shù)據(jù)在分析過程中至關重要。捕獲帶寬、載波頻率和溫度等參數(shù)可能會有很大差異,并且相關的元數(shù)據(jù)必須與頻譜數(shù)據(jù)一起存儲。眾多SDR供應商的存在及其獨特的數(shù)據(jù)包協(xié)議可能會使捕獲數(shù)據(jù)的分析復雜化。利用符合 VITA49 標準的 SDR 將提高 SDR 平臺數(shù)據(jù)之間的性能和一致性。符合 VITA49 標準的 SDR 數(shù)據(jù)會將捕獲的樣本與元數(shù)據(jù)隔離。元數(shù)據(jù)的分離減少了數(shù)據(jù)傳輸,因為符合VITA49標準的SDR僅在SDR看到變化時才發(fā)送元數(shù)據(jù)數(shù)據(jù)包,從而為頻譜捕獲數(shù)據(jù)留出更多空間。除了出色的元數(shù)據(jù)處理外,VITA49 還支持數(shù)據(jù)包的高精度時間戳和時序校正,以補償 RF 前端延遲,從而獲得更準確的元數(shù)據(jù) [IEEE]。

第 5 部分:

盡管在許多應用中變得越來越普遍,但目前可用的大多數(shù)SDR都無法滿足高性能寬帶頻譜監(jiān)測應用的要求。除了高通道帶寬外,許多頻譜監(jiān)測應用還需要多個獨立的接收鏈來實現(xiàn)空間信息提取。為了實現(xiàn)高帶寬捕獲和處理,無線電和早期處理系統(tǒng)需要通過高速數(shù)字回程緊密集成。嚴格的集成要求使交鑰匙 SDR 解決方案提供最佳性能,同時縮短硬件開發(fā)時間。由于數(shù)據(jù)攝取和處理要求可能非常嚴格,因此一些交鑰匙解決方案會將錄制、存儲和回放直接集成到解決方案中,以確保最佳性能。在查看本文中討論的高性能頻譜監(jiān)控要求時,與能夠提供完整解決方案的供應商合作非常重要。

審核編輯:郭婷

-

FPGA

+關注

關注

1629文章

21754瀏覽量

604236 -

控制器

+關注

關注

112文章

16396瀏覽量

178513 -

SDR

+關注

關注

7文章

233瀏覽量

50506

發(fā)布評論請先 登錄

相關推薦

選擇數(shù)據(jù)采集器時需要考慮的因素

?影響UVLED固化速率的多種因素

LORA模塊的數(shù)據(jù)傳輸速率

電磁頻譜管控系統(tǒng)

mos管的選型主要考慮哪些因素

天線PCB布局的設計考慮因素是什么?

電磁頻譜數(shù)據(jù)綜合管理平臺

電磁頻譜數(shù)據(jù)綜合管理系統(tǒng)

影響頻譜分析儀分辨率的因素解析

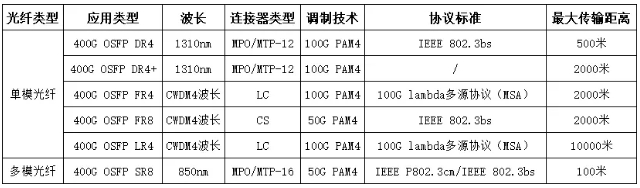

數(shù)據(jù)中心選擇光纖時的考慮因素

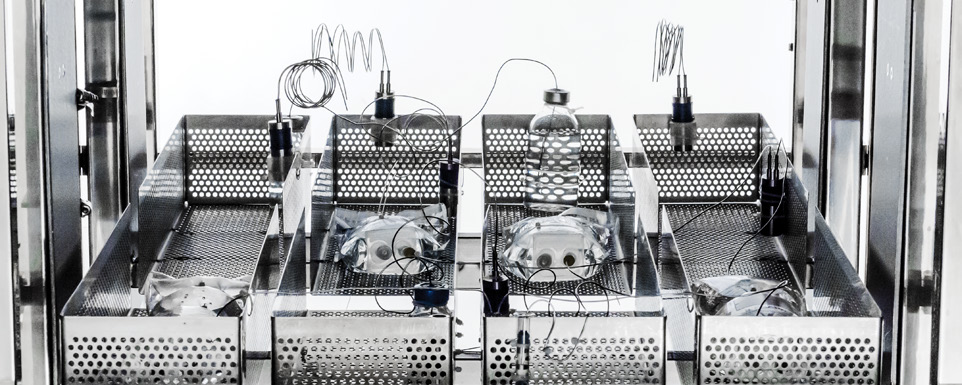

革新監(jiān)測技術:無線數(shù)據(jù)記錄系統(tǒng)如何顛覆食品、醫(yī)療和制藥行業(yè)的驗證流程

選擇ITX主板時要考慮的因素

頻譜監(jiān)測和記錄中SDR的高數(shù)據(jù)速率考慮因素

頻譜監(jiān)測和記錄中SDR的高數(shù)據(jù)速率考慮因素

評論