【摘要】

在某單板上,由于CPU芯片GMII接口的電源上只加了磁珠濾波,引起的故障:在網口通信時,當通信包的內容為低速碼型(全0全1)時,沒有丟包;當更改為偽隨機包時(碼型速率快),丟包嚴重。最終在磁珠后加電容,問題解決。

一、原因分析

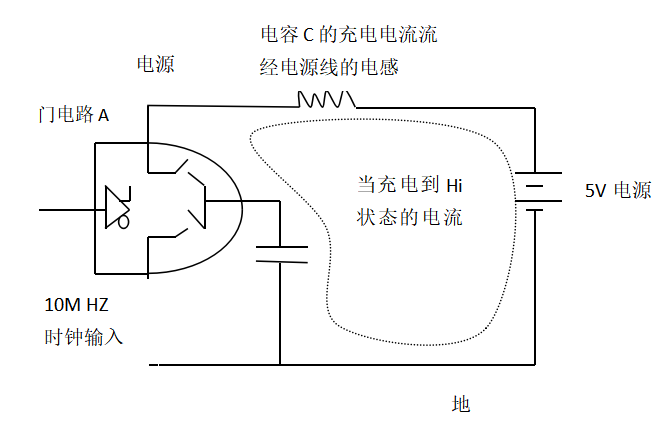

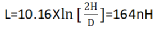

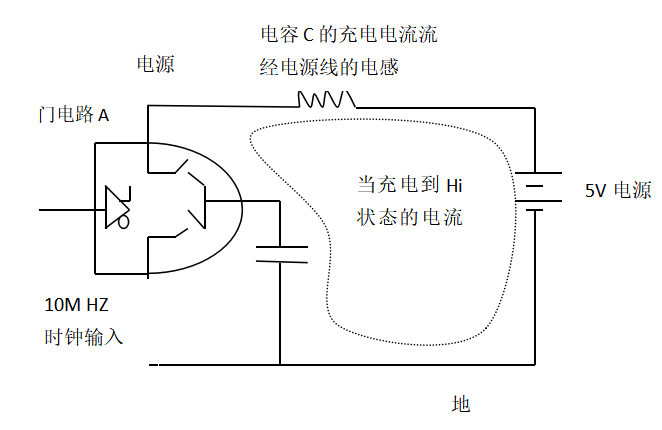

從電源的輸出到所供電的邏輯電路之間的引線可能包括值得重視的阻抗,這個阻抗導致了一個與工作電流成正比的壓降。其中,電源線上的電感產生的影響比電阻更嚴重。快速變化的電流(高速率碼型)通過電源線的電感引起電源和所供電的邏輯電路之間的電壓偏移。舉例說明一下布線電感問題有多糟糕。圖1的電路驅動一個大的容性負載。門電路A電源引腳的供電電流需求由每隔100ns的時鐘高電平組成。時鐘的高電平與門電路每次驅動容性負載為HI狀態時相對應。驅動HI狀態操作的電流路徑如虛線所示。

圖1 電源供電分配線的電感假設門電路的上升時間為5ns,則驅動器的最大dI/dt

其中,△V=5V(驅動電壓)

Tr10%-90%=5ns(驅動上升時間)C1=50pf(負載電容)

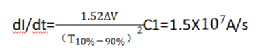

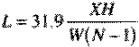

下一步,計算電源供電線路的電感:

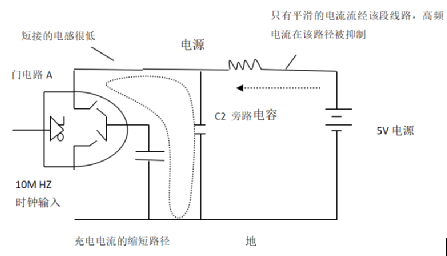

其中,X=10in(線路的長度) H=0.1in(線路之間的平均間距) D=0.04in L=電感/nH 最后得到噪聲電壓=(1.5X107)*(164*10-9)=2.5V噪聲真的這么大嗎?實際上,問題可能更嚴重。因為我們的假設并不精確。假設上升時間等于1ns,在這個電路中,電源供電電感非常大,以至于當門電路A試圖驅動Hi時,該電路板電源的供電輸入下降到接近零,隨著電容C1經過電源線電感的充電,電壓慢慢升起。當電源的供電下降的時候,門電路A在運行,或者進入振蕩狀態。 解決的辦法是加如圖2所示的旁路電容,如果電容C2的阻抗比電源的布線阻抗低,變化的電流將會流過電容而不是布線。當轉換為Hi狀態的時候,門電路A所經受的電源下降是C2阻抗的函數,而不是電源布線阻抗的函數。

圖2 旁路電容在電源線中平滑電流的流動

二、總結

1.電源在低頻時提供低的阻抗,局部的旁路電容在較高的頻率上提供低的阻抗;

2.對于可調電源輸出(包含反饋端),反饋端會為電源提供在分配線遠端測量到的電壓,然后電源就能通過調整輸出來適應布線引起的阻抗,而通常我們布線時,反饋電阻是放在電源近端的;

3.旁路電容要靠近管腳放置。

審核編輯:湯梓紅

-

電源

+關注

關注

185文章

18385瀏覽量

256587 -

cpu

+關注

關注

68文章

11090瀏覽量

217327 -

電感

+關注

關注

54文章

6210瀏覽量

104382

發布評論請先 登錄

如何消除電源走線引起的引線電感影響?

PCB板蛇形走線的作用

電源引線過長,寄生電感導致的電路振蕩現象

pcb蛇形走線

計算機組裝電源線排,主機箱背部走線技巧 組裝電腦走背線與理線教程

【干貨】如何消除電源走線引起的引線電感影響

【干貨】如何消除電源走線引起的引線電感影響

評論