時序約束中的

set_input_delay/set_output_delay約束一直是一個難點,無論是概念、約束值的計算,還是最終的路徑分析,每一次都要費一番腦子。Vivado為方便用戶創建輸入輸出接口的約束,整理出了一套非常實用的InputDelay/Output Delay Constraints Language Templates。只需根據接口信號的特征匹配到對應的template分類,就可以輕松套用模板中的公式創建約束。

本文將通過3個例子來展示,如何精確找到匹配的template。

01Input Delay/Output Delay Constraints Language Template

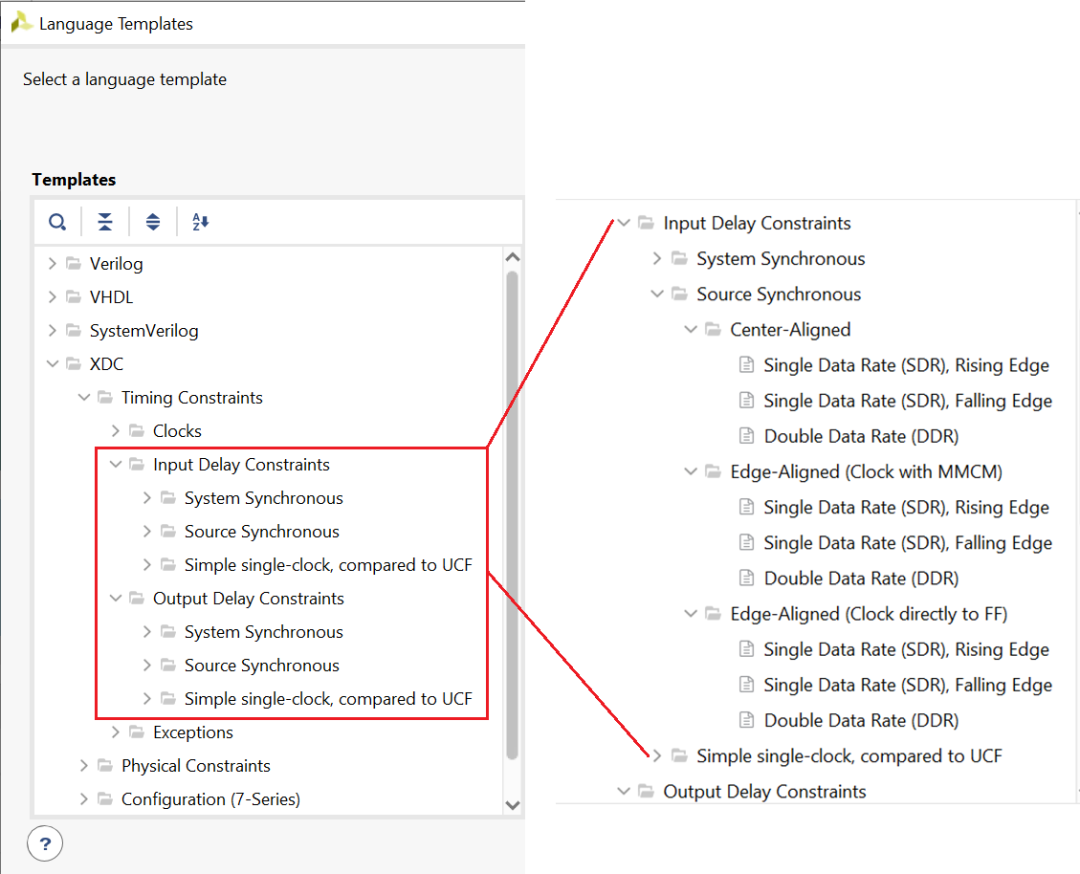

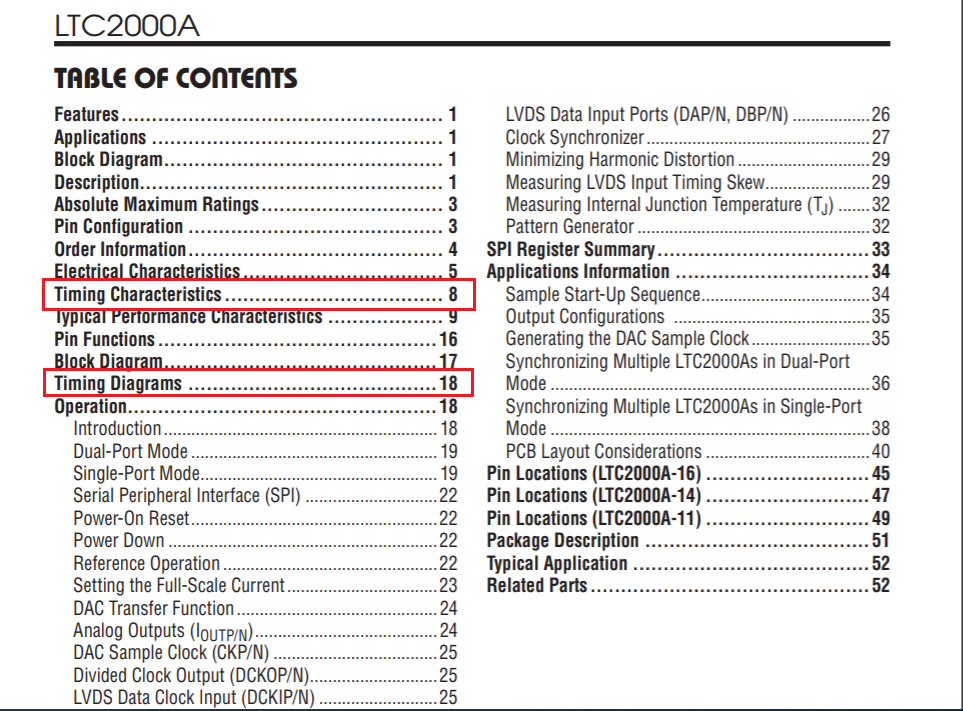

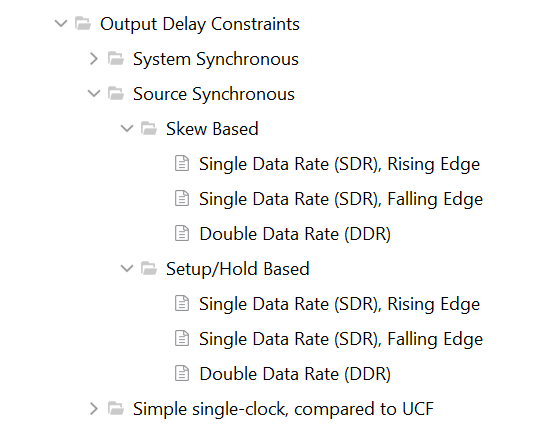

首先來介紹下Vivado的language Template。在Vivado GUI界面下,Tools菜單里即可打開Language Template。下圖紅框部分即InputDelay/Output Delay Constraints部分的模板

02模板分類目錄中的關鍵字

1. System Synchronous(系統同步)和Source Synchronous(源同步)

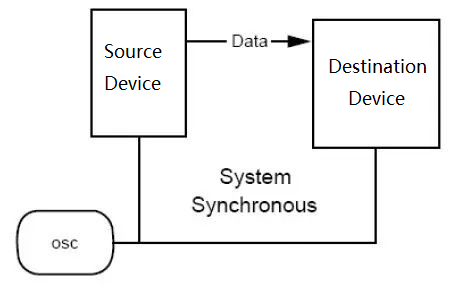

System Synchronous:兩個 device 之間進行通信時,使用一個共用時鐘,用于數據發送和接收。

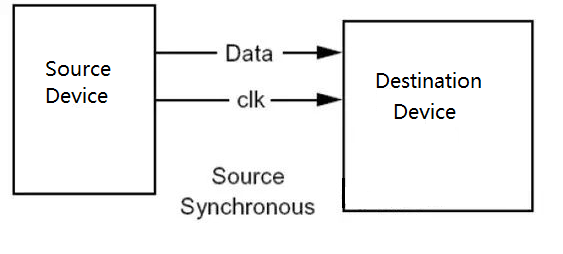

Source Synchronous:兩個 device 間進行通信時,發送端生成一個伴隨發送數據的時鐘信號。接收端利用該隨路時鐘進行數據接收。

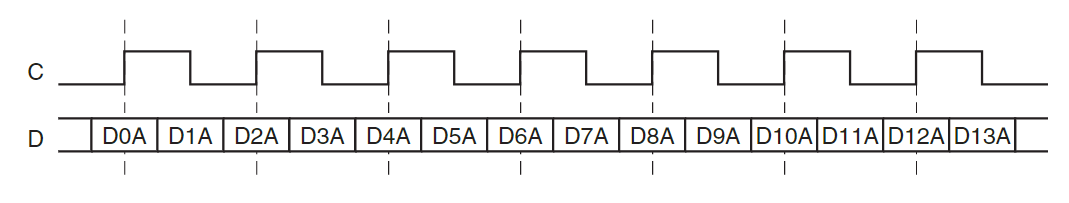

SDR:singledata rate。一個時鐘周期只傳輸一個 data。

DDR:doubledata rate。一個時鐘周期傳輸兩個 data。

3. Center-Aligned 和 Edge-Aligned

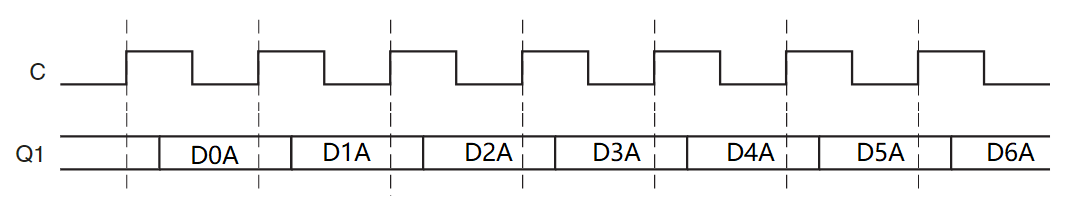

Center-Aligned 中心對齊,指時鐘的采樣沿 (capture edge) 處于對應數據有效窗口的中心位置附近。

Edge-Aligned 邊沿對齊,指時鐘的采樣沿處于對應數據的起始或結束位置附近.

03Template的內容

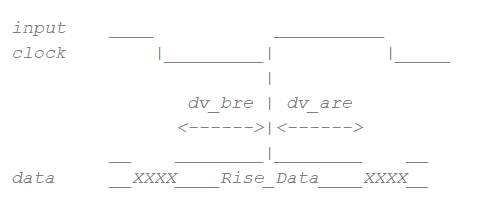

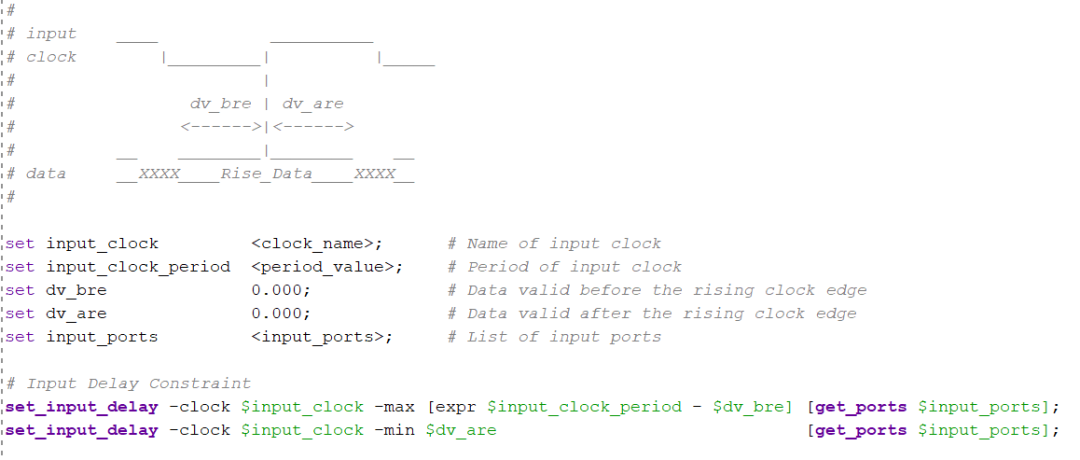

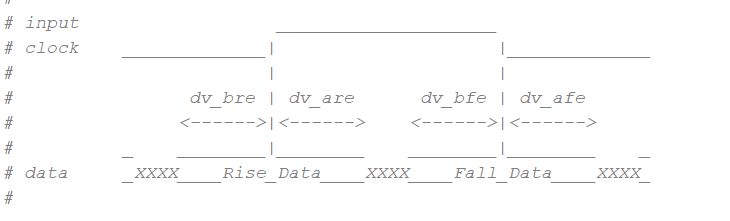

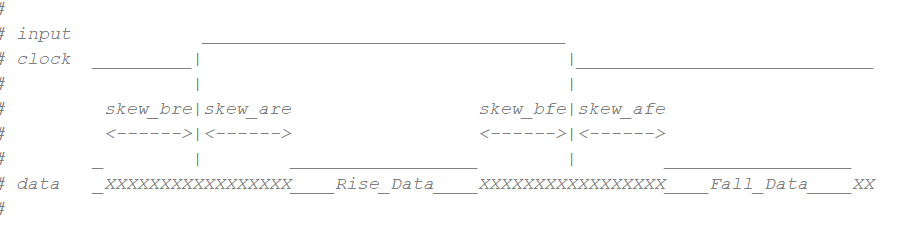

我們以"InputDelay Constraints -> Source Synchronous -> Center-Aligned -> SDR, Rising Edge"模板為例,看看模板的具體內容。

每個模板開頭都有個波形圖,描述這個模板對應的接口 data 與 clock 之間的時序關系。后面我們會講,這個時序圖將是精準匹配模板的關鍵。

波形圖里標示的參數 dv_bre,dv_are,是用來代入約束模板里面的公式計算 -max 和 -min 的約束值。因此匹配了正確的模板,確定了波形圖里的參數值,就可以套用公式完成約束的創建。

04匹配模板的法寶 - 波形圖

那么問題來了,去哪里找接口信號的波形圖?

模板里用來計算的參數如何確定呢?

答案: 對端器件的 Datasheet

Inputdelay 和 output delay 約束提供給 Vivado工具的信息,是 FPGA 外部電路上的時序數據。這部分數據跟 FPGA 內部電路上的時序信息(這部分工具已知)相結合才能完整地分析整條路徑是否滿足終點器件的建立時間和保持時間。

Inputdelay 約束的創建依賴 FPGA 上游器件的 Datasheet;Output delay 約束的創建依賴下游器件的 Datasheet。

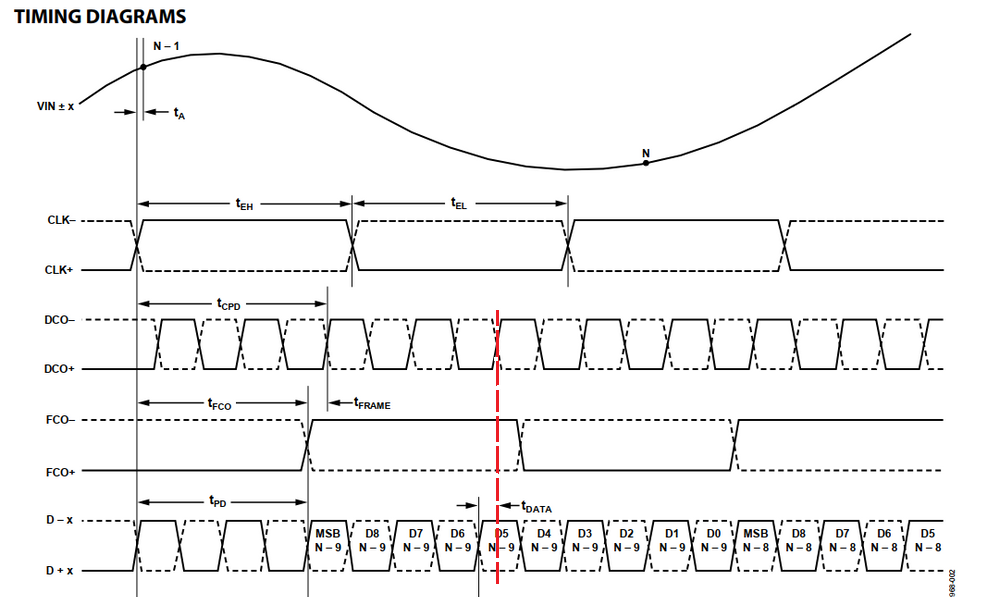

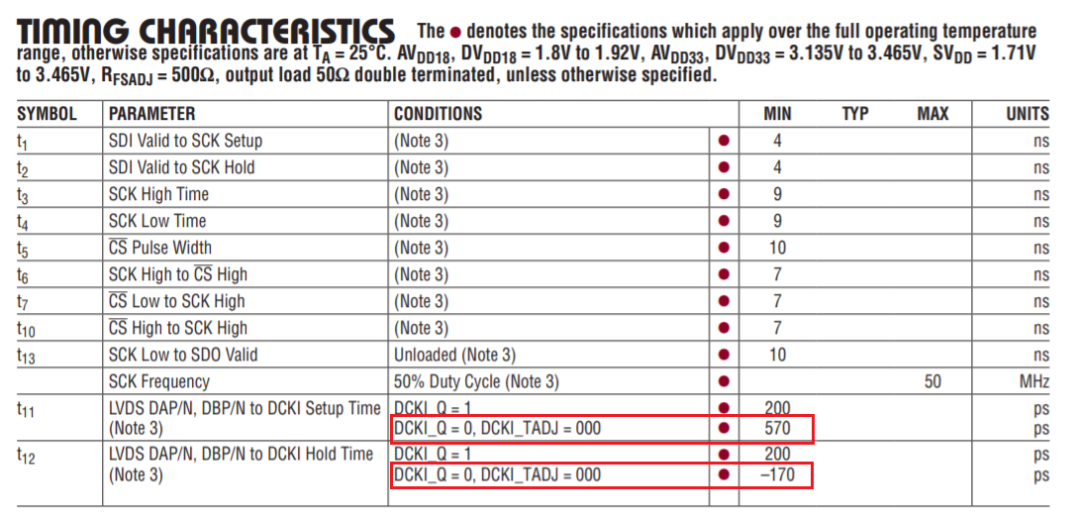

我們以 LTC2000A-11 DAC 器件的 Datasheet 為例:https://www.analog.com/media/en/technical-documentation/data-sheets/2000afb.pdf

我們需要的波形圖通常在 Datasheet 的 Timing Diagram 部分,而用來計算的參數通常在Timing Characteristics 部分。

對于前面講解的模板的三種分類目錄,SystemSynchronous/Source Synchronous 以及SDR/DDR 的區分相對容易,而 Center-Aligned 和 Edge-Aligned 如何得知呢?

這就依賴于對端器件的 Datasheet 中的 Timing 波形圖。

我們來看幾個例子:

例一:

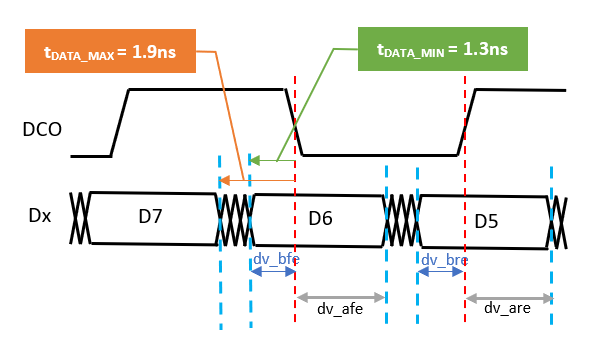

這是一個 SourceSynchronous 的 DDR 接口,需要約束 Dx 數據的 inputdelay,時鐘為DCO。下圖為上游器件 Datasheet 中的TimingDiagram,其中tDATA的范圍是1.3ns~1.9ns。

從圖中可以看出時鐘采樣沿大致在 Data 的中心,因此是 Center-Aligned。那么這個數據接口符合 SourceSynchronous --> Center-Aligned --> DDR 模板。

這個模板需要 dv_bre 等4個參數,如何確定呢?我們只需將 Datasheet 里的原波形圖做一點細化改動,就可以與模板里的波形圖完美匹配了。

tDATA之所以是一個范圍值,就是因為 data 是有“有效數據”(datavalid)和“無效數據”(陰影部分)窗口的。把原波形圖畫出陰影部分就一目了然了。

因此,

dv_bfe = dv_bre = tDATA_MIN = 1.3ns

dv_afe = dv_are = tDATA_MAX = (? Period – 1.9)ns

例二、

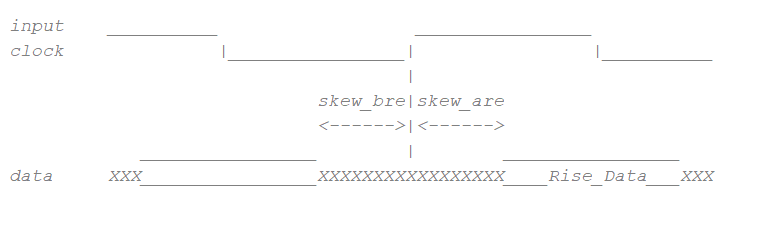

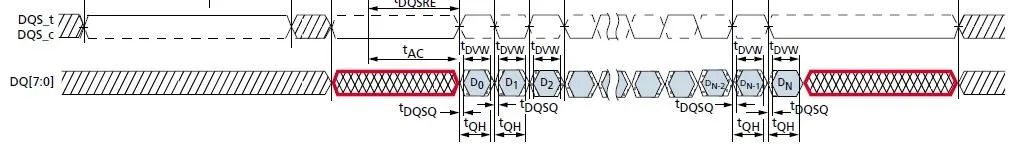

從下面這個 Datasheet 里的波形圖可以看出,這是一個 SourceSynchronous Edge-Aligned DDR 接口,需要創建 DQ 的 input delay 約束,時鐘是 DQS

這個例子比較直觀,直接匹配 SourceSynchronous ->Edge-Aligned -> DDR 模板

其中

skew_bre = skew_bfe = ? Period - tQH

skew_are = skew_afe = tDQSQ

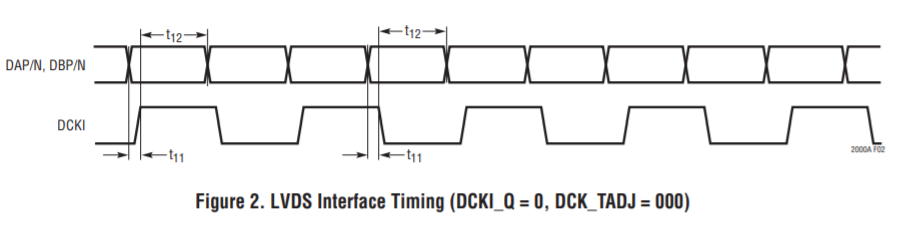

例三、

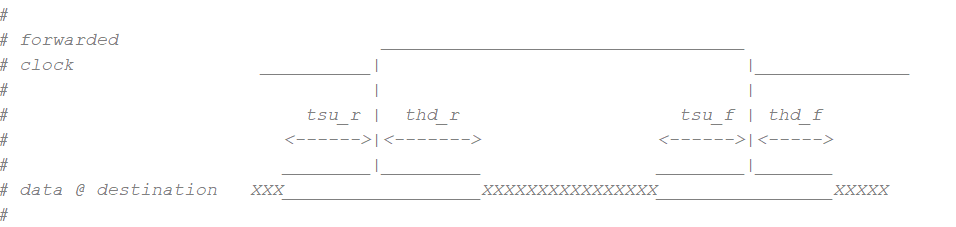

這個例子也是 SourceSynchronous,是從前面的 LTC2000A-11DAC 器件的 Datasheet 中提取出來的,需要創建 DAP/N的outputdelay 約束,隨路時鐘是DCKI。其中t11參數為0.057ns,t12參數為-0.017ns

Output delay 模板的分類不同于 Inputdelay,分為 Skew Based 和 Setup/HoldBased。仔細分析模板內容不難看出,兩者之間的差別是看對端器件 Datasheet 里提供的數據與時鐘之間關系的參數值是 Skew 形式還是 Setup/Hold 形式

本例中t11,t12是Setup/Hold值,因此匹配 SourceSynchronous -> Setup/Hold Based -> DDR 模板。

其中

tsu_r = tsu_f = t11

thd_r = thd_f = t12

希望通過這三個例子,能夠幫助大家找到使用模板創建輸入輸出接口時序約束的竅門。

審核編輯 :李倩

-

接口

+關注

關注

33文章

8650瀏覽量

151434 -

模板

+關注

關注

0文章

108瀏覽量

20579 -

時序

+關注

關注

5文章

389瀏覽量

37360

原文標題:運用 Language Template 來創建set_input_delay/set_output_delay約束

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

西門子PLC輸入輸出接線全攻略

評論